Disponible - Web Laboratori d`Electrònica - ETSETB

Anuncio

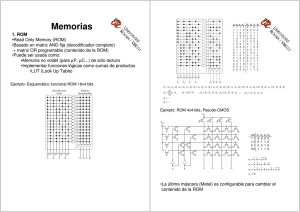

Disseny Microelectrònic I 11 de gener de 2013 Data notes provisionals: 18 de gener Període d’al·legacions: fins al 22 de gener Data notes revisades: 24 de gener DEPARTAMENT D’ENGINYERIA ELECTRÒNICA Professors: Daniel Bardés i Vicente Jiménez. Informacions addicionals: • Duració de l’examen: 3 hores. • Lliureu les respostes dels diferents problemes i de les qüestions de pràctiques en fulls separats. Problema 1 (50%) Las puertas CMOS típicas basadas en un bloque P y otro N complementarios son las más habituales en diseños digitales pero tienen algunos inconvenientes. Entre ellos se halla la existencia de consumo de potencia cuando las entradas tienen tiempos de subida o bajada no despreciables o el área necesaria para incluir los dos bloques N y P complementarios. Una estructura de diseño que ataca algunos de estos problemas son las puertas con lógica dinámica “Domino”. En la siguiente figura se muestra un ejemplo. Vdd MP A MIP Vx Vo MIN MA C B MB CLK Inversor MC MN GND Las puertas en tecnología Domino emplean una puerta dinámica seguida de un inversor. La puerta tiene cualquier número de entradas, como cualquier puerta CMOS convencional (en el ejemplo hay tres: A, B y C) y una entrada de reloj CLK. La evaluación de una función lógica se realiza dos fases: • Precarga (CLK=”0”) se carga la capacidad asociada al nodo VX con un valor alto “1” empleando el transistor MP independientemente del valor de las entradas. • Evaluación (CLK=”1”) el nodo VX se descarga a “0” o permanece a “1” dependiendo del valor de las entradas A, B, C de la puerta. La salida VO pasará a tomar el valor complementario de VX. Se pide analizar el circuito del ejemplo, empezando por la función lógica que realiza. a) Determine la función lógica realizada por el circuito V0 = f(A,B,C) Los transistores tienen les siguientes tamaños: WN = 10 µm (los NMOS) WP = 20 µm (los PMOS) L = 2µm (todos). Para el cálculo de tiempos, podremos modelar los transistores en conducción como resistencias equivalentes. Las únicas capacidades que consideremos son las capacidades del óxido de puerta COX, entre la puerta y el surtidor de los transistores. b) Calcule la capacidad total del nodo VX debida a las puertas del inversor de salida. Fase de precarga. c) Encuentre el tiempo mínimo que debe durar la precarga para garantizar que se alcanza en VX un valor 0,5V por debajo de VDD (partiendo de un valor cero inicial). Fase de Evaluación. La velocidad de descarga, cuando la hay, dependerá del estado de las entradas A,B,C. d) Determine los valores mínimos y máximos posibles que puede tener el tiempo necesario para que VX evolucione, durante la evaluación, entre VDD y 0,5 V. e) A partir de los resultados de los apartados c) y d) encuentre la máxima frecuencia de CLK, para la puerta del ejemplo, si ha de funcionar para cualquier combinación de valores de entrada. En relación a la tecnología usada, se piden los siguientes cálculos: f) Determine, para la tecnología empleada, el grosor del óxido de puerta (en nanómetros) y la movilidad de los portadores µn, µp (en cm2/V s). Sabiendo que el óxido en cuestión crecería a un ritmo de 0,015 µm/h a 900ºC, según la ley de crecimiento de óxidos finos: g) Calcule el tiempo necesario para que crezca el óxido de puerta no a 900 ºC sino a 1000ºC. Datos: K’N = 60 µA/V2 K’P = 20 µA/V2 ε0 = 8,85⋅10-12 F/m k = 8,62⋅10-5 eV/K VTN = 0,8V VTP = -1 V εrSi = 11,68 VDD = 5 V C’ox = 2 fF/µm2 εrSi02 = 3,89 Problema 2 (50%) Volem estudiar l’amplificador diferencial BiCMOS d’una etapa amb entrada bipolar i sortida MOS que es mostra a la figura. L’entrada bipolar permet un guany elevat, i l’us de quatre transistors bipolars en lloc de dos fa que la resistència d’entrada no sigui molt baixa. En ell, tots els transistors MOS tenen el mateix valor de la constant de corrent k ( = kN = kP). També són iguals entre sí tots els transistors bipolars. VDD VDD M7 M5 VDD M6 VDD V - VDD M8 VDD V+ Q4 Q3 Q1 Q2 IB/2 V0 IB/2 VSS IB VSS VSS M10 M9 VSS VSS Per a l’anàlisi de petit senyal del circuit, noteu que les resistències ro dels bipolars i les rds dels MOS M5, M6, M7 i M9 no afecten de manera important el funcionament del circuit i per tant no cal considerar-les. a) Dibuixeu el seu circuit equivalent en petit senyal i mode diferencial, negligint les resistències no rellevants abans mencionades. b) Doneu l’expressió simplificada del guany diferencial del circuit complet en funció dels paràmetres de petit senyal dels transistors, assumint que βF >> 1. c) Escriviu, en funció del corrent de polarització IB, l’expressió de la gm dels transistors, la de les rπ i també de les rds dels transistors M8 i M10. Sabem que la λ dels transistors MOS val 0.01 V-1 i que a la temperatura d’anàlisi la vT = 25mV. d) Determineu el valor del guany diferencial en funció del corrent de polarització IB. e) Calculeu la resistència d’entrada en mode diferencial, definida com la relació entre vd i el corrent entrant per v+ (o sortint per v-). Preneu βF = 100 i IB = 40 µA. Donat que l’amplificador només consta d’una etapa, l’únic node en que podem realitzar compensació freqüencial és el de sortida. f) Calculeu quina capacitat de càrrega cal posar entre el node de sortida i massa per tal que el producte guany-ample de banda sigui de 10 MHz. Preneu, on calgui, les dades dels apartats anteriors. Qüestions sobre les pràctiques 1.- Extraieu el circuit elèctric de layout de la figura, corresponent a una porta AND feta amb transistors de pas. 2.- Estimeu l'amplada de la cel·la i la relació d'aspecte dels transistors del layout. 3.- Esbosseu el layout d’una porta AND alternativa, que sigui CMOS. 4.- Expliqueu com podríem fer, en l’entorn de pràctiques del laboratori, una simulació de la resposta DC de la porta que permetés veure la relació entre l’entrada B i la sortida amb l’entrada A constant. Enuncieu clarament cada un dels passos a seguir, i descriviu els fitxers que ens caldria generar. 5.- Dibuixeu l’aspecte del tall vertical del circuit sota la línia blanca. 6.- Al dissenyar un VCO com el de les pràctiques, hem escollit que la font doni 20 µA amb Sc = 2.5 V i que VH - VL = 0.5 V. Trobeu la freqüència central d’oscil·lació si la capacitat és de 0.25 nF. 7.- Proposeu una W i una L per al transistor M1 de la font.

![[Video] Contrainfos 27](http://s2.studylib.es/store/data/003896030_1-899519afe91f19fe474dc1f66fbbee03-300x300.png)

![[Video] Contrainfos 29](http://s2.studylib.es/store/data/003720643_1-37bf8791ba050f31fa2da1ba4587b9c5-300x300.png)