Diapositiva 1 - Escuela de Ingeniería Electrónica

Anuncio

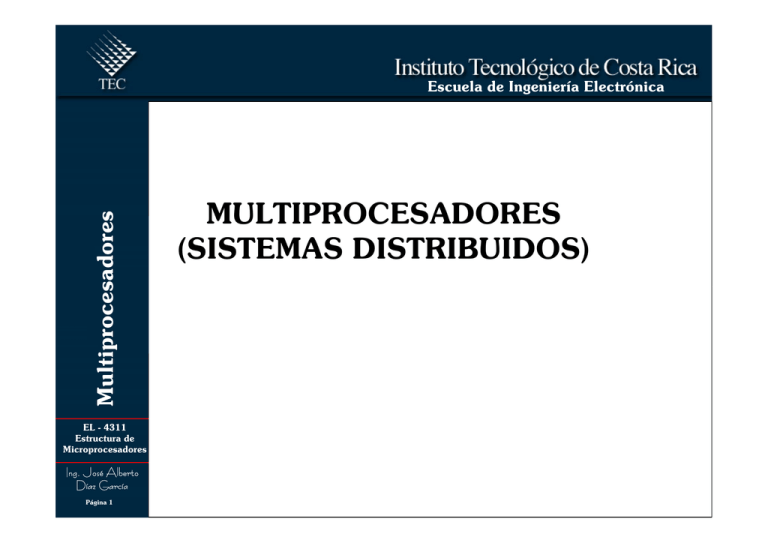

Multiprocesadores Escuela de Ingeniería Electrónica EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 1 MULTIPROCESADORES (SISTEMAS DISTRIBUIDOS) Escuela de Ingeniería Electrónica Multiprocesadores MODOS DE OPERACIÓN DEL 8086 EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 2 • Modo mínimo • Modo máximo Escuela de Ingeniería Electrónica Multiprocesadores OPERACIÓN EN MODO MINIMO EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 3 • La aplicación es específica, dedicada. • Ejemplos: – Controles para maquinaria, edificios. • La capacidad de procesamiento de la máquina es muy limitada. • Una vez desarrollado el sistema no se puede expandir. Escuela de Ingeniería Electrónica Multiprocesadores OPERACIÓN EN MODO MAXIMO EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 4 • Se quiere aumentar el procesamiento de información. • No cuenta con una aplicación definitiva. • Es un sistema abierto. Escuela de Ingeniería Electrónica Multiprocesadores CONSECUENCIAS DE OPERACIÓN EN MODO MAXIMO EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 5 • Las señales de control de modo mínimo para enrutar datos se dejan de generar. • Se necesitan de otros componentes para administrar el sistema eficientemente. • Se deben generar controles y prioridades para la utilización de los recursos del sistema. Escuela de Ingeniería Electrónica Multiprocesadores NECESIDADES EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 6 • ¿Quién se encarga de generar las señales de modo mínimo que se dejaron de generar por estar en modo máximo? Escuela de Ingeniería Electrónica Multiprocesadores CONTROLADOR DE BUS 8288 EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 7 • Es el encargado de proporcionar las señales de control para: – Manejar las direcciones – Manejar los datos – Manejar las interrupciones de modo mínimo que se dejaron de generar por estar ahora en modo máximo. Escuela de Ingeniería Electrónica Multiprocesadores CONTROLDADOR DE BUS 8288 EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 8 Escuela de Ingeniería Electrónica Multiprocesadores ENTRADAS AL CONTROLADOR EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 9 Escuela de Ingeniería Electrónica Multiprocesadores MODOS DE OPERACION EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 10 • Cuenta con dos modos de operación: – Modo I/O Bus. Bus para periféricos – Modo System Bus. Bus para el sistema Escuela de Ingeniería Electrónica Multiprocesadores MODO I/O BUS EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 11 • Este modo se selecciona cuando el pin IOB se conecta a un voltaje alto. • En este caso todas las señales para el control de puertos se llegan a activar dependiendo de la operación a ejecutar. • No dependen de la señal AEN. • Las señales PDEN y DT/R se utilizarían para activar el transceiver del bus para periféricos. • En este modo se pueden manejar dos buses externos. • No son necesarios los tiempos de espera para el procesador si este desea accesar el bus de puertos de entrada salida. • Los accesos normales a memoria requieren de la señal “Bus Ready”, (AEN en bajo) antes de proceder. • Es una ventaja utilizar el modo IOB si la arquitectura del sistema cuenta con periféricos dedicados a un solo procesador. Escuela de Ingeniería Electrónica Multiprocesadores MODO “System Bus” EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 12 • Se encuentra en este modo si el pin IOB se pone en bajo. • En este modo no se utilizan los comandos hasta que se active la señal AEN (bajo). • En este modo se asume una lógica para el arbitraje de bus, el cual le informa al controlador del bus el momento en que el bus se encuentra libre. • Tanto la memoria como los periféricos esperan por el arbitraje del bus. • Este modo se utiliza cuando solo existe un bus. Aquí ambos periféricos y memoria son compartidos por más de un procesador. Escuela de Ingeniería Electrónica DIAGRAMA ELÉCTRICO U3 1 2 3 4 5 6 7 8 U5 17 Multiprocesadores 16 EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 13 4 6 3 7 14 1 15 13 11 X1 READY CLK RESET X2 PCLK RDY1 RDY2 AEN1 AEN2 EFI CSYNC ASYNC F/C OSC 5 8 10 2 12 U2 22 19 21 18 READY CLK RESET INTR RES 8284 AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 AD8 AD9 AD10 AD11 AD12 AD13 AD14 AD15 A16/S3 A17/S4 A18/S5 A19/S6 BHE/S7 8259A 15 13 12 25 24 23 22 21 20 19 18 CAS2 CAS1 CAS0 IR7 IR6 IR5 IR4 IR3 IR2 IR1 IR0 INTA INT SP/EN WR RD CS A0 D7 D6 D5 D4 D3 D2 D1 D0 U6 26 17 16 2 3 1 27 4 5 6 7 8 9 10 11 31 30 17 23 33 S0 S1 S2 RQ/GT0 RQ/GT1 NMI TEST MX 8086MAX RD LOCK QS0 QS1 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 39 38 37 36 35 9 11 I0 I1 I2 I3 I4 I5 I6 I7 O0 O1 O2 O3 O4 O5 O6 O7 19 18 17 16 15 14 13 12 OE STB 8282 U4 1 2 3 4 5 6 7 8 9 11 A0 A1 A2 A3 A4 A5 A6 A7 B0 B1 B2 B3 B4 B5 B6 B7 19 18 17 16 15 14 13 12 OE T 8286 34 26 27 28 32 29 25 24 U1 19 3 18 2 15 1 6 S0 S1 S2 CLK CEN IOB AEN MRD MWT AMW IOR IOW AIOW INTA DT/R DEN MC/PD ALE 8288 7 9 8 13 11 12 14 4 16 17 5 Escuela de Ingeniería Electrónica Multiprocesadores CONCEPTOS EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 14 • El ‘BUS’ es un mecanismo para que varios dispositivos puedan compartir información. – Cuando un dispositivo trasmite el otro recibe. • Los datos pueden transmitirse por el bus en forma serial o paralela. – USB, IEEE Firewire son ejemplos de buses seriales – PCI, ISA, SCSI son ejemplos de buses paralelos • Los Buses solo pueden tener un master o múltiples masters. – Si se opera con varios bus masters, debe operarse con un arbitraje de bus para decidir el master o para programar el acceso al bus por parte de múltiples masters (división de tiempo, multiplexación); compartir en forma asíncrona o sincrónica. Escuela de Ingeniería Electrónica Multiprocesadores CONCEPTOS BUS DEL PROCESADOR/MEMORIA BUS PCI EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 15 BUSES DE PERIFERICOS Escuela de Ingeniería Electrónica Multiprocesadores CONCEPTOS EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 16 • El BUS LOCAL es aquel que es residente para el microprocesador. • El bus local contiene la memoria y la entrada/salida residente, o local. • Es un bus de un gran ancho de banda • Es un bus paralelo sincronizado a una alta razón. • Las líneas de direcciones, datos y control, corren en una distancia bien corta. • El bus PCI es un ejemplo de un bus local conectado por medio de chip set al microprocesador. Escuela de Ingeniería Electrónica Multiprocesadores CONCEPTOS EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 17 • El SYSTEM BUS o BUS COMPARTIDO es aquel que está conectado a todos los microprocesadores del sistema. • Se utiliza para intercambiar datos entre los microprocesadores del sistema. • Contiene dispositivos de memoria y de entrada/salida a los que todos los microprocesadores del sistema tienen acceso. • El acceso al bus compartido es controlado por alguna fuente o por un árbitro, que permite el acceso al espacio del bus compartido del sistema a un solo microprocesador a la vez. • El chipset del sistema puede transferir datos entre el bus del sistema y otros buses que lo requieran. • Esto es funciona como un puente entre el sistema y otros buses. Escuela de Ingeniería Electrónica Multiprocesadores “Bus Mastership” EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 18 • DMA es un ejemplo en donde el procesador cede el control de los buses a otro dispositivo. (DMAC) • El dispositivo que tiene control del bus, que no sea el procesador se conoce como “BUS MASTER”. • Los componentes de memoria y periféricos de entrada salida que no utilizan DMA se conocen como componentes “BUS SLAVE”. • En los primeros diseños de computadores, solo los procesadores y los dispositivos DMAC tenían control sobre el bus (Bus Master) • En los sistemas modernos los buses (por ejemplo PCI) permiten a los dispositivos I/O operar como masters. • Un dispositivo de I/O que puede operar como master puede realizar operaciones de DMA por el mismo en lugar de utilizar DMAC • Si todas las tarjetas de I/O pueden operar como master, entonces no necesitan de un controlador de DMA, cada tarjeta es un DMAC. Escuela de Ingeniería Electrónica Multiprocesadores VENTAJAS DE LOS BUSES EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 19 • Versatilidad: – Los nuevos dispositivos se pueden agregar fácilmente al sistema. – Los periféricos pueden moverse entre el computador si utilizan el mismo estándar. • Bajo costo: – Un simple grupo de cables se comparten de múltiples formas. • Manejan muy bien la complejidad del sistema ya que se particiona el diseño. Escuela de Ingeniería Electrónica DESVENTAJAS DE LOS BUSES Multiprocesadores • Crea cuellos de botella en la comunicación. EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 20 – El ancho de banda del bus puede limitar el manejo de los periféricos. • La velocidad máxima del bus esta limitada por: – El largo del bus. – La cantidad de dispositivos en el bus. – La necesidad de soportar una cantidad de dispositivos con: • Amplia variedad de protocolos. • Amplia variedad de velocidades de transferencia. Escuela de Ingeniería Electrónica TIPOS DE BUSES • BUS DEL PROCESADOR-MEMORIA (diseño específico) – Cortos y de alta velocidad – Solo necesitan accesar al sistema de memoria Multiprocesadores • Maximiza el ancho de banda de la relación memoria a procesador EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 21 – Se conecta directamente al procesador – Se optimiza en la transferencia de bloques entre la memoria cache. • BUS I/O (estándar industrial) – Generalmente es mas lento y largo. – Necesita ofrecer servicio a una amplia gama de dispositivos de entrada/salida. – Interconecta al bus procesador-memoria o al bus Backplane (bus del sistema) • BUS BACKPLANE (estándar o propietario) – Backplane: una estructura de interconexión con el chassis. – Permite a los procesadores, memoria y dispositivos de entrada/salida coexistir. – Ventaja de costo: un bus para todos los componentes. Escuela de Ingeniería Electrónica Multiprocesadores COMPUTADORES CON UN SOLO TIPO DE BUS EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 22 Bus Backplane PROCESADOR MEMORIA DISPOSITIVOS DE ENTRADA/SALIDA • Un solo bus (backplane bus) se utiliza para: – Comunicación entre la memoria y el procesador – Comunicación entre los dispositivos de entrada salida y la memoria. • Ventajas: Simple y de bajo costo • Desventajas: lento y el bus se convierte en un cuello de botella. • Ejemplo: IBM PC – AT Escuela de Ingeniería Electrónica COMPUTADOR CON DOS TIPOS DE BUSES BUS DE PROCESADOR-MEMORIA MEMORIA Multiprocesadores PROCESADOR EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 23 ADAPTADOR DE BUS I/O Bus ADAPTADOR DE BUS I/O Bus ADAPTADOR DE BUS I/O Bus • Los buses de I/O se comunican con el procesador por medio de adaptadores: – El bus procesador-memoria: principalmente para el trafico de operaciones entre el procesador y la memoria. – Buses para I/O: provee con conectores para expansión para los dispositivos periféricos. • Apple Macintosh-II – NuBus: procesador, memoria, y algunos dispositivos de entrada y salida. – Bus SCCI: los dispositivos restantes de entrada/salida. Escuela de Ingeniería Electrónica COMPUTADOR CON TRES BUSES BUS PROCESADOR MEMORIA Multiprocesadores PROCESADOR EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 24 MEMORIA ADAPTADOR DE BUS ADAPTADOR DE BUS BUS I/O Backplane Bus ADAPTADOR DE BUS BUS I/O • Una pequeña cantidad de buses backplane se conectan al bus procesador-memoria. – El bus procesador-memoria se utiliza para el tráfico de información entre el procesador y la memoria. – Los buses de I/O se conectan al bus backplane. • Ventaja: se reduce la carga del bus del procesador. Escuela de Ingeniería Electrónica ¿Qué define un bus? Multiprocesadores Protocolo de transmisión EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 25 Especificaciones de temporización y señalización Grupo de cables Especificaciones eléctricas Características Físicas/Mecánicas – los conectores Escuela de Ingeniería Electrónica BUSES SINCRÓNCIOS Y ASINCRÓNCIOS Multiprocesadores • BUS SINCRÓNICO: EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 26 – Incluye el reloj en las señales de control. – Cuenta con un protocolo de comunicación relacionado con el reloj. – Ventaja: se necesita de una pequeña lógica y puede correr muy rápido. – Desventaja: • Todos los dispositivos deben correr a la misma velocidad del reloj. • Para eliminar los corrimientos del reloj, no pueden ser largos para no perder la velocidad. • BUS ASINCRONICO: – – – – – No necesita de un reloj Permite conectarse una amplia gama de dispositivos. Puede aumentar el largo del bus sin preocuparse. Requiere de un protocolo de comunicación por handshaking. Requiere un protocolo del apretón de manos Escuela de Ingeniería Electrónica Multiprocesadores Tipos de buses EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 27 • Desde la introducción de los computadores se han generado diferentes tipos de buses para el manejo de periféricos. • ¿Porqué tantos? – La velocidad de los periféricos debe ser alta para mejorar el rendimiento del sistema. • Para mejorar el rendimiento deben de contemplarse las siguientes tres áreas: – Procesadores veloces – Incremento en la demanda del software – Mayores requerimientos de multimedia • Cualquiera de estas áreas requiere que el bus para los puertos de entrada/salida sean lo más rápido posibles. Escuela de Ingeniería Electrónica Buses en PC-XT y PC-AT Multiprocesadores BIOS EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 28 timer, int. contl. bus buffer ISA bus CPU DRAM contrl. DMA contrl. DRAM expansion slots • ISA (Industry Standard Architecture) – IBM-PC y PC-XT: 8 bits a 4.77MHz, directamente conectado a un 8088, ciclo de bus de 2-estados (2.38Mbyte/seg ancho de banda del bus) – AT bus: extension slot + 8 bit ISA • 16 bits a 8.33MHz para 80286 Escuela de Ingeniería Electrónica Multiprocesadores Bus ISA (8 bits) EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 29 Escuela de Ingeniería Electrónica Multiprocesadores Bus ISA de 16 bits EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 30 Escuela de Ingeniería Electrónica Buses en el PC(486) Multiprocesadores DRAM EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 31 486 CPU local bus L2 cache ISA bridge ISA bus bus buffer video card LAN adapter HDD contrl. expansion slots • El 16-bit ISA no puede manejar las aplicaciones de Windows • VESA LB (local bus) -- 486 local bus, 33MHZ, 32 bits Escuela de Ingeniería Electrónica Multiprocesadores FILOSOFÍA DE DISEÑO (BUS LOCAL) EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 32 Escuela de Ingeniería Electrónica Buses en un PC (Pentium) Pentium CPU Multiprocesadores host bus EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 33 PCI chipset PCI bridge L2 Cache Data bus Memory PCI bus Video card LAN adapter PCI/ISA bridge SCSI adapter IDE controller monitor ISA bus SuperIO chip Modem sound card Escuela de Ingeniería Electrónica Multiprocesadores CHIP SETS EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 34 DMA Escuela de Ingeniería Electrónica Multiprocesadores MULTIPROCESADOR EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 35 • El concepto de multiprocesador surge cuando es necesario realizar algunas tareas en forma simultánea y para un único procesador es imposible realizarlas, de esta forma se pueden distribuir las tareas sobre varios procesadores trabajando en paralelo. Escuela de Ingeniería Electrónica Multiprocesadores CONECTORES PARA PERIFÉRICOS EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 36 Escuela de Ingeniería Electrónica MULTIPROCESADOR Multiprocesadores MEMORIA EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 37 MICROPROCESADOR MICROPROCESADOR 1 1 ENTRADA/ SALIDA MEMORIA BUS DE SISTEMA MULTIPROCESADOR ENTRADA/ SALIDA MEMORIA MICROPROCESADOR MICROPROCESADOR 2 2 ENTRADA/ SALIDA Escuela de Ingeniería Electrónica Multiprocesadores PRINCIPIO DE OPERACIÓN EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 38 • El intercambio de información de un procesador a otro se efectúa a través de un bus de sistema multiprocesador. • Este tipo de configuraciones define dos conceptos más: – AMO y – ESCLAVO. • El AMO es aquel que realiza el control principal del computador. • El ESCLAVO es el que contribuye a que el amo realice las tareas. • Cada uno de los procesadores puede: – accesar memoria – módulos de entrada/salida privados y también a los compartidos o públicos. • Se puede dividir las tareas de tal forma que: – los procesadores trabajen relativamente independientes (MULTIMASTER SYSTEM) – o que uno asuma el mando y asigne las tareas a los demás (MASTER SLAVE SYSTEM). Escuela de Ingeniería Electrónica Multiprocesadores PRINCIPIO DE OPERACIÓN EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 39 • El concepto multiprocesador puede contener también procesadores de diferentes tipos, los cuales en cada caso están óptimamente adaptados a una determinada tarea, por ejemplo: – el procesador aritmético, – procesadores gráficos – procesadores para entrada/salida de datos, etc. Escuela de Ingeniería Electrónica TÉCNICA DE SEMÁFOROS Multiprocesadores • En un sistema multicomputador, la memoria compartida (memoria del sistema) puede ser utilizada para diferentes funciones: EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 40 – contener varias tareas, es decir códigos de instrucciones para determinadas tareas parciales dentro de un programa. – por ejemplo lectura de valores de medición, impresión de una lista de resultados, resolución de una operación aritmética, etc. • Un procesador que finalizó la ejecución de una tarea, – recoge de la memoria del sistema la siguiente tarea – la traslada a su memoria particular y la ejecuta. • Pero la memoria del sistema también puede tener áreas que varios procesadores utilizan para almacenar datos de forma intermedia. – por ejemplo, resultados de cálculos, o para la comunicación entre ellos, depositar mensajes. Escuela de Ingeniería Electrónica Multiprocesadores TÉCNICA DE SEMÁFOROS EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 41 • Si se da el caso que dos o más procesadores acceden simultáneamente a una de estas áreas de memoria compartidas: – por ejemplo, a la misma tarea o uno de los procesadores quiere leer valores de medición que otro justamente quiere escribir, se pueden originar conflictos. • Por este motivo a cada área de memoria compartida (ROM, RAM) se le asigna un byte adicional (en la RAM), el así llamado byte semáforo. – Si en el byte de semáforo hay un “1”, entonces su correspondiente área de memoria está “ocupada”, un “0” señaliza que dicha área está libre. – Cada procesador antes de accesar a esta área de memoria, debe leer el byte semáforo; si es “0”, le escribe un “1” y se reserva para sí momentáneamente el derecho de acceso. Cuando finaliza su cometido, escribe un “0” y vuelve a liberar dicha área de memoria. Escuela de Ingeniería Electrónica TÉCNICA DE SEMÁFOROS Multiprocesadores • EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 42 En la práctica se procede con la técnica de semáforos de la siguiente forma: – – – • • • • El 8086 lee el byte de semáforo y luego escribe en él un 1; ambas operaciones las efectúa con una única instrucción de intercambio (exchange). Luego se analiza si el byte semáforo leído contenía un 1 o un 0. Si ya contenía un 1, la reinscripción de un 1 no alteró al byte semáforo y el procesador debe esperar; si contenía un 0, la inscripción de un 1 reservó al área de memoria y el procesador tiene acceso. Pero el momento crítico en la técnica de semáforos es cuando la instrucción de intercambio contiene un ciclo de lectura y un ciclo de escritura que pueden ser separados por el administrador del bus. Así se puede dar el caso que un segundo procesador ejecuta inmediatamente después del primero un ciclo de lectura sobre el byte de semáforo y también lee un 0 debido a que el ciclo de escritura del primero para escribir un 1 todavía no fue ejecutado. Para evitar un conflicto de este tipo, existe la posibilidad de colocar un prefijo de LOCK (bloqueo) en la instrucción de intercambio; este prefijo origina sobre el conductor LOCK una señal LOCK (señal de bloqueo), que le informa al administrador del bus que el próximo ciclo de instrucciones se debe ejecutar sin perturbaciones. El acceso al bus compartido del amo de bus remoto se logra por medio de un árbitro de bus que funciona para resolver la prioridad entre los amos de bus, sólo permite acceso a uno a la vez al bus compartido. Escuela de Ingeniería Electrónica Multiprocesadores ¿Qué es arbitraje? EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 43 • El arbitro es una lógica de control que debe decidir cual dispositivo toma control del bus; normalmente este circuito reside en los chipsets del sistema y es parte del sistema completo. • Hay dos líneas que son utilizadas para asignar el bus a cada uno de los periféricos: – Bus Request – utilizada por los dispositivos para solicitar el bus. – Bus Grant – utilizada para asignar el bus al dispositivo. • Generalmente los periféricos tienen control del bus por un número máximo de pulsos de reloj (32 aproximadamente) antes de que transfiera el bus al arbitro. Escuela de Ingeniería Electrónica Multiprocesadores ESQUEMA DE ARBITRAJE EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 44 • El arbitraje del bus puede ser dividido en cuatro tipos: – – – – Cadena de margaritas Centralizado, arbitraje paralelo Distribuido, por auto selección Distribuido por detección de colisión Escuela de Ingeniería Electrónica Multiprocesadores ARBITAJE POR CADENA DE MARGARITAS (DAISY CHAIN) EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 45 Dispositivo 1 Alta Prioridad Grant Dispositivo “n” Prioridad Muy baja Dispositivo 2 Prioridad media Grant Arbitro de bus Grant Release Request OR alambrada • • Ventaja: sencillo Desventajas: – No hay certeza de servicio: • El dispositivo con más baja prioridad podría nunca recibir servicio. – El uso de las señales en daisy chain limita la velocidad del bus. Escuela de Ingeniería Electrónica Multiprocesadores ARBITRAJE CENTRALIZADO (ARBITRAJE PARALELO) EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 46 Dispositivo A Dispositivo B Dispositivo N Grant A Req A Bus Arbiter Grant B Req B Grant N Req N Data Bus Control Bus • Utilizado principalmente por los buses memoriaprocesador y en los buses para periféricos de alta velocidad. Escuela de Ingeniería Electrónica Multiprocesadores ARBITRAJE DISTRIBUIDO (POR AUTOSELECCIÓN) EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 47 • Cuenta con múltiples señales para la solicitud del bus, pero el dispositivo que solicita el bus determina el ingreso. – Cada dispositivo que quiere utilizar el bus coloca su código de identidad en el bus de solicitud. – Cada dispositivo examina el bus de solicitud y determina donde se encuentra el solicitante de más alta prioridad. – Nota: Requiere de más señales para solicitud. – Ejemplo: NuBus en Apple IIs Escuela de Ingeniería Electrónica Multiprocesadores ARBITRAJE DISTRIBUIDO (POR DETECCIÓN DE COLISIONES) EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 48 • Ejemplo = ethernet • Cuando un dispositivo en particular quiere utilizar el bus: – Prueba si algún dispositivo está utilizando el bus. – Si no, trasmite sus datos • Problema: Dos dispositivos pueden encontrarse el bus libre e iniciar su transmición al mismo tiempo. • Resultado = Colisión – Detectada cuando los datos del bus difieren de los transmitidos. • Solución: Ambos nodos detienen la transmición y esperan un intervalo de tiempo prudencial para restablecer la transmición. Escuela de Ingeniería Electrónica Multiprocesadores SIMPLE IMPLEMENTACION DE UN ARBITRO DE BUS EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 49 Escuela de Ingeniería Electrónica Multiprocesadores LOGICA PARA LA PRIORIDAD EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 50 Escuela de Ingeniería Electrónica Multiprocesadores Arbitro 8289 EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 51 • Provee del control necesario para que varios procesadores tomen control del bus compartido. • Provee control sobre el Multimaster System Bus • Arbitraje • Sincroniza el procesador con el Multimaster System Bus Escuela de Ingeniería Electrónica BUS ARBITER 8289 Multiprocesadores • EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 52 • • • • • • • Opera en conjunto con el controlador de bus 8288 para permitir al 8086 trabajar en modo máximo para que permita el uso de los buses por parte de múltiples procesadores. El procesador no se percata de la existencia del arbitro y ejecuta sus órdenes como si tuviera a su plena disposición el bus. Si el procesador no necesita del Multimaster System Bus, el arbitro le indica al Controlador del Bus (82C88), para que sus salidas para el manejo del bus se coloquen en tercer estado. Si la secuencia de órdenes no se genera por el 82C88, el sistema aparece como “Not Ready” y el procesador entra en estados de espera. El procesador permanecerá en el estado de espera (WAIT) hasta que el Arbitro del Bus adquiera el uso del Multimaster System Bus, después el arbitro permitirá al controlador del bus generar las señales que permitan el acceso al bus del sistema. Generalmente una vez que se ha realizado un orden y los datos han sido transferidos una señal de reconocimiento de transferencia se genera (XACK) para indicarle al procesador que se encuentra “READY”. Luego el procesador completa su ciclo de transferencia. Así el arbitro se utiliza para multiplexar el procesador (bus master) al Multimaster System Bus y de esta forma elimina problemas de disputa entre amos por el acceso al bus. Escuela de Ingeniería Electrónica Multiprocesadores Arbitro 8289 EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 53 Escuela de Ingeniería Electrónica Multiprocesadores ARBITRAJE ENTRE AMOS DEL BUS EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 54 • Los masters con alta prioridad tomaran el bus una vez que los masters con baja prioridad completen sus transferencias. • Los masters con baja prioridad toman el bus cuando ningún master con alta prioridad solicite el bus. • Sin embargo existe la opción de (ANYRQST) para permitirle al arbitro asignar el bus a un master de baja prioridad como si este tuviera una prioridad mayor. – Si no hay otros masters solicitando el bus, el arbitro mantiene el bus hasta que el procesador no entre en un estado de espera, (HALT State). • El arbitro no liberará el bus voluntariamente, deberá ser forzado por parte de otra solicitud de otro master para que libere el bus y lo seda a este segundo, el estado de espera es la única excepción. Escuela de Ingeniería Electrónica Multiprocesadores TECNICAS PARA LA ASIGNACIÓN DE PRIORIDAD EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 55 • • • • Prioridad paralela Prioridad serie Prioridad rotativa Todas las técnicas se basan en el concepto de prioridad en donde en un tiempo dado un master que solicita el bus tiene una prioridad mayor al resto de los dispositivos que accesan el bus. Multiprocesadores COMMON BUS REQUEST: Esta es una señal de entrada/salida que permite al arbitro si hay solicitudes de árbitros de más baja prioridad solicitando el bus solicitar el bus. PRIORIDAD árbitros PARALELA del sistema. EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 56 BUS REQUEST: es una salida activa en nivel bajo en una Escuela de Ingeniería Electrónica configuración de prioridad que le permite a diferentes BUSY: Es una señal de colector abierto para indicarle a los árbitros del bus cuando el bus del BUS PRIORITY IN: activa en sistema está nivel bajo que es devuelta al disponible.arbitro para indicarle que puede utilizar el bus después del próximo ciclo de reloj en BCLK'. Escuela de Ingeniería Electrónica Multiprocesadores PRIORIDAD SERIE EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 57 • Con este método se conecta la salida BPRO con la entrada BPRN al 8289 que tenga la prioridad inmediata inferior; es el menos costoso de implementar. Intel recomienda que este método se limite a no más de tres 8289 en un sistema en que se use un reloj de canal de 10Mhz o menos. Escuela de Ingeniería Electrónica Multiprocesadores PRIORIDAD ROTATIVA EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 58 • Es similar a la prioridad paralela excepto de que se asigna en forma dinámica. • El codificador de prioridad (74148) se reemplaza por una más complejo. El cual rota la prioridad entre los árbitros que solicitan el bus, permitiéndoles a cada uno de ellos la misma oportunidad de utilizar el Multimaster System Bus. Escuela de Ingeniería Electrónica Multiprocesadores MODOS DE OPERACIÓN EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 59 • El 8289 puede dar servicio a dos tipos de procesadores: – Procesador de entradas y salidas (NMOS 8089 IOP) – A los procesadores 8086, 8088. • Consecuentemente hay dos modos de operación: – Modo IOB (I/O Peripheral Bus), permite al procesador accesar el bus de periféricos y el Multimaster System Bus. – Modo RESB (Resident Bus mode), permite comunicarse con el bus residente y el Multimaster System Bus. Escuela de Ingeniería Electrónica Multiprocesadores DEFINICION DE BUSES EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 60 Bus local Escuela de Ingeniería Electrónica Multiprocesadores BUS DE ENTRADA/SALIDA (I/O Peripheral Bus ) EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 61 • Es un bus donde todos los dispositivos del bus, incluyendo la memoria son tratados como dispositivos de entrada/salida y son accesados por medio de comandos de entrada/salida. • Todos los comandos de memoria son dirigidos a otro bus, el Multimaster System Bus. Escuela de Ingeniería Electrónica Multiprocesadores BUS RESIDENTE EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 62 • El bus residente puede manejar comandos para el manejo de memoria y para el manejo de puertos de entrada/salida. Pero es un bus distinto al Multimaster System Bus. • La diferencia es que el bus residente tiene un solo master. • Cuenta con toda la disposición del bus. BUS RESIDENTE EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 63 B U S L O C A L MULTIMASTER SYSTEM BUS Multiprocesadores BUS RESIDENTE Escuela de Ingeniería Electrónica Escuela de Ingeniería Electrónica SELECCIÓN DE MODOS DE OPERACION • IOB RESB MODO 0 0 BUS PARA ENTRADA SALIDA 0 1 BUS DE ENTRADA SALIDA Y RESIDENTE 1 0 BUS SIMPLE 1 1 BUS RESIDENTE Multiprocesadores EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 64 El pin IOB es activo en bajo y configura el 82C89 para que opere en modo IOB, el pin RESB que es activo en alto configura el 8289 para que opere en modo RESB. • DESCRIPCION Todos los componentes que hay en el bus local se consideran como E/S incluso la memoria, y se accesa a ellos con instrucciones para el espacio de entrada/salida. Todas las referencias a la memoria permiten acceso al bus compartido y todos los dispositivos de E/S acceden al bus local residente. Sirve de interface del microprocesador con un bus compartido pero el microprocesador no tiene memoria ni E/S locales. En muchos sistemas, el microprocesador se inicializa como el amo de bus compartido (modo de bus sencillo) para controlar y poder ser amo del bus compartido. Permite acceso a la memoria y a E/S en los buses local y compartido. Se puede notar que cuando las dos opciones son falsas, o sea IOB = 1 y RESB = 0, el arbitro conecta el procesador al Multimaster System Bus. Escuela de Ingeniería Electrónica Multiprocesadores BUS LOCAL EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 65 MULTIMASTER SYSTEM BUS BUS SIMPLE Escuela de Ingeniería Electrónica Multiprocesadores • EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 66 • • Cuando ambas opciones son cero, IOB =0 y RESB =0. El arbitro permite el acceso del procesador al Multimaster System Bus , al bus residente y la bus de periféricos. En el modo IOB, el procesador permite que se comuniquen los periféricos por medio del bus de periféricos. El procesador utiliza el bus de memoria del sistema cuando necesita comunicarse con la memoria del sistema. SELECCIÓN DE MODOS DE OPERACION B U S P A R A P E R I F E R I C O S M U L T I M A S T E R S Y S T E M B U S Escuela de Ingeniería Electrónica Multiprocesadores SELECCIÓN DE MODOS DE OPERACION EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 67 • Para que un procesador 8086 o 8088 se comuniquen por medio de un Bus Residente y un Multimaster System Bus, se necesitan en la configuración dos controladores de bus y de un arbitro. • En este tipo de configuración el procesador tiene acceso a la memoria y a los periféricos por medio de dos buses. • Las técnicas de mapeo de memoria se deben aplicar para seleccionar el bus que la accesará. • La entrada SYSB/RESB en el arbitro se utiliza para indicarle al arbitro si el bus del sistema será accesado o no. • La señal conectada a SYSB/RESB también habilita o desabilita las ordenes de uno de los dos controladores de buses. Escuela de Ingeniería Electrónica Multiprocesadores SELECCIÓN DE MODOS DE OPERACION EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 68 Multiprocesadores Escuela de Ingeniería Electrónica EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 69 Multiprocesadores Escuela de Ingeniería Electrónica EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 70 Multiprocesadores Escuela de Ingeniería Electrónica EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 71 Escuela de Ingeniería Electrónica Arquitectura típica de un computador basado en X86 con buses tipo PCI Multiprocesadores L3 Cache EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 72 AGP L2 Cache SDRAM System Bus 64-bit L1 Cache x86 CPU Common Package PCI Adapter 1PCI Adapter 2North Bridge PCI Adapter 3PCI Adapter 4 PCI Bus 32-bit EIDE 1 EIDE 2 XD Bus 8-bit Flash Mem BIOSRTC and CMOS South Bridge USB Root Hub 1 USB Root Hub 2 KBD, PS/2, LPT, UART1, UART2, Floppy ISA Bus 16-bit ISA Adapter 1 ISA Adapter 2 Escuela de Ingeniería Electrónica Multiprocesadores Tarjeta Madre AMD EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 73 Multiprocesadores Escuela de Ingeniería Electrónica EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 74 Escuela de Ingeniería Electrónica Multiprocesadores Investigación bus de memoria(1993) EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 75 Characteristics Originator Clock Rate (MHz) Address lines Data lines Data Sizes (bits) Clocks/transfer Peak (MB/s) Master Arbitration Slots Busses/system Length MBus Sun 40 36 64 256 320(80) Multi Central 1 Summit HP 60 48 128 512 4 960 Multi Central 16 1 13 inches Challenge SGI 48 40 256 1024 5 1200 Multi Central 9 1 12? inches XDBus Sun 66 muxed 144 (parity) 512 4? 1056 Multi Central 10 2 17 inches Escuela de Ingeniería Electrónica Multiprocesadores Investigación bus Backplane EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 76 Characteristics Originator Clock Rate (MHz) Addressing Data Sizes (bits) Master Arbitration 32 bit read (MB/s) Peak (MB/s) Max Power (W) SBus Sun 16-25 Virtual 8,16,32 Multi Central 33 89 16 TurboChannel DEC 12.5-25 Physical 8,16,24,32 Single Central 25 84 26 MicroChannel IBM async Physical 8,16,24,32,64 Multi Central 20 75 13 PCI Intel 33 Physical 8,16,24,32,64 Multi Central 33 111 (222) 25 Escuela de Ingeniería Electrónica Investigación bus Serial I/O Multiprocesadores Metrics EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 77 Effective Bandwidth Power Multi-master Fault Tolerance Max. # Nodes Max Bus Length Protocol Overhead IEEE 1394 (cable) SFODB (IEEE 1393) FIBRE CHANNEL I2C 100, 200, 400 Mbps 200 Mbps, 1 Gbps 1 Gbps 100, 400 Kbps 1 W/node 5 W/node 2 W/node 5 mW/node Yes Yes Yes Yes CRC for error detection Redundant ring with cross-strap bypass links 127 nodes Redundant ring with bypass links, CRC for error detection Loop; 127 Switched: no limit No redundancy in topology. Error detection by Ack bit Addressable up to 128 nodes or up to max loading of 400 pf up to max loading of 400 pf 64 nodes 72 m (4.5 m/hop) 8 % overhead with 278 byte payload data 10 km, 100m node spacing Fiber: 10 km Electrical: 30 m 10 % overhead with 25 % overhead with 53 byte payload 2168 byte payload 1 byte for address & R/W + 1 Ack bit per data byte Escuela de Ingeniería Electrónica Multiprocesadores Investigación buses Estándar EL - 4311 Estructura de Microprocesadores Ing. José Alberto Díaz García Página 78 Characteristic VME Bus NuBus FutureBus IPI SCSI PCI Bus Type Backplane Backplane Backplane I/O I/O Backplane Bus width (signals) 128 96 96 16 8 48 Address / data Multiplexed? Not Multiplexed 16- 32 bits Multiplexed Multiplexed N/A Multiplexed Multiplexed 32 bits 32 bits 16 bits 8 bits 32 bits Multiple Multiple Multiple Single Multiple Multiple Multiple daisy chain Distributed selfselection Async N/A Selfselection Any Async Either Sync Data width (primary) Number of bus masters Arbitration Clocking Async Distributed selfselection Sync Bandwidth, 150ns memory single word 12. 9 MB/s 13. 2 MB/s 15. 5 MB/s 25. 0 MB/s 5.0 MB/s or 1.5 MB/s 16. 5 MB/s Bandwidth, 150ns memory, multi word (infinite length) Maximum number of devices 13. 6 MB/s 26. 4 MB/s 20. 8 MB/s 25. 0 MB/s 5.0 MB/s or 1.5 MB/s 132 MB/s 21 16 20 8 7 10 Maximum bus length 0.5 meters 0.5 meters 0.5 meters 50 meters 25 meters 0.5 meters Standard name IEEE 1014 IEEE 1196 IEEE 869. 1 ANSI X3.129 ANSI X3.131 PCI