Capítulo 8: Encapsulado

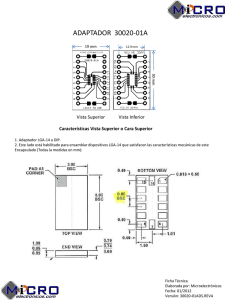

Anuncio

página >>1 Introducción al Diseño de CIs Universitat Autònoma de Barcelona Curso académico 2009-10 Elena Valderrama Ingeniería Informática Diseño de Circuitos Integra ados I Capítulo 8: Encapsulado página >>2 Diseño de Circuitos Integra ados I Introducción Capítulo 8 : Encapsulado Elena Valderrama Capítulos 1 2 3 8 9 10 4 5 6 Introducción 7 Una vez el ASIC está completamente c diseñado se envía a fábrica. Allí, el primer paso que se realiza es la fabricación de las máscaras; una para cada nivel del proceso CMOS. En cada una de ellas se repite el motivo o fundamental (circuito) tantas veces (n) como es posible (figura 1). A continuación se pone en e marcha la línea de procesos correspondientes a la tecnología que acabarán construyendo sobre cada una de las obleas de Silicio n copias del circuito representado por el layout. Tras pasa ar las comprobaciones necesarias las obleas se cortan, obteniéndose n pastillas de silicio (o dados, o dice), réplicas idénticas del circuito diseñado. ver figura >> 01 on todavía inutilizables, es necesario hacer algo para que éstas puedan Las pastillas tal cual so conectarse con el resto de d los componentes que configurarán el sistema final. Este último proceso recibe el nombre de encapsulado, y es el objeto de este capítulo. Materiales • En la inmensa mayoría m de los casos las pastillas de silicio se montarán sobre una cápsula como las que esstamos habituados a ver en los circuitos integrados convencionales; se pegará la pastilla a sobre la cápsula y se “soldarán” soldarán hilos desde los pads de la pastilla hasta los pines de la cá ápsula. Es responsabilidad del diseñador seleccionar la cápsula que mejor se adapte a las características c del circuito. • En casos muy particulares es posible que la pastilla esté destinada a ser montada directamente sob bre el substrato, p.e. la PCB1 • Existe todavía una tercera p posibilidad;; q que la p pastilla se monte sobre un substrato q que p y, todas juntas, se encapsulen. Esta última técnica se conoce con contenga otras pastillas el nombre de MC CM (Multi-Chip-Module) o Módulo Multi Chip. Tipos de encapsulados El conexionado Reglas de encapsulado Unión directa a substrato e híbridos MCMs Resumen 1 Ingeniería Informática PCB: Printed Circuit Board d B Universidad Autónoma de Barcelona página >>3 Diseño de Circuitos Integra ados I Introducción Capítulo 8 : Encapsulado En este capítulo se explicarán brevemente estas técnicas haciendo especial hincapié en aquellas partes del proceso en lass que el diseñador debe especificar sus necesidades. Nos centraremos en primer lugar en el uso de e cápsulas (o encapsulados como también se denominan frecuentemente) por ser el método más habitual, y posteriormente describiremos brevemente la unión directa a substrato y los MCMs. MCMs Elena Valderrama Capítulos 1 2 3 8 9 10 4 5 6 7 Introducción Materiales Tipos de encapsulados El conexionado Reglas de encapsulado Unión directa a substrato e híbridos MCMs Resumen Ingeniería Informática Universidad Autónoma de Barcelona B página >>4 Diseño de Circuitos Integra ados I Materiales Capítulo 8 : Encapsulado En el proceso de encapssulado se trabaja con tres componentes fundamentales: (1) la cápsula en sí sobre la cual se pega el e dado de silicio y que llamaremos base, (2) los hilos conductores que unirán cada uno de los pads p del circuito al pin correspondiente de la cápsula, y (3) la propia pastilla de silicio. Una vez cortados los dados, el técnico responsable del encapsulado pega el dado a su base y une con hilos co onductores cada uno de los pads del circuito al pin correspondiente de la cápsula. Elena Valderrama Capítulos 1 2 3 8 9 10 4 5 6 7 ver figura >> 02 La base debe: 1. Servir de soporte e al circuito Introducción 2. Protegerlo del en ntorno Materiales 3. Disipar el calor ge enerado por éste. Tipos de encapsulados Y para ello a la base se le l pide que: El conexionado 1. Sea robusta Reglas de encapsulado 2. Tenga una alta co onductividad térmica para que disipe bien el calor Unión directa a substrato e híbridos 3. Tenga un coeficie ente de expansión térmica (dilatación) lo más parecido posible al del silicio para que los cam mbios de temperatura no causen un excesivo stress en la unión dado-base MCMs Resumen 4. Aísle se e eléctricame éct ca e ente te e el dado de ssilicio c o de del e entorno to o o, lo o que es lo o mismo, s o, que te tenga ga u una a constante dieléctrica alta. 5. Esté compuesta por materiales fáciles de procesar La tabla siguiente muesttra algunos de los materiales más frecuentemente utilizados como base de los encapsulados y sus características. c Ingeniería Informática B Universidad Autónoma de Barcelona página >>5 Diseño de Circuitos Integra ados I Materiales Capítulo 8 : Encapsulado Elena Valderrama Capítulos 1 2 3 8 9 10 Coeficiente de conductividad térmica (W/cm.ºK) Coeficiente de expansión (10-6/ºK) Constante Dieléctrica Carburo Ca bu o de Si S (SiC) (S C) , 2,2 3,7 3, 42,0 ,0 Berilia (BeO) 2,0 6,0 6,7 Alumina (Al2O3) 0,3 6,0 9,5 Dióxido de Si (SiO2) 0,01 0,5 3,9 Polimidas 0,004 - 3,5 Epoxy (PCBs) 0,003 1,5 5,0 Material 4 5 6 7 Introducción Materiales Tipos de encapsulados El conexionado Reglas de encapsulado Unión directa a substrato e híbridos MCMs Resumen Desde un punto de vista a práctico se pueden clasificar en dos grandes grupos: (1) Los materiales cerámicos (carburo de silicio, berilia y óxido de Al) y (2) los materiales plásticos (dióxido de Si, polimidas y epoxy). Los primeros son los materiales más adecuados desde el punto de vista de la disipación de calor ((allta conductividad térmica)) y del aislamiento eléctrico ((alta constante dieléctrica, sobre todo el SiC) y, aunque su coeficiente de expansión no es todo lo cercano al del silicio (2,5x10-6/ºK) que lo o que podríamos desear, lo cierto es que el de los plásticos no es mejor. El problema con los materia ales cerámicos es que el resultan caros y más difíciles de procesar que los plásticos, razón por la cual su uso queda restringido a (1) ASICs de muy alta densidad de integración en los que e la disipación de calor sea crítica y/o (2) series pequeñas. Muy frecuentemente los p proto otipos p se encapsulan p en cerámica y p posteriormente la serie se encapsula p en plástico. Los plásticos vemos qu ue disipan mucho peor el calor (coeficientes de conductividad muy por debajo de los de los cerá ámicos), pero resultan muy fáciles de procesar y económicos. Los hilos conductores deben asegurar un conexionado estable en el tiempo y eléctricamente bueno. Por tanto se les pide p que tengan: Ingeniería Informática Universidad Autónoma de Barcelona B página >>6 Diseño de Circuitos Integra ados I Materiales Capítulo 8 : Encapsulado 1. Una resistencia eléctrica e baja Elena Valderrama 2. Un coeficiente de e autoinducción bajo 3. Un coeficiente de e expansión térmica similar al del silicio, aunque esta condición es menos crítica que en el caso c del material que forma la base Capítulos 4. Que sean fáciles de soldar sobre los pads del circuito 1 2 3 8 9 10 4 5 6 7 5. Y que sean durab bles, es decir, que no sufran corrosión fácilmente La tabla siguiente muesstra algunos de los materiales más frecuentemente utilizados como hilos conductores. Introducción Mate erial Materiales Coeficiente de expansión (10-6/ºK) Resistencia (μΩ.cm) Tipos de encapsulados Plata 19,0 1,0 El conexionado Cobre 17,0 1,7 Reglas de encapsulado Aluminio 23,0 2,8 Tungsteno 4,6 5,3 Molibdeno 5,0 5,3 Unión directa a substrato e híbridos MCMs Resumen Ingeniería Informática La plata y el cobre son lo os materiales que tienen una menor resistencia, pero presentan problemas de corrosión y son incom mpatibles con las altas temperaturas a los que se somete el encapsulado cuando se utilizan cerám micas, así que el Al es el material más frecuentemente utilizado. Tiene la ventaja adicional que, pu uesto que los pads del circuito también son del mismo material, el proceso de unión a los pads es simple. Universidad Autónoma de Barcelona B página >>7 Diseño de Circuitos Integra ados I Tipos p de encapsulados p Capítulo 8 : Encapsulado Existe una verdadera mu ultitud de encapsulados (bases). Si atendemos a la forma de fijar el chip a la placa PCB podemos clasificarlos c en dos grandes grupos: Elena Valderrama 1. Encapsulados de e inserción, cuyos pines atraviesan la placa de PCB. Su principal ventaja es que pueden uttilizarse en PCBs multi-nivel. Capítulos 1 2 3 8 9 10 4 5 6 7 2. Encapsulados de e montaje superficial, en los que los chips se colocan sobre la superficie del PCB. Su prin ncipal ventaja es que la soldadura de estos chips en los PCBs de montaje superficial es fácilmente automatizable. Si atendemos a la forma a en la que se distribuyen los pines, los encapsulados se pueden clasificar en tres grupos: Introducción 1. Encapsulados “d dual-in-line” o “dual-in-parallel” (DIL o DIP), en los que los pines están ubicados en sólo dos lados del encapsulado Materiales 2. Chip-Carriers, en los que los pines se distribuyen por los 4 lados del encapsulado Tipos de encapsulados El conexionado Reglas de encapsulado Unión directa a substrato e híbridos MCMs Resumen 3. Pin-Grid-Arrays (PGAs) y Ball-Grid-Arrays (BGAs). Los PGAs son encapsulados de inserción en los que los pines se distribuyen y por toda la superficie del encapsulado., mientras que loss BGAs son su versión equivalente para montaje superficial, teniendo pequeñas “pelottitas” de material soldable distribuidas por toda la superficie del encapsulado, en lugar de pines convencionales. En todos los casos existe en versiones de inserción y versiones de montaje superficial. La figura 3 muestra algunos ejemplos de ambos tipos de encapsulados. En ella se han introducido links a figuras específica as para los tipos de encapsulado más relevantes, donde se comentan su características, sus venta ajas y sus desventajas. ver figura >> 03 El fabricante o responssable del encapsulado suministrará al diseñador información sobre los encapsulados disponible e; sus tamaños y la reglas de encapsulado. Ingeniería Informática Universidad Autónoma de Barcelona B página >>8 Diseño de Circuitos Integra ados I Tipos p de encapsulados p Capítulo 8 : Encapsulado Elena Valderrama En casi todas las figuras de los encapsulados se han incluido dimensiones físicas. A la hora de escoger el encapsulado o el diseñador deberá valorar (1) el tamaño apropiado de la cavidad (dimensiones H y G de e la figura) con respecto al tamaño del dado de silicio y (2) el tamaño apropiado del encapsulado completo con respecto a la placa sobre el que irá montado. Capítulos Mucho habría que comentar sobre las ventajas y desventajas de cada encapsulado, aquí nos vamos a limitar a esboza ar una visión muy general: 1 2 3 8 9 10 4 5 6 Introducción Materiales Tipos de encapsulados 7 1. Encapsulados co on pines por dos lados: Poseen un número relativamente bajo de pines (hasta 48 o 64). Resultan fáciles de testear una vez montados en placa. Existen versiones de inserción (DIL L o DIP) y de montaje superficial (SOP). 2. Encapsulado con n pines por sus 4 lados: Poseen un número mayor de pines (hasta 84). Existen versione es de inserción y existen diferentes versiones de montaje superficial dependiendo de la forma de los pines (gull-wing, J-leaded, leadless,..). 3. Encapsulado con n pines en toda su superficie: Son los encapsulado que permiten el mayor número de pines (313), aunque resultan difíciles de comprobar una vez montados en placa. Existen versioness de inserción (PGA) y de montaje superficial (BGA). El conexionado Reglas de encapsulado Unión directa a substrato e híbridos MCMs 4. Finalmente menccionar que hay en el mercado muchos otros encapsulados que tratan de cubrir algunas necesidades n de espacio muy concretas, como por ejemplo los “flatpackages”, que son s encapsulado similares al DIP en los que los pines son muy largos y salen horizontale es, esto es, sin doblarse hacia abajo, pensando en montarlo verticalmente respecto a la placca, etc. Resumen Ingeniería Informática Universidad Autónoma de Barcelona B página >>9 Diseño de Circuitos Integra ados I El conexionado Capítulo 8 : Encapsulado Una vez se dispone del dado de Silicio y de la base del encapsulado, lo primero que se hace es pegar el dado a la base,, evidentemente por la parte del dado que no contiene el circuito. La unión se suele hacer con una a pasta conductora, y se aprovecha esta unión para polarizar a tierra el substrato. El siguiente pa aso es la conexión entre los pads del dado y los pines de la base. Elena Valderrama Capítulos 1 2 3 8 9 10 4 5 6 Introducción Materiales Tipos de encapsulados El conexionado 7 “wire-bonding” La unión entre pads del circuito c y pines del encapsulado se realiza mediante hilos conductores (ver figura 4.a). Esta unión n (en inglés wire-bonding), a diferencia de la soldadura, se realiza directamente entre el hilo conductor y el material del pad (Al) y del pin, sin necesidad de un material de unión como el estaño. Para ello el extremo del hilo conductor y el material del pad se funden parcialmente utilizando ultrasonidos y calor. En el extremo del hilo se forma una pequeña pelota de material fundid do que se fuerza mecánicamente sobre el pad, quedando ambos unidos cuando los dos materiales se re-solidifican totalmente. El mismo proceso se repite en el extremo del pin, entre éste y el hilo (figura 4.b). Las máquinas de wire-bo onding son capaces de hacer este proceso una y otra vez, para cada una de las parejas pin-pad de el chip. Reglas de encapsulado ver figura >> 04 Unión directa a substrato e híbridos MCMs Resumen Ingeniería Informática Es muy importante que las uniones hilo-pad y hilo-pin sean no sólo mecánicamente estables sino también muy homogéne eas en toda la superficie de contacto. De no ser así se crean microcavidades que distorsion nan el paso de corriente creando pequeñas corrientes de fuga que a su vez (1) provocan consumoss indeseados y (2) calientan la superficie de contacto. Asimismo es importante asegurar que e la resistencia y la capacidad asociada a la unión sean lo menor posibles. B Universidad Autónoma de Barcelona página >>10 Diseño de Circuitos Integra ados I El conexionado Capítulo 8 : Encapsulado Para asegurar todos esttos parámetros es necesario un control preciso no sólo de la temperatura, ultrasonidos y el tiempo de aplicación de éstos, sino también de la longitud del hilo, la altura que alcanza, el ángulo con el que el hilo llega al pad, etc. (figura 4.c). El control de todos estos factores justificarán algunas de la as “reglas de encapsulado” que veremos más adelante. Elena Valderrama Capítulos 1 2 3 8 9 10 4 5 6 Introducción Materiales Tipos de encapsulados El conexionado Reglas de encapsulado Unión directa a substrato e híbridos MCMs 7 El tape-automatic c-bonding o TAB La técnica de conexionad do explicada hasta ahora resulta lenta cuando se trata de encapsular chips a nivel industrial. Una altternativa de uso frecuente es el TAB. El TAB es una tecnolog t l gía í de d conexión ió entre t pines i y pads d que usa delgadas d l d pistas i t d metal de t l depositadas (grabadas) sobre una película de polímero, que se colocan de manera que permitan realizar todas las conexio ones pad-pin de un chip en (prácticamente) un sólo paso. La figura 5.a muestra un n cinta utilizada para el TAB. Las pistas de metal, como se puede ver en la figura 5.b, quedan “flotan ntes” en aquellas zonas en las que se ha eliminado el polímero (marcadas en la figura). g ) En p primerr lugar g se ensambla el dado de silicio colocando una cierta cantidad de material conductor sobre e los pads a modo de pequeñas pelotas (son los llamados bumps en la figura) y se hacen coinciidir éstos con los extremos de las pistas metálicas que quedan en la zona central de la estructura utilizada para el TAB (ver figura 5.c). Una vez unido el dado de silicio, el conjunto formado por ésste más la cinta-TAB se llevan a la base del encapsulado, haciendo ahora coincidir la zona de lass pistas metálicas que han quedado flotantes debido al hueco periférico sobre las áreas de conexxión de los p pines y se p procede igual. g Resumen ver figura >> 05 Ingeniería Informática Universidad Autónoma de Barcelona B página >>11 Diseño de Circuitos Integra ados I El conexionado Capítulo 8 : Encapsulado Por supuesto la explica ación expuesta se ha simplificado extraordinariamente. Los procesos de bonding a través del TA AB tiene una gran complejidad, y la alineación dado-cinta TAB y base del encapsulado-cinta TAB debe realizarse con gran precisión, pero lo que se desea aquí es simplemente dar la idea de esta técnica. Elena Valderrama Capítulos 1 2 3 8 9 10 4 5 6 Introducción Materiales Tipos de encapsulados El conexionado 7 El “flip-chip” El flip-chip es una técnica de conexionado introducida por IBM en la cual (1) se depositan unas aterial conductor sobre cada uno de los pads del circuito (bumps) tal como pequeñas “bolas” de ma se hacía en el TAB; (2) se s coloca la pastilla, cara abajo (con el circuito “mirando” mirando hacia la base del encapsulado) con los bu umps coincidiendo con pads del circuito y (3) se sueldan todas las parejas de pads y pines (pad+bu ump+pin) simultáneamente. Comparado con el wire-b bonding o el TAB, el flip-chip produce unos conexionados más compactos y con unas muy buenas características eléctricas en lo que se refiere a resistencia e inductancia de las conexiones. En la figura 6 se puede ver un esquema del flip-chip frente a la técnica convencional de unión por p wire-bonding, así como el detalle de tres bumps colocados sobre los pads correspondientes. Reglas de encapsulado ver figura >> 06 Unión directa a substrato e híbridos MCMs Resumen nveniente de que los bumps deben depositarse sobre la oblea y no a nivel El flip-chip tiene el incon de la pastillas ya cortad da. Otro problema de esta técnica, por otro lado muy buena, es que la disposición final del circu uito dificulta la disipación de calor. Esta técnica, utilizada originariamente como ya se ha dicho por IBM en el famoso IBM-360 y en circuitos híbridos, ha sido o mejorada y se usa hoy en día en los MCMs (como se verá más adelante) y en la unión directa a su ubstrato. Ingeniería Informática Universidad Autónoma de Barcelona B página >>12 Diseño de Circuitos Integra ados I Reglas g de encapsulado p Capítulo 8 : Encapsulado La técnica estándar que e se utiliza para el encapsulado de ASICs es el wire-bonding, y sólo en casos muy específicos es e necesario utilizar alguna de las otras técnicas. Así, en este curso de introducción al diseño de ASICs, las reglas de encapsulado las referiremos a esta técnica convencional. Elena Valderrama Capítulos 1 2 3 8 9 10 4 5 6 Introducción Materiales Tipos de encapsulados El conexionado 7 Una vez seleccionado el e encapsulado el diseñador puede definir la relación pad-pin exacta que desea y que mejor se va a adaptar a la placa sobre la que irá montada. No todas las relaciones entre pines y pads son posibles como es fácil de entender; p.e., las relaciones que provoquen el cruce de alguna pareja de cables de conexionado, o conexionados muy largos y por tanto con resistencias e inductanccias altas no se podrán permitir. Para solventar estas dificultades, el fabricante o responsable e del encapsulado suministra un conjunto de “reglas de encapsulado” que la asignación pines-p pads propuesta por el diseñador deberá cumplir. Se llaman bondpads a los l pads del circuito (dado de silicio) sobre los cuales se unirán los hilos y, similarmente, se llaman bondpines a las áreas sobre la base del encapsulado sobre las que se unirán los hilos proceden ntes del dado (figura 7.a). La idea general de las reglas de encapsulado es sencilla: Conseguir distrribuciones homogéneas de los hilos sin que estos se solapen ni sean demasiado largos. largos A títtulo de ejemplo, ejemplo la figura 7.b 7 b muestra un diagrama de encapsulado (bonding-diagram) corrrecto. Reglas de encapsulado ver figura >> 07 Unión directa a substrato e híbridos MCMs Resumen No vamos a ver exhaustivamente todas las reglas de encapsulado porque, entre otras cosas, d dependen d del d l fabricante f bi concreto con ell que se esté é trabajando; b j d pero síí vamos a mostrar algunas l de ellas. Así por ejemplo o: 1. Los bondpines se e distribuyen alrededor de los 4 lados de la cavidad donde se posiciona el dado de silicio y se s hallan numerados. El bondpin-1 está indicado por un bondpad de forma distinto al resto, y el resto de pines se cuentan en el sentido contrario al de las agujas del relojj ((ver 7.b). ) Ingeniería Informática Universidad Autónoma de Barcelona B página >>13 Diseño de Circuitos Integra ados I Reglas g de encapsulado p Capítulo 8 : Encapsulado Elena Valderrama Capítulos 1 8 2 9 3 4 5 6 10 Introducción 7 2. La base del enca apsulado debe haberse seleccionado de forma que, una vez colocado el dado de silicio en e su interior, la longitud de los hilos necesarios para la conexión sea lo menor posible. El E dado tampoco puede quedar totalmente pegado a las paredes de la cavidad porque la máquina de bonding requiere un mínimo espacio para maniobrar. En consecuencia el tamaño de la cavidad del encapsulado fija no sólo el tamaño máximo del consecuencia, dado que se pue ede colocar en su interior, sino también su tamaño mínimo (dados muy grandes no caben n; dados muy pequeños requieren hilos de conexión demasiado largos). 3. Los hilos no debe en (1) ser muy largos (puesto que provocan Rs, Cs y Ls desaconsejadas), (2) no pueden qu uedar demasiado elevados y (3) no pueden cruzarse. Esto limita qué pads pueden conectarse a qué pines, de modo que se suele aconsejar seguir la siguiente reglas para definir las conexiones c pad-pin: El dado se debe partir (virtualmente) en 8 sectores como indica la fig gura 8.a. Sólo están permitidas las uniones que afecten a pads y pines que estén en el mismo sector. Materiales ver figura >> 08 Tipos de encapsulados El conexionado Reglas de encapsulado 4. Los hilos, como ya y se ha dicho, no se pueden cruzar entre sí; y los ángulos formados por la línea que une ca ada bondpad con su bondpin y el lado del dado (ver figura 9.b) debe ser mayor a 45º. Unión directa a substrato e híbridos ver figura >>09 MCMs Resumen Ingeniería Informática Cada fabricante añade las l reglas que cree oportuno y que mejor se adaptan a su tecnología de encapsulado. Es respon nsabilidad del diseñador asegurarse que su elección de encapsulado y la asignación entre pines y pads cumplen las reglas de encapsulado. Universidad Autónoma de Barcelona B página >>14 Diseño de Circuitos Integra ados I Unión directa a substrato e híbridos Capítulo 8 : Encapsulado En casos muy específico os será necesario colocar el dado de silicio directamente sobre la placa de PCB, sin encapsulado protector. p Tanto el wire-bonding, el TAP o el flip-chip son técnicas que pueden utilizarse para la a unión directa a substrato. Elena Valderrama Capítulos 1 2 3 8 9 10 4 5 6 7 Los encapsulados híbrid dos (ver figura 10) utilizan un substrato fino para fijar sobre él distintos dispositivos; ASICs, circu uitos integrados estándar y componentes más sencillos como capacidades o resistencias minúscu ulas. Este substrato puede ser la base de un encapsulado que posteriormente se sellará á y quedará, a la vista del diseñador, como un único chip. ver figura >> 10 Introducción Materiales Tipos de encapsulados El conexionado Reglas de encapsulado Unión directa a substrato e híbridos MCMs Resumen Ingeniería Informática Universidad Autónoma de Barcelona B página >>15 Diseño de Circuitos Integra ados I MCMs ((Multi Chip p Modules)) Capítulo 8 : Encapsulado Los MCMs son el último o nivel de evolución de los híbridos, en los que se han introducido dos conceptos/técnicas adicionales: Elena Valderrama 1. Se ha ampliado el rango de substratos utilizables sobre los cuales colocar los dados de silicio. Uno de esstos substratos merece algún comentario especial: El Silicio. Capítulos 1 2 3 8 9 10 4 5 6 Introducción Materiales Tipos de encapsulados El conexionado Reglas de encapsulado Unión directa a substrato e híbridos MCMs 7 Los llamados MC CMs activos utilizan como substrato el propio silicio, colocando sobre él dados de distinta as procedencias (p.e. algún/os ASIC/s, algún/os CIs estándar como podría ser un microcontrolador, componentes básicos e incluso se podría pensar en introducir adores integrados), encapsulándose finalmente juntos. La gran ventaja de sensores o actua utilizar silicio como c substrato es que sobre él pueden integrarse (con técnicas fotolitográficas) pistas p metálicas y también otros dispositivos activos (p.e., (p e transistores). transistores) Estos pequeños circuitos integrados sobre la base de silicio pueden constituir verdaderas “conexiones inteligentes” entre los distintos circuitos integrados en los dados o, p.e. se puede integrar so obre el substrato circuitería para el auto-test de los componentes. 2. Sobre los circuito os integrados, y tras depositar la última capa de pasivación, se deposita una capa de material m aislante (polímeros) por fotolitografía y sobre ella se colocan pequeños cuadra ados de Al que harán las funciones de pads. Gravando la capa de aislante se pueden conecctar estos pads a pistas del circuito. De este modo se puede utilizar toda la superficie del dad do de silicio para colocar pads, aumentando espectacularmente el número de señales que se s puede entrar/sacar del circuito sin aumentar la superficie del mismo. La figura 11 muestra un esquema del conexionado de un MCM. En la figura 12 puede verse la foto de un MCM y la placa a la que substituye. substituye Resumen ver figura >> 11 ver figura >> 12 Ingeniería Informática Universidad Autónoma de Barcelona B página >>16 Diseño de Circuitos Integra ados I Resumen Capítulo 8 : Encapsulado Elena Valderrama Una vez fabricados y co ortados los dados de silicio que constituyen el circuito es necesario fijarlos sobre algún tipo de base e que permita conectarlo con el resto de los componentes electrónicos del sistema a la vez que le sirva de protección y asegure una disipación térmica conveniente. Esta base toma la forma, en la a gran mayoría de los casos, de un encapsulado. Capítulos El diseñador puede opta ar entre una amplia gama de encapsulados con características particulares. La elección debe basarse en: 1 2 3 8 9 10 4 5 6 7 1. Capacidad de dissipación de calor (encapsulados plásticos o cerámicos) 2. Número de piness: Ordenados de menor a mayor y número de p pines: DIL o DIP;; chip-carries; p ; PGAs o BGAs. Introducción 3. Del tamaño de la a cavidad y del dado de silicio Materiales 4. Del tamaño tota al del encapsulado y el espacio disponible en la placa en la que vaya montado. Tipos de encapsulados El conexionado Reglas de encapsulado Unión directa a substrato e híbridos MCMs Resumen Ingeniería Informática Una vez seleccionado ell encapsulado el diseñador puede definir la relación entre pads del circuito y pines del encapsulado,, siempre de acuerdo con la reglas de encapsulado. Existe la posibilidad de introducir i varios dados distintos sobre una misma base, constituyendo los que se conoce como mó ódulo multi-chip o MCM (Multi-Chip-Module). Los MCMs permiten colocar sobre una misma base circuitos estándar (p.e., memorias), ASICs, sensores y/o actuadores, etc, fabricados con diferentess tecnologías. Finalmente, otra opción en caso de que la disponibilidad de espacio en el sistemas sea mínima es el direct-bonding o unión n directa del dado sobre la placa de circuito. Universidad Autónoma de Barcelona B página >>17 Diseño de Circuitos Integra ados I Figura 1 Encapsulado Proceso tecnológico Corte Layout y Pastillas (dice) Generación de las máscaras ... etc Máscaras (una por nivel) Máscara difusiones dif i P Máscara de e área activa Ingeniería Informática Chip B Universidad Autónoma de Barcelona Oblea de Si página >>18 Diseño de Circuitos Integra ados I Figura 2 Encapsulado Dado de Si (ASIC C) Base del encapsulado Hilo (wire-bonding) p pin Ingeniería Informática B Universidad Autónoma de Barcelona página >>19 Diseño de Circuitos Integra ados I Encapsulados de inserción ó Encapsulados de montaje superficial Figura 3 ir a PDI IP>> ir a SOP>> ir a LCC.1>> ir a LCC.2>> ir a PGA A>> ir a VSQF>> y : Otros: Ball-Grid-Array Ingeniería Informática B Universidad Autónoma de Barcelona ir a BGA>> página >>20 Diseño de Circuitos Integra ados I Figura 3.1 Encapsulado PDIP Ingeniería Informática B Universidad Autónoma de Barcelona página >>21 Figura 3.2 Ingeniería Informática Diseño de Circuitos Integra ados I Encapsulado PGA B Universidad Autónoma de Barcelona página >>22 Diseño de Circuitos Integra ados I Figura 3.3 Detalle de los pines (tipo “Gull-wing” o “ala de gaviota” Encapsulado SOP Ingeniería Informática B Universidad Autónoma de Barcelona página >>23 Diseño de Circuitos Integra ados I Encapsulado LCC (“Leadless Chip Carrier”) Figura 3.4 Detalle de los pines (internos). De ahí el nombre de “leadless”. Ingeniería Informática B Universidad Autónoma de Barcelona página >>24 Diseño de Circuitos Integra ados I Encapsulado de tipo “Chip Chip-Carrier” (LCC) Figura 3.5 “J-leaded” Detalle de los pines en forma de J (J-leaded) Existen encapsuladoss simulares con formas de pines diferentes: Ingeniería Informática Universidad Autónoma de Barcelona B Ver foto>> página >>25 Diseño de Circuitos Integra ados I Figura 3.6 Detalle del pin de tipo “butt” Ingeniería Informática Universidad Autónoma de Barcelona B página >>26 Diseño de Circuitos Integra ados I Figura 3.7 Enc capsulado VSQF “Gull Gull-wing” Ingeniería Informática B Universidad Autónoma de Barcelona página >>27 Diseño de Circuitos Integra ados I Encapsulado BGA Figura 3.8 Ingeniería Informática Universidad Autónoma de Barcelona B página >>28 4.a a : Wire-bonding g Figura 4 Diseño de Circuitos Integra ados I hilo conector bondpin 4.c : De etalle de una co onexión Base del encapsulado Ingeniería Informática bondpad bondpad Dado de Si S bond dpin 4.b : Proceso de ball-bonding B Universidad Autónoma de Barcelona página >>29 Diseño de Circuitos Integra ados I TAB : Tape Automatic Bonding Figura 5 5.a Partes flotantes de la pistas de metal hu c s en huecos n ell film 5.c : proceso 5.b Ingeniería Informática B Universidad Autónoma de Barcelona página >>30 Diseño de Circuitos Integra ados I Figura 6 6.a Unión directa a substrato s FlipFlip -chip 6.b Detalle de 3 “bumps” Ingeniería Informática Universidad Autónoma de Barcelona B página >>31 Diseño de Circuitos Integra ados I Figura 7 Bondpad Bondpin 7.a: Bond Bond-pad y Bond Bond-pin Ingeniería Informática B Universidad Autónoma de Barcelona 7.b: Ejemplo de asignación correcta página >>32 Diseño de Circuitos Integra ados I Figura 8 8 8.a: P Particionado ti i d en sectores t Ingeniería Informática B Universidad Autónoma de Barcelona 8 b A 8.b: Asignación i ió correcta t página >>33 Diseño de Circuitos Integra ados I Figura 9 8.a: Regla sobre los ángulos Ingeniería Informática B Universidad Autónoma de Barcelona 8.b: Asignación incorrecta página >>34 Diseño de Circuitos Integra ados I Figura 10 Microsistema donde se puede observar dos dados unidos directamente a substrato (direct-bond ding) Ingeniería Informática B Universidad Autónoma de Barcelona Híbrido: Distintos tipos de componentes encapsulados sobre una misma base página >>35 Diseño de Circuitos Integra ados I Figura 11 Gentileza del Dr. Cabruja; CNM-Barcelona Esqu uema de un encapsulado MCM Ingeniería Informática B Universidad Autónoma de Barcelona página >>36 Diseño de Circuitos Integra ados I Figura 12 Gentileza del Dr. Cabruja; CNM-Barcelona MC CM y circuito al que sustituye Ingeniería Informática B Universidad Autónoma de Barcelona página >>37 Ingeniería Informática Diseño de Circuitos Integra ados I Universidad Autónoma de Barcelona B