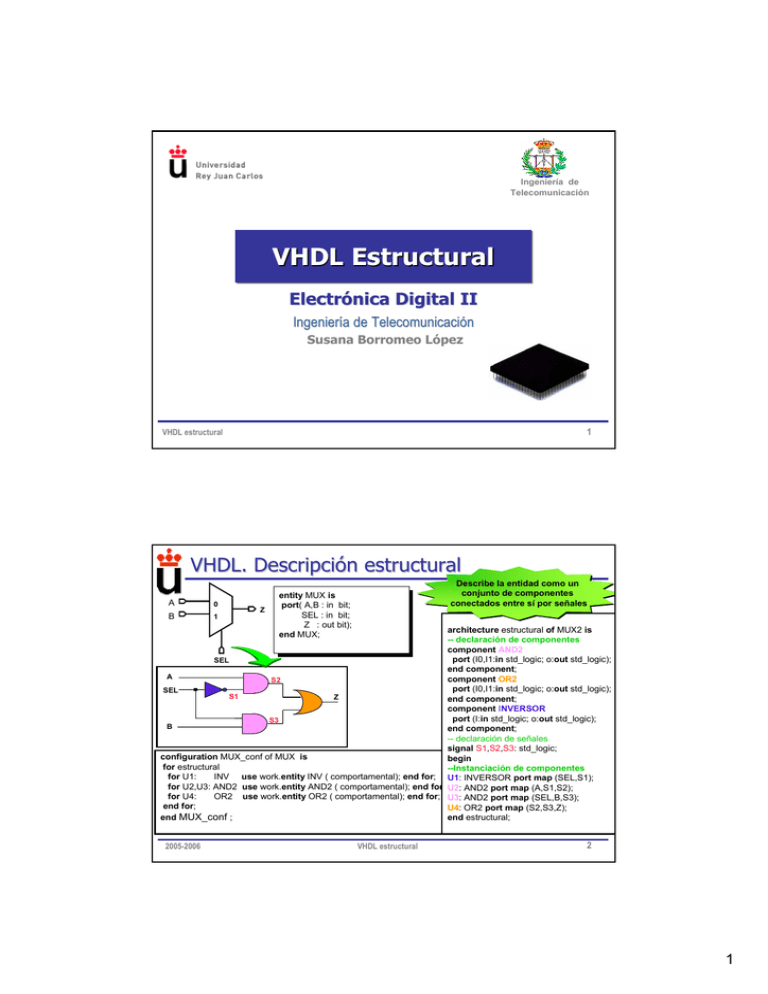

VHDL Estructural VHDL Estructural

Anuncio

Ingeniería de Telecomunicación VHDL Estructural Electrónica Digital II Ingeniería de Telecomunicación Susana Borromeo López 1 VHDL estructural VHDL. Descripción estructural E0 A 0 B E1 1 Z Describe Describe la la entidad entidad como como un un conjunto conjunto de de componentes componentes conectados conectados entre entre sí sí por por señales señales entity entityMUX MUXisis port( port(A,B A,B: :inin bit; bit; SEL SEL: :inin bit; bit; ZZ : :out outbit); bit); end endMUX; MUX; architecture estructural of MUX2 is -- declaración de componentes component AND2 port (I0,I1:in std_logic; o:out std_logic); SEL end component; A component OR2 S2 port (I0,I1:in std_logic; o:out std_logic); SEL S1 Z end component; component INVERSOR port (I:in std_logic; o:out std_logic); S3 B end component; -- declaración de señales signal S1,S2,S3: std_logic; configuration MUX_conf of MUX is begin for estructural --Instanciación de componentes for U1: INV use work.entity INV ( comportamental); end for; U1: INVERSOR port map (SEL,S1); for U2,U3: AND2 use work.entity AND2 ( comportamental); end for; U2: AND2 port map (A,S1,S2); for U4: OR2 use work.entity OR2 ( comportamental); end for; U3: AND2 port map (SEL,B,S3); end for; U4: OR2 port map (S2,S3,Z); end MUX_conf ; end estructural; 2005-2006 VHDL estructural 2 1 VHDL. Descripción estructural configuration identificador of identificador_entidad is for identificador arquitectura for ref_componente: identificador_componente use librería.identificador_entidad(identificador_arquitectura) end for; ….. end for; end identificadir_configuracion ; 2005-2006 3 VHDL estructural VHDL. Descripción estructural Modelar un divisor de 10 y basándose en ese módulo realizar un divisor por 1000 CE CE Clk100_enable DIV10 CE Clk10_enable DIV10 CE DIV10 myClk1 Clk1000 reset reset reset reset 2005-2006 VHDL estructural 4 2 architecture Behavioral of divisor1000 is -- Declaración componente COMPONENT divisor10 PORT( reset : IN std_logic; clk10 : IN std_logic; CE : IN std_logic; clk1 : OUT std_logic entity divisor1000 is ); Port ( clk1000 : in std_logic; END COMPONENT; reset : in std_logic; -- Declaración de señales CE : in std_logic; -- Señal de habilitacion de cuenta signal clk10_enable: std_logic; myclk1 : out std_logic); signal clk100_enable: std_logic; end divisor1000; begin -- Instanciación del componente Inst_divisor10: divisor10 PORT MAP( reset => reset , clk10 => clk1000, CE => '1', clk1 => clk100_enable ); -- Instanciación del componente Inst_divisor100: divisor10 PORT MAP( reset => reset, clk10 => clk1000, CE => clk100_enable, clk1 => clk10_enable ); -- Instanciación del componente Inst_divisor1000: divisor10 PORT MAP( reset => reset , clk10 => clk1000, CE => clk10_enable, clk1 => myclk1 ); 5 2005-2006 VHDL estructural end Behavioral; Descripción estructural 3