MÁQUINAS DE ESTADO FINITO CON FLIP–FLOP TIPO JK Diseñe

Anuncio

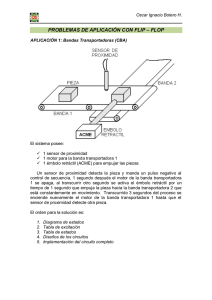

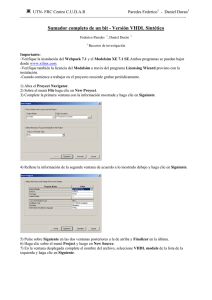

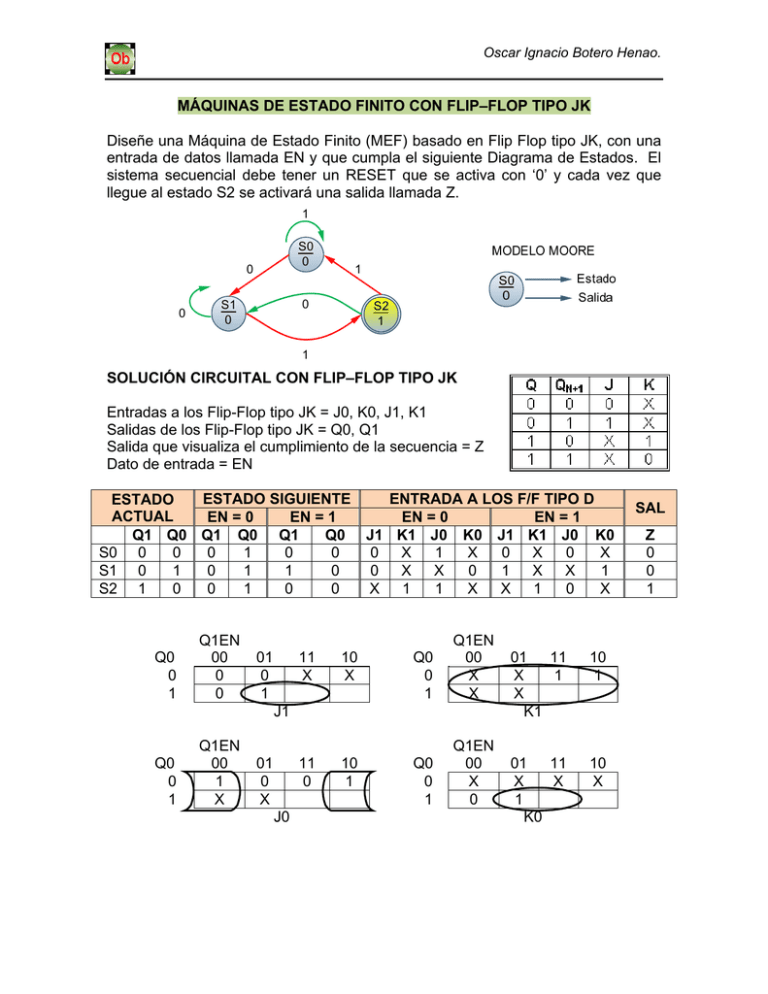

Oscar Ignacio Botero Henao. MÁQUINAS DE ESTADO FINITO CON FLIP–FLOP TIPO JK Diseñe una Máquina de Estado Finito (MEF) basado en Flip Flop tipo JK, con una entrada de datos llamada EN y que cumpla el siguiente Diagrama de Estados. El sistema secuencial debe tener un RESET que se activa con ‘0’ y cada vez que llegue al estado S2 se activará una salida llamada Z. 1 S0 0 0 0 1 0 S1 0 S2 1 1 SOLUCIÓN CIRCUITAL CON FLIP–FLOP TIPO JK Entradas a los Flip-Flop tipo JK = J0, K0, J1, K1 Salidas de los Flip-Flop tipo JK = Q0, Q1 Salida que visualiza el cumplimiento de la secuencia = Z Dato de entrada = EN ESTADO SIGUIENTE ESTADO ACTUAL EN = 0 EN = 1 Q1 Q0 Q1 Q0 Q1 Q0 S0 0 0 0 1 0 0 S1 0 1 0 1 1 0 S2 1 0 0 1 0 0 ENTRADA A LOS F/F TIPO D EN = 0 EN = 1 K1 J0 K0 J1 K1 J0 K0 X 1 X 0 X 0 X X X 0 1 X X 1 1 1 X X 1 0 X J1 0 0 X Q0 0 1 Q1EN 00 0 0 01 0 1 11 X 10 X Q0 0 1 Q1EN 00 X X Q0 0 1 Q1EN 00 X 0 J1 Q0 0 1 Q1EN 00 1 X 01 0 X 11 0 10 1 J0 01 11 X 1 X K1 10 1 01 11 X X 1 K0 10 X SAL Z 0 0 1 Oscar Ignacio Botero Henao. Q0 0 1 Q1 0 1 1 X Z 1 0 Σ 0 1 Σ 0 Σ Σ 1 Ecuación del F/F tipo JK: Q n 1 J Q K Q DISEÑO EN PROTEUS MIXTO: FLIP FLOP TIPO JK – SECUENCIAL Y ECUACIONES BOOLEANAS library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Moore1_MIXJK is ‐‐ Entidad Port ( EN : in STD_LOGIC; ‐‐ Entrada del dato, 1 bit 2 Oscar Ignacio Botero Henao. CLK : in STD_LOGIC; ‐‐ Reloj manual RESET : in STD_LOGIC; ‐‐ Reset del sistema Z : out STD_LOGIC; ‐‐ Salida de cumplimiento de secuencia Q0 : inout STD_LOGIC; ‐‐ Salida Q0 del F/F 0 Q1 : inout STD_LOGIC); ‐‐ Salida Q1 del F/F 1 end Moore1_MIXJK; ‐‐ Fin de la entidad architecture Comportamiento of Moore1_MIXJK is ‐‐ Arquitectura SIGNAL J0,K0,J1,K1: STD_LOGIC:='0'; ‐‐ Señales internas de las entradas de los F/F SIGNAL Qt0,Qt1:STD_LOGIC:='0'; ‐‐ Señales internas temporales begin ‐‐ Comienza ‐‐ ECUACIONES COMBINACIONALES (Mapas K) J0 <= NOT EN; ‐‐ Entrada J0 del F/F 0 K0 <= Q0 AND EN; ‐‐ Entrada K0 del F/F 0 J1 <= Q0 AND EN; ‐‐ Entrada J1 del F/F 1 K1 <= '1'; ‐‐ Entrada K1 del F/F 1 ‐‐ PROCESO SECUENCIAL SEQ:PROCESS (CLK,RESET,EN) ‐‐ Proceso Secuencial SEQ BEGIN ‐‐ Comienza IF RESET='0' THEN ‐‐ Si hay RESET, entonces Qt0 <= '0'; ‐‐ Lleve '0' a la salida Q0 Qt1 <= '0'; ‐‐ Lleve '0' a la salida Q1 ELSE ‐‐ Si no IF CLK'EVENT AND CLK='1' THEN ‐‐ Si hay evento y flanco UP, entonces IF EN='0' THEN ‐‐ Si EN está en '0', entonces Qt0 <= (J0 AND NOT Q0) OR (NOT K0 AND Q0); ‐‐ Ec. del F/F JK Qt1 <= (J1 AND NOT Q1) OR (NOT K1 AND Q1); ‐‐ Ec. del F/F JK ELSE ‐‐ Si no Qt0 <= (J0 AND NOT Q0) OR (NOT K0 AND Q0); ‐‐ Ec. del F/F JK Qt1 <= (J1 AND NOT Q1) OR (NOT K1 AND Q1); ‐‐ Ec. del F/F JK END IF; ‐‐ Fin si END IF; ‐‐ Fin si END IF; ‐‐ Fin si END PROCESS SEQ; ‐‐ Fin del Proceso Secuencial SEQ Q0 <= Qt0; ‐‐ Lleve lo que tenga Qt0 a la salida Q0 del F/F 0 Q1 <= Qt1; ‐‐ Lleve lo que tenga Qt1 a la salida Q1 del F/F 1 Z <= Q1 AFTER 10ns; ‐‐ Lleve lo que tenga Q1 después de 10ns a la salida Z end Comportamiento; ‐‐ Fin de la arquitectura 3 Oscar Ignacio Botero Henao. MODELADO ESQUEMÁTICO EN XILINX CON F/F TIPO JK 4