FPGAs - UNICEN

Anuncio

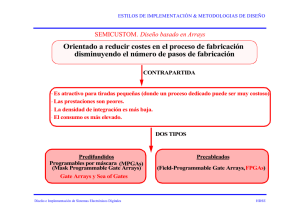

Técnicas de Programación Hardware: CAD para FPGAs y CPLDs Clase 4: FPGAs Por: Nelson Acosta & Daniel Simonelli UNICEN - Tandil - 1999 1 Implementación de Sistemas • Procesador convencional. Economico, conjunto fijo de instrucciones, entonces lento. • Microcontrolador dedicado. Economico, pero lento por igual causa que procesador. • Circuito dedicado a medida. Caro, pero se obtienen buenas velocidades, aunque cualquier modificación es muy difícil de realizar. 2 Circuito dedicado a medida • Transistores. Copiable. • Integrados estandar. serie 74xxx. Copiable. • ‘Glue-Logic’, se hacen placas grandes con varios integrados. Copiable. • ASIC. Extremadamente rápido y caro, totalmente a medida. No COPIABLE. Estructura no modificable. 3 ASIC. Puntos a tener en cuenta. • Costo de diseño. El diseño debe realizarlo una empresa con las librerías del fabricante. • Costo de implementación. El fabricante ejecuta verificaciones sobre el diseño, para detectar si cumple los requerimientos. • Confección de mascaras en tecnología propietaria. 4 Que es una FPGA ? Dispositivo lógico de propósito general programable por los usuarios, compuesto de bloques lógicos comunicados por conexiones programables. El tamaño, estructura y número de bloques; y la cantidad y conectitividad de las conexiones varian en las distintas arquitecturas. 5 • Ventajas: Costo bajo de las herramientas, programación en minutos, y bajo riesgo del proyecto (como consecuencia del bajo costo), verificación efectiva del diseño mediante simuladores o en el chip, bajo costo del testing, ventajas de ser un producto de fabricación estándar, y ventajas del ciclo de vida de una aplicación. • Desventajas: tamaño y costo del chip, velocidad del circuito, y metodología de diseño ad-hoc. 6 Evolución de dispositivos programables • PROM (Programmable Read-Only Memory). LUT • Mask Programmable. • Field Programmable. • EPROM (Eraseable Programmable Read-Only Memory). • EEPROM (Electrically Eraseable Programmable Read-Only Memory). LUT • PLD (Programmable Logic Device). (And-Or) • PAL (Programmable Array Logic). (And-Or). Cableado fijo • PLA (Programmable Logic Array). (And-Or). Cabl. progr. • MPGA (Mask Programmable Gate Array). Arreglo 2D de transist. • FPGA (Field Programmable Gate Array). (Xilinx’85) 7 FPGAs programables por SRAM • Estructura: arreglo bidimensional de bloques lógicos rodeados por conexiones configurables. Una familia tiene identicos bloques lógicos y conexiones, pero difieren en el tamaño del arreglo. • Tecnología de programación: Se programa por la carga de celdas de memoria de configuración, que controlan la lógica e interconexiones. No hay área de memoria separada. • Características: Volatilidad, Memoria externa, Reprogra-mabilidad, Calidad, Proceso de fabricación estandar y Bajo consumo. 8 Arquitectura del dispositivo (1) El CHIP de la FPGA: • Arreglo 2d de CLBs rodeados por IOB. • Tiene circuitería para la configuración. • La palabra de configuración se carga en las celdas de memoria de configuración, formando las funciones lógicas en una tabla y controlan las interconexiones en PIPs y multiplexores. 9 Arquitectura del dispositivo (2) Bloque lógico CLB (Configurable Logic Block): • Contiene una tabla de n entradas, • Esta rodeado por canales del cableado (varios segmentos). • La salida del CLB es conectada a segmentos cableados usando PIPs. • Si el bloque no se usa, todos los PIPs se desconectan y el bloque no genera señal a ningún segmento, y el segmento puede ser usado para otras señales. 10 Arquitectura del dispositivo (3) 11 Arquitectura del dispositivo (4) Un Bloque está formado por (a): • Tabla: • Implementa lógica combinacional 2n por cada celda de memoria. Usando n entradas 2^2n. • Se programa cargando el patron de bits de la tabla de verdad de la función. • Las entradas no usadas se mantienen a nivel bajo o se duplica la lógica. • Todas las funciones tienen el mismo retraso. El place&route toma ventaja de la equivalencia entre pines. 12 Arquitectura del dispositivo (5) Un Bloque está formado por (b): • Punto de Interconexión Programables (PIP): • Controlan la conexión de los segmentos cableados en las interconexiones programables. • Es un pass-transistor controlado por la memoria de configuración. • Multiplexor: • Unico ruteo unidireccional. • Las llaves construidas con multiplexores ahorran espacio. 13 Diseño con SRAM-FPGA (1) • Densidad y velocidad. • Densidad es la cantidad de lógica usable por unidad de área del chip. • Velocidad es el retraso necesario para implementar una función. • Tamaño y ruteabilidad. • Más PIPs brinda más opciones de ruteo. • Cada PIP incluye una celda de memoria. 14 Diseño con SRAM-FPGA (2) • Velocidad y ruteabilidad. • Cada segmento de conexión se carga por la capacidad del pass-transistor de todas las potenciales conexiones que pueden hacerse. • Tamaño de bloque y estructura. • Compuertas versus LUT. • Para alta velocidad se prefieren tablas más grandes. • Estimación de la capacidad. • Las FPGAs tienen 3 recursos: lógica, I/O y ruteo. • El diseño debe caber en todos los parámetros. 15 Diseño con SRAM-FPGA (3) Proceso de Implementación: • Definición del diseño inicial (vhdl, esquemas). • Optimización lógica (de las ecuaciones). • Mapeo tecnologico (adapta ecuaciones a tecnología). • Ubicación (asigna la ubicación física a las ecuaciones). • Ruteo (conecta todas las ecuaciones). • Programación de la unidad (genera configuración). 16 Diseño con SRAM-FPGA (4) Programación de una SRAM -FPGA: • Configuración. Carga en serie para minimizar el número de pines. Conexión en cadena para la configuración de varias FPGAs. • Relectura. Se permite la lectura del contenido completo del chip, incluido el contenido de los FF internos. • Seguridad. Bit para evitar la re-ingeniería del diseño. 17 FPGAs Disponibles en el Mercado Por las formas de programación: Static RAM, Antifusibles y (E)EPROM. 18 Fin 19