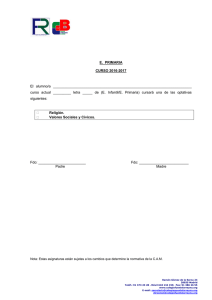

especialidades: electrónica curso: 4º profesorado

Anuncio

HOJA 1 DE 9 DEPARTAMENTO DE TECNOLOGÍA ELECTRÓNICA ASIGNATURA: LABORATORIO DE SISTEMAS DIGITALES Universidad de Vigo PROGRAMABLES II Universidad de Vigo CENTRO: ESCUELA TÉCNICA TELECOMUNICACIÓN CÓDIGO: 305010769 CURSO ACADÉMICO: 05-06 SUPERIOR DE INGENIEROS TITULACIÓN: INGENIERO DE TELECOMUNICACIÓN ESPECIALIDADES: ELECTRÓNICA CURSO: 4º TIPO DE ASIGNATURA: OBLIGATORIA ESPECIALIDAD CRÉDITOS: 6 LABORATORIO PROFESORADO: Coordinador: D. Luis Jacobo Álvarez Ruiz de Ojeda D. José Rey Juncal. Fdo.: D. L. Jacobo Álvarez Ruiz de Ojeda Fdo.: D. José Rey Juncal DE HOJA 2 DE 9 DEPARTAMENTO DE TECNOLOGÍA ELECTRÓNICA ASIGNATURA: LABORATORIO DE SISTEMAS DIGITALES Universidad de Vigo PROGRAMABLES II Universidad de Vigo CÓDIGO: 305010769 CURSO ACADÉMICO: 05-06 OBJETIVOS - Consolidación de los diferentes conceptos asociados a los Circuitos Digitales Configurables (CDCs) estudiados en la asignatura Sistemas Digitales Programables II. - Aprendizaje de los métodos y herramientas de diseño de sistemas digitales mediante Circuitos Digitales Configurables del tipo FPGA. - Aplicación de métodos avanzados de diseño de sistemas digitales. - Aplicación de los conocimientos de las arquitecturas de FPGAs adquiridos en la asignatura Sistemas Digitales Programables II. - Diseño de sistemas digitales complejos mediante FPGAs, llegando a la implementación final y prueba de dichos sistemas. PROGRAMA DE LABORATORIO TEMA 1 (2 h.). FASES DEL DISEÑO CON CDCs I. DESCRIPCIÓN ESTRUCTURAL DEL DISEÑO MEDIANTE ESQUEMÁTICOS. 1.1.- Introducción. Diagrama de flujo general de la herramienta Foundation ISE. 1.2.- Captura de esquemáticos. Biblioteca de componentes para esquemático de Foundation ISE. 1.3.- Realización de ejemplos. TEMA 2 (2 h.).- FASES DEL DISEÑO CON CDCs II. DESCRIPCIÓN DEL DISEÑO MEDIANTE LENGUAJES DE DESCRIPCIÓN HARDWARE. 2.1.- Introducción. 2.2.- VHDL para síntesis. 2.3.- Utilización del editor HDL. 2.4.- Inclusión de un componente HDL en un esquemático. TEMA 3 (2 h.). FASES DEL DISEÑO CON CDCs III. VERIFICACIÓN DEL DISEÑO MEDIANTE SIMULACIÓN FUNCIONAL. 3.1.- Introducción. Fdo.: D. L. Jacobo Álvarez Ruiz de Ojeda Fdo.: D. José Rey Juncal HOJA 3 DE 9 DEPARTAMENTO DE TECNOLOGÍA ELECTRÓNICA Universidad de Vigo ASIGNATURA: LABORATORIO DE SISTEMAS DIGITALES PROGRAMABLES II Universidad de Vigo CÓDIGO: 305010769 CURSO ACADÉMICO: 05-06 3.2.- Simulación funcional. 3.3.- Realización de ejemplos. TEMA 4 (2 h.). CONJUNTOS CONFIGURABLES DE PUERTAS (FPGAs). ARQUITECTURAS. 4.1.- Introducción. 4.2.- Arquitectura de las FPGAs de la familia Spartan II de Xilinx. TEMA 5 (1 h.). FASES DEL DISEÑO CON FPGAs I. COMPILACIÓN E IMPLEMENTACIÓN DEL DISEÑO. 5.1.- Introducción. 5.2.- Compilación del diseño. 5.3.- Implementación del circuito. 5.4.- Opciones de implementación para las FPGAs de la familia Spartan II de Xilinx. 5.5.- Informes de implementación para las FPGAs de la familia Spartan II de Xilinx. TEMA 6 (1 h.). FASES DEL DISEÑO CON FPGAs II. EDICIÓN DEL DISEÑO IMPLEMENTADO. 6.1.- Introducción. 6.2.- Utilización del editor de FPGAs (“FPGA Editor”). 6.3.- Edición de bloques. TEMA 7 (2h.). FASES DEL DISEÑO CON FPGAs III. VERIFICACIÓN DEL DISEÑO MEDIANTE SIMULACIÓN TEMPORAL Y ANÁLISIS DE RETARDOS. 7.1.- Simulación temporal. 7.2.- Análisis de retardos mediante el fichero de informe de retardos. 7.3.- Análisis de retardos mediante el programa Analizador de tiempos (“Timing Analyzer”). 7.4.- Realización de ejemplos. TEMA 8 (2 h.): FASES DEL DISEÑO CON FPGAs IV. TECNOLOGÍAS Y CONFIGURACIÓN. 8.1.- Introducción. 8.2.- Tecnología y métodos de configuración de las FPGAs de Xilinx. Fdo.: D. L. Jacobo Álvarez Ruiz de Ojeda Fdo.: D. José Rey Juncal HOJA 4 DE 9 DEPARTAMENTO DE TECNOLOGÍA ELECTRÓNICA Universidad de Vigo ASIGNATURA: LABORATORIO DE SISTEMAS DIGITALES PROGRAMABLES II Universidad de Vigo CÓDIGO: 305010769 CURSO ACADÉMICO: 05-06 8.3.- Placas de desarrollo basadas en FPGAs de Xilinx. 8.4.- Obtención del fichero .BIT de configuración. 8.5.- Programación de la FPGA. ”iMPACT”. 8.6.- Solución de problemas. 8.7.- Comprobación del circuito. “Probing”. 8.8.- Programación de una memoria de configuración. 8.9.- Realización de ejemplos. TEMA 9 (2 h.). FASES DEL DISEÑO CON CDCs IV. DESCRIPCIÓN DE SISTEMAS SECUENCIALES MEDIANTE GRAFOS DE ESTADO. 9.1.- Introducción. 9.2.- Herramientas gráficas para la descripción de diagramas de estado de Sistemas Secuenciales Síncronos. 9.3.- Realización de ejemplos. - REALIZACIÓN DE EJEMPLOS DE SISTEMAS DIGITALES DE COMPLEJIDAD MEDIA (26 h.). - Circuito de lectura de un teclado PS2. - Memoria FIFO. - Generador digital de funciones. - REALIZACIÓN DE UN TRABAJO DE DISEÑO DE UN SISTEMA DIGITAL DE COMPLEJIDAD MEDIA BASADO EN UNA FPGA DE XILINX (16 h.). Para la realización del trabajo se deberán aplicar los métodos de diseño estudiados en la asignatura SDPII para la realización de sistemas digitales complejos. TEMA 10 (2h.). INTRODUCCIÓN A LAS HERRAMIENTAS DE DISEÑO DE ALTO NIVEL CON CDCs. 10.1.- Introducción. 10.2.- Generador de Sistemas (“System Generator”) de Xilinx. 10.2.1.- Fases del diseño con la herramienta “System Generator”. 10.2.2.- Realización de un ejemplo práctico de diseño. Fdo.: D. L. Jacobo Álvarez Ruiz de Ojeda Fdo.: D. José Rey Juncal HOJA 5 DE 9 DEPARTAMENTO DE TECNOLOGÍA ELECTRÓNICA Universidad de Vigo ASIGNATURA: LABORATORIO DE SISTEMAS DIGITALES PROGRAMABLES II Universidad de Vigo CÓDIGO: 305010769 CURSO ACADÉMICO: 05-06 BIBLIOGRAFÍA LIBRO BÁSICO DE TEXTO DE LA ASIGNATURA: [ÁLVAREZ 04] ÁLVAREZ RUIZ DE OJEDA, L. Jacobo, Diseño Digital con Lógica Programable, Editorial Tórculo, Santiago de Compostela, 2004. BIBLIOGRAFÍA COMPLEMENTARIA: DISEÑO DE SISTEMAS DIGITALES: [ACOSTA 00] ACOSTA, A.J., BARRIGA, A., BELLIDO, M.J., JUAN, J., VALENCIA, M., Temporización en circuitos integrados digitales CMOS, Marcombo, Barcelona, 2000. [ÁLVAREZ 01] ÁLVAREZ RUIZ DE OJEDA, Diseño de aplicaciones mediante PLDs y FPGAs, Editorial Tórculo, Santiago de Compostela, 2001. [ÁLVAREZ 02] ÁLVAREZ RUIZ DE OJEDA, L. Jacobo, MANDADO PÉREZ, E., VALDÉS PEÑA, M.D., Dispositivos Lógicos Programables y sus aplicaciones, Editorial ThomsonParaninfo, 2002. [ÁLVAREZ 95a] ÁLVAREZ RUIZ DE OJEDA, L. Jacobo, Metodología de diseño de controladores lógicos caracterizados por flancos realizados con circuitos digitales configurables, tesis doctoral, Universidad de Vigo, 1995. [ÁLVAREZ 95b] ÁLVAREZ RUIZ DE OJEDA, L. Jacobo, MANDADO PÉREZ, Enrique, RODRÍGUEZ ANDINA, Juan J., Manual de prácticas de Electrónica Digital 3ª edición, Ed. Marcombo, Barcelona, 1995. [ARTIGAS 02] ARTIGAS MAESTRE, J.I., BARRAGÁN PÉREZ, L.A., ORRITE URUÑUELA, C., URRIZA PARROQUÉ, I., Electrónica Digital. Aplicaciones y problemas con VHDL, Prentice-Hall, Madrid, 2002. [BOLTON 90] BOLTON, M., "Digital systems design with programmable logic", Addison-Wesley, 1990. [LALA 90] LALA, Parag K., "Digital system design using programmable logic devices", Prentice Hall, New Jersey, 1990. [LEWIN 92] LEWIN, D., PROTHEROE, D., "Design of logic systems", Chapman & Hall, 19922. [MANDADO 98] MANDADO PÉREZ, Enrique, Sistemas Electrónicos Digitales 8ª edición, Ed. Fdo.: D. L. Jacobo Álvarez Ruiz de Ojeda Fdo.: D. José Rey Juncal HOJA 6 DE 9 DEPARTAMENTO DE TECNOLOGÍA ELECTRÓNICA Universidad de Vigo ASIGNATURA: LABORATORIO DE SISTEMAS DIGITALES PROGRAMABLES II Universidad de Vigo CÓDIGO: 305010769 CURSO ACADÉMICO: 05-06 Marcombo, Barcelona, 1998. [MEYER-BAESE 01] MEYER-BAESE, UWE, “Digital Signal Processing with Field Programmable Gate Arrays”, Springer-Verlag, Berlín, 2001. [PELLERIN 91] PELLERIN, D., HOLLEY, M., "Practical design using programmable logic", Prentice Hall, Londres, 1991. [PELLERIN 94] PELLERIN, D., HOLLEY, M., "Digital Design using ABEL", Prentice Hall, Londres, 1994. [PÉREZ 02] PÉREZ LÓPEZ, S.A., SOTO CAMPOS, E., FERNÁNDEZ GÓMEZ, S., Diseño de sistemas digitales con VHDL, Thomson-Paraninfo, Madrid, 2002. [SCARPINO 98] SCARPINO, F., “VHDL and AHDL digital system implementation”, Prentice Hall, Londres, 1998. [SILVA 85] Silva, Manuel, Las Redes de Petri en la Automática y la Informática, editorial AC, 1985. PLDs Y FPGAs: [ACTEL] Dirección de Internet, http://www.actel.com, Actel. [ALTERA] Dirección de Internet, http://www.altera.com, Altera. [ÁLVAREZ 95a] ÁLVAREZ RUIZ DE OJEDA, L. Jacobo, Metodología de diseño de controladores lógicos caracterizados por flancos realizados con circuitos digitales configurables, tesis doctoral, Universidad de Vigo, 1995. [ÁLVAREZ 01] ÁLVAREZ RUIZ DE OJEDA, L. Jacobo, Diseño de aplicaciones mediante PLDs y FPGAs, Editorial Tórculo, Santiago de Compostela, 2001. [ÁLVAREZ 02] ÁLVAREZ RUIZ DE OJEDA, L. Jacobo, MANDADO PÉREZ, E., VALDÉS PEÑA, M.D., Dispositivos Lógicos Programables y sus aplicaciones, Editorial ThomsonParaninfo, 2002. [AMD 89] "MACH devices data book", AMD, 1989. [ATMEL 90] "1990/91 data book", Atmel, 1990 [BROWN 92] BROWN, S.D., FRANCIS, R.J., ROSE, J., VRANESIC, Z.G., "Field Programmable Gate Arrays", Kluwer Academic Press, 1992. [BURTON 90] BURTON, Von L., "The programmable logic device handbook", TAB professional Fdo.: D. L. Jacobo Álvarez Ruiz de Ojeda Fdo.: D. José Rey Juncal HOJA 7 DE 9 DEPARTAMENTO DE TECNOLOGÍA ELECTRÓNICA Universidad de Vigo ASIGNATURA: LABORATORIO DE SISTEMAS DIGITALES PROGRAMABLES II Universidad de Vigo CÓDIGO: 305010769 CURSO ACADÉMICO: 05-06 and reference books, 1990. [CROSSPOINT 92] "CP20K Field programmable gate arrays. Data book", Crosspoint Solutions, 1992. [CYPRESS] Dirección de Internet, http://www.cypress.com, Cypress. [CHAN 94] CHAN, Pak K., MOURAD, Samiha, "Digital design using Field Programmable Gate Arrays", Prentice Hall, New Jersey, 1994. [GRUNBACHER 92] GRUNBACHER, H., HARTENSTEIN, R. W., editores, "Field programmable gate arrays. Architectures and tools for rapid prototyping, FPL 92 selected papers", Springer-Verlag, Berlín, 1992. [HARTENSTEIN 94] HARTENSTEIN, R. W., SERVIT, M. Z., editores, "Field programmable logic. Architectures, synthesis and applications. FPL 94 proceedings", Springer-Verlag, Berlín, 1994. [INTEL 90] "Programmable logic handbook", Intel, 1990. [JENKINS 94] JENKINS, Jesse H., "Designing with FPGAs and CPLDs", Prentice Hall, New Jersey, 1994. [LATTICE] Dirección de Internet, http://www.latticesemi.com, Lattice semiconductors. [LUCENT] Dirección de Internet, http://www.lucent.com, Lucent microelectronics. [MM 81] "Programmable array logic handbook", Monolithic Memories, 1981. [MOORE 91] MOORE, W., LUK, W., editores, "FPGAs, Oxford 1991 international workshop on field programmable logic and applications", Abingdon EE & CS books, Abingdon, 1991. [MOORE 93] MOORE, W., LUK, W., editores, "More FPGAs, Oxford 1993 international workshop on field programmable logic and applications", Abingdon EE & CS books, Abingdon, 1993. [MOORE 95] MOORE, W., LUK, W., editores, "Field-Programmable logic and applications, 5th international workshop, FPL' 95", Springer-Verlag, Berlin, 1995. [OLDFIELD 95] OLDFIELD, J.V., DORF, R.C., "Field Programmable Gate Arrays: Reconfigurable logic for rapid prototyping and Implementation of Digital Systems", John Wiley & Sons, 1995. [PELLERIN 91] PELLERIN, D., HOLLEY, M., "Practical design using programmable logic", Prentice Hall, Londres, 1991. Fdo.: D. L. Jacobo Álvarez Ruiz de Ojeda Fdo.: D. José Rey Juncal HOJA 8 DE 9 DEPARTAMENTO DE TECNOLOGÍA ELECTRÓNICA Universidad de Vigo ASIGNATURA: LABORATORIO DE SISTEMAS DIGITALES PROGRAMABLES II Universidad de Vigo CÓDIGO: 305010769 CURSO ACADÉMICO: 05-06 [PHILIPS 87a] "Semi-custom programmable logic devices data handbook", Philips, 1987. [PHILIPS 87b] "System Cell 1987. Design manual. Cell library", Philips, 1987. [PHILIPS 90] "Semi-custom programmable logic devices (PLD) data handbook", Philips, 1990. [PREP 93] "Programmable Electronics Performance Corporation", "PREP PLD Benchmark", 1993. [QUICKLOGIC] Dirección de Internet, http://www.quicklogic.com, Quicklogic. [SHARMA 98] SHARMA, A. K., "Programmable logic handbook", McGraw Hill, Fairfield, 1998. [TEXAS 88] "Programmable logic data book", Texas Instruments, 1988. [TEXAS 93a] "FPGA data manual", Texas Instruments, 1993. [TEXAS 93b] "FPGA applications handbook", Texas Instruments, 1993. [WSI 91] "Programmable peripheral design and applications handbook", WSI, California, 1991. [XILINX 94] "The programmable gate array data book", Xilinx, San Jose (CA), 1994. [XILINX 99] “Xilinx Student Edition version 1.5”, Prentice-Hall, 1999. [XILINX] Dirección de Internet, http://www.xilinx.com, Xilinx, 2001. [YALAM 01] YALAMANCHILI, Sudhakar, “Introductory VHDL: From simulation to synthesis + Xilinx Foundation series software, version 2.1", Prentice Hall, 2001. Fdo.: D. L. Jacobo Álvarez Ruiz de Ojeda Fdo.: D. José Rey Juncal HOJA 9 DE 9 DEPARTAMENTO DE TECNOLOGÍA ELECTRÓNICA ASIGNATURA: LABORATORIO DE SISTEMAS DIGITALES Universidad de Vigo PROGRAMABLES II Universidad de Vigo CÓDIGO: 305010769 CURSO ACADÉMICO: 05-06 PRERREQUISITOS RECOMENDADOS - Haber cursado Electrónica Digital (2º). - Haber cursado Sistemas Digitales Programables I (3º). - Haber cursado Electrónica Analógica (convertidores A/D y D/A) (3º). No es necesario haberlas aprobado, pero sí conocer las materias que se imparten en estas asignaturas. CORREQUISITOS RECOMENDADOS - Haber cursado Diseño Microelectrónico I (VHDL) (4º) el primer cuatrimestre. - Haber cursado Sistemas Digitales Programables II (4º) el primer cuatrimestre. No es necesario haberlas aprobado, pero sí conocer las materias que se imparten en estas asignaturas. EVALUACIÓN - Asistencia a clase obligatoria. - Realización de los ejemplos propuestos de diseño de sistemas digitales. - Realización de un trabajo de diseño de un sistema digital basado en una FPGA y su verificación mediante la simulación y prueba posterior del circuito. - Memoria explicativa del trabajo realizado. - Si la realización de los ejemplos y del trabajo no es satisfactoria, será necesario realizar un examen práctico de la asignatura. TUTORÍAS Luis Jacobo Álvarez Ruiz de Ojeda: Martes de 11 a 14; Viernes de 11 a 14. José Rey Juncal: Martes de 9 a 13: Miércoles de 11 a 13. Fdo.: D. L. Jacobo Álvarez Ruiz de Ojeda Fdo.: D. José Rey Juncal