UART. Clase 13 (14 de mayo de 2013)

Anuncio

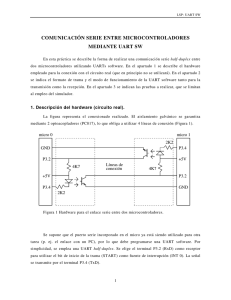

UART Diseño de Sistemas con FPGA 1er cuatrimestre 2013 Patricia Borensztejn UART • Universal Asynchronous receiver and transmitter: dispositivo (controlador ) que envía datos paralelos sobre una línea serie. • RS-232: standard que especifica las características eléctricas, mecánicas, funcionales de los dos equipos que se comunican. • Diseñar una UART significa hacer el software o el hardware que controle la transmisión y recepción de los datos según la norma RS232. Es decir, debemos conocer la norma. RS-232 • RS232 (Recommended Standard 232, también conocido como Electronic Industries Alliance RS-232C) es una interfaz que designa una norma para el intercambio de una serie de datos binarios entre un DTE (Equipo terminal de datos) y un DCE (Data Communication Equipment, Equipo de Comunicación de datos), aunque existen otras en las que también se utiliza la interfaz RS-232. DTE - DCE • Los equipos conectados a ambos extremos de la línea reciben los nombres de DTE(Equipo terminal de datos )y DCE (Equipo de Comunicación de Datos) • Antes, El DTE era la computadora y el DCE el modem, actualmente, muchos dispositivos que se van a conectar a la computadora tienen un DCE (en particular, las placas de desarrollo que utilizamos) • El DTE usa un conector macho DB9, y el DCE usa conector hembra DB9 (o DB25) Puertos Serie en las placas • Spartan -3 Starter Kit: – Contiene un puerto RS-232 con el conector standard de 9 pines hembra (DCE) • .Spartan-3E Starter Kit: – Contiene los dos puertos, DCE Y DTE con conectores de 9 pines • Nexys2: – Contiene un puerto DCE (conector hembra 9 pines) • Nexys3: – Contiene un puerto USB-Serie Convertidor de voltaje • Debido a que el nivel de voltaje definido en RS-232 es distinto al voltaje de los pines de E/S de la FPGA, es necesario un chip convertidor entre ambos (entre el puerto serie y los pines de la FPGA). • El convertidor de tensión, en todos los casos está incluído en las placas Spartan-3e Starter Kit Nexys2 Chip ST3232 Conector DCE UART • • • • La UART incluye un transmisor y un receptor. El transmisor es básicamente un shift register que carga los datos en paralelo a transmitir y luego los shiftea uno a uno a una velocidad determinada (rate). Empezando por el LSB(Least Significand Bit) El receptor, recibe los bits uno a uno y reensambla el dato completo. Procedimiento: – Cuando la línea serie no lleva datos (iddle) está a “1”. – La transmisión comienza con un bit de start (“0”), seguido por los bits de datos (6,7, o 8), un bit opcional de paridad (paridad par (igual a cero cuando hay un número par de unos) o impar) y finaliza con los bits de stop (1, 1.5 o 2). – No se envía señal de clk. – Antes de iniciarse la transferencia, el emisor y el transmisor deben ponerse de acuerdo en lo que se transmite y además en la velocidad de transmisión (baud rate: bits por segundo) UART: Subsistema receptor • Módulo Generador de Baud Rate – • Modulo Receptor – • Debido a que no hay un reloj que permita decidir cuando el dato (bit) está disponible a la entrada, el receptor usará un sistema de “oversampling” que permite estimar el punto medio del bit transmitido y adquirirlo en ese instante. Este módulo es el encargado de generar las señales para el procedimiento de oversampling. En función de los parámetros acordados (formato de la trama ) y del procedimiento de oversampling, se van obteniendo los bits hasta completar el dato. Módulo Interface – – Provee un mecanismo para señalizar al sistema la llegada de un nuevo dato, y previene que éste no sea adquirido dos o mas veces. Provee buffers para almacenar los datos entre el sistema y el receptor. FPGA Procedimiento de Muestreo • Dado el baud rate de transmisión, se genera una frecuencia que es 16 veces el baud rate, y se sigue el siguiente procedimiento: 1. 2. 3. 4. 5. 6. Esperar que la señal se ponga a “0”, el principio del bit de start, e iniciar el conteo. Cuando el conteo llega a 7, quiere decir que estamos en la mitad del start bit, se resetea el contador a cero. Cuando el contador llega a 15, quiere decir que estamos en la mitad del primer bit de datos. Se obtiene el bit y se resetea el contador. Repetir el paso 3 por cada bit de datos. Si hay bit de paridad, repetir el paso 3 para el bit de paridad Repetir el paso 3 para el bit de stop. Módulo Generador de Baud Rate • Su función será generar un “tick” 16 veces por baud rate. • Si el baud rate es de 19.200 ciclos por segundo, la frecuencia de muestreo debe ser 19.200 *16= 307.200 ticks por segundo. Si el reloj de la placa (en spartan) es de 50 Mhz, entonces hay que generar un tick cada 163 ciclos de reloj. 50 *106 163 307200 • Para ello podemos utilizar un contador modulo 163. • La señal generada, llamada “tick” no se comporta como un reloj, sino mas bien como un enable, porque valdrá “1” durante un ciclo de reloj, del reloj del sistema, y luego valdrá cero. Módulo Generador de Baud Rate • Usamos un contador módulo m genérico, instanciado a mod 163(M) y 8 (N)bits • Módulo Generador de Baud Rate (mod_m_counter.v) Módulo Receptor • Este módulo es el responsable del sampleo de la línea de datos serie, debe seguir el procedimiento del muestreo descrito anteriormente, de forma que será necesario realizar una máquina de estados o bien un diagrama de estados. (ASMD: algorithmic state machine with Data Path) FSM y ASM • Para representar Maquinas de Estados Finitas (FSM) se pueden utilizar: – Grados de Estado o Diagramas de Estado – O bien ASM: Algorithmic State Machine • Ambos tienen su extensión con Data Path: – FSMD – ASMD ASMD del Módulo Receptor Modulo Receptor • Módulo Receptor: uart_rx.v Módulo Interface – Provee un mecanismo para señalizar al sistema la llegada de un nuevo dato, y previene que éste no sea adquirido dos o mas veces. – Provee buffers para almacenar los datos entre el sistema y el receptor. Módulo Interface • El módulo Interface utiliza una FIFO para almacenar el dato (fifo.v) Módulo Transmisor • La organización del transmisor es similar a la del receptor, es decir, consiste de: – Transmisor: • Es un shift register que envía hacia fuera uno a uno los bits a una determinada velocidad. • Como aquí no hay muestreo de bits, la frecuencia de los ticks es 16 veces más lenta que en el caso del receptor. • Usa el mismo generador de baud rate que el receptor pero se le agrega un contador de forma que cada bit es shifteado cada 16 ticks. – Generador de baud rate • El mismo módulo que usa el receptor. – Interface: • FIFO de transmisión Módulo Transmisor • Módulo Transmisor (uart_tx.v) • Módulo Interface (fifo.v) UART Completa • Código UART (uart.v) Prueba de la UART • El circuito de prueba consiste en recibir desde la PC datos. Estos datos se incrementan en 1 y vuelven a ser transmitidos a la PC. Las señales de control de la FIFO (escribir en la FIFO de transmisión y eliminar de la FIFO de recepción) se generan al apretar el pushbottom. Los datos de entrada a la UART están conectados a los LEDS, y las señales tx_full y rx_empty a los dos segmentos horizontales del digito de la derecha de los 7 segmentos (todo un debugger). HyperTerminal • Configurar el Hyper Terminal a: – 19.200 baudios, 8 bits de datos, 1 bit de stop y no paridad. Prueba de la UART • Por ejemplo: – Conectar el cable serie (o usb-serie) a la PC y a la FPGA – Abrir el Hiper Terminal y configurarlo para la conexión – Tipear HAL en el Hiper terminal – Apretar el pushbottom 3 veces (cada vez que se aprieta remueve un dato de la cola de recepcion, y lo introduce, ya incrementado, en la de transmisión) – Debemos ver en la PC: IBM (la típica!)