PRACTICA N0.6

Anuncio

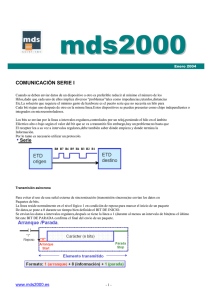

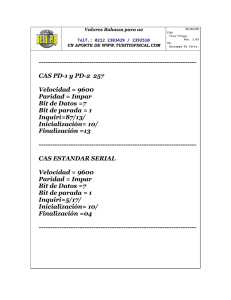

Laboratorio de Microprocesadores El UART PRACTICA N0.6 NOMBRE DE LA PRÁCTICA EL PUERTO SERIE 8250 OBJETIVO ESPECÍFICO: Aprender a programar y utilizar el adaptador de interfase serie UART INTRODUCCIÓN: Un puerto serial se caracteriza por: 9 Transmitir un bit detrás de otro usando una sola línea 9 Permite mayor separación entre transmisor y receptor U Es más lento que en la transferencia en paralelo SERIE PARALELO BIT7 CPU BIT0 TRANSMISOR RECEPTOR MODOS DE COMUNICACIÓN De acuerdo al sentido de la transmisión se clasifican en: 3 SIMPLEX 3 HALF DUPLEX O SEMI-DUPLEX 3 FULL DUPLEX O DUPLEX COMPLETO De acuerdo a su temporización pueden ser: 3 3 SÍNCRONO ASÍNCRONO SIMPLEX Es comunicación en un solo sentido, esto es, que el mensaje siempre viajará de transmisor a receptor M.C. Carlos E. Canto Quintal - 64 - Dato Transmisor Receptor Laboratorio de Microprocesadores El UART HALF DUPLEX : La comunicación puede ser en ambos sentidos pero no simultáneamente Receptor Transmisor Transmisor Receptor Receptor Transmisor Receptor Transmisor FULL DUPLEX : la comunicación puede ser en ambos sentidos y simultáneamente Receptor Transmisor Transmisor Receptor COMUNICACIÓN SINCRÓNICA Se caracteriza porque el dato es enviado junto con la señal de reloj del transmisor Dato Transmisor Receptor sincronía COMUNICACIÓN ASÍNCRONA Asíncrono, significa que el transmisor y el receptor tienen sus propios generadores de baudaje con la misma frecuencia,pero independientes. No existe una señal de sincronía entre transmisor y receptor Ambos dispositivos deben manejar la misma velocidad de transmisión o baudaje. Interfase simple (velocidad de transmisión limitada típicamente a < de 64 Kbps) Usado para conectar Impresoras,terminales, Modems, conexión casera a Internet No hay envio de reloj (Tx & Rx tienen sus propios relojs) Requiere de bits de arranque y de parada para proporcionar temporización de byte pero aumenta el número de bits M.C. Carlos E. Canto Quintal - 65 - Laboratorio de Microprocesadores El UART Con frecuencia se usa paridad para validar una correcta recepción. Ejemplo deTransmisión asíncrona de una serie de caracteres cada caracter está enmarcado por un bit de arranque y por uno o dos bit de parada Sistema de comunicación serial Dato al destino Dato de la fuente 8 bits 1 bit a la vez 8 bits Buffer de dato recibido Buffer de dato transmitido 8 bits 8 bits Registro de corrimiento entrada serie/salida paralelo Registro de corrimiento entrada paralelo/salida serie Reloj del Receptor Reloj del Transmisor Transmisor Receptor Circuitos integrados adaptadores de comunicación serial más usados ✔ UART (Universal Asynchronous Reciever Transmitter de National semiconductor). ✔ ACIA ( Asynchronous Communications Interfase Adapter de Motorola). ✔ Z80 SIO (Serial Input/Output de Zilog) M.C. Carlos E. Canto Quintal - 66 - Laboratorio de Microprocesadores El UART ✔ USART (Universal Synchronous Asynchronous Reciever Transmitter de Intel) FUNCIONES PRINCIPALES DE UN UART 3 3 3 3 3 3 3 Convierte los datos de paralelo a serie y viceversa Genera y checa la paridad de los datos Genera bit de arranque Inserta bit de parada Controla el número de bits por carácter Almacena temporalmente el mensaje Controla la velocidad de transmisión-recepción DIAGRAMA DE BLOQUES DE UN PUERTO SERIE RS232C USANDO UN UART PUERTO SERIE RS232C Bus de datos NIVEL TTL NIVEL RS232 UART Periférico serie de salida Paralelo/serie CPU Manejador RS-232 Periférico serie de entrada Serie/paralelo Protocolo de comunicación asíncrona de bit de arranque/bit de parada Bit de paridad opcional de 7 ú 8 bits de datos Línea ociosa b0 b1 b2 b3 b4 b5 b7 P Bit(s) de parada Bit de arranque M.C. Carlos E. Canto Quintal b6 - 67 - Laboratorio de Microprocesadores El UART Arquitectura interna del UART 8250 Los registros del UART Registro de Control de Línea (Line Control Register LCR) b7 DLAB DLAB b6 Break Break Control Control 0=off 0=off 1=on 1=on b5 b4 000 001 011 101 111 = = = = = b3 Paridad ninguna impar par marca espacio Divisor DivisorLatches LatchesAccess Access Bit: Bit:Bit Bitde deAcceso Accesoaalos los Latches Divisores Latches Divisores M.C. Carlos E. Canto Quintal - 68 - b2 Número Número de destops stops bits bits 0=1 0=1 1=2 1=2 b1 b0 Número de bits de Datos 10=7 11=8 Laboratorio de Microprocesadores El UART Registro de Status de Línea (Line Status Register LSR) b7 b6 b5 b4 b3 Buffer Buffer de Tranmisor Detección Detección Tranmisor de Transmisor vacío de de vacío Transmisor Vacío (TXE) Break Break (TXE) Vacío (TBE) (TBE) Siempre Siempre 00 b2 Error Error de de tramado tramado b1 Error Error de de paridad paridad b0 Error Error de de Overrun Overrun Dato Dato Listo Listo (RxRDY) (RxRDY) Registro de Habilitación de Interrupciones (Interrupts Enable Register IER b7 b6 Siempre Siempre 00 Siempre Siempre 00 b5 Siempre Siempre 00 b4 b3 Siempre Siempre 00 b2 b1 b0 Error Buffer Buffer Error del del Dato del Dato del Receptor Transmisor Recibido Receptor Transmisor Recibido oo Vacío (RxRDY) Vacío (RxRDY) break (TBE) (TBE) break Entrada Entrada RS232 RS232 Registro de Identificación de Interrupciones (Interrupts Identificación Register IIR) b7 b6 Siempre Siempre 00 Bit 2 Siempre Siempre 00 b5 Siempre Siempre 00 b4 b3 Siempre Siempre 00 b2 b1 b0 Siempre Siempre 00 Bit 1 Bit 0 Prioridad * 0 0 1 Ninguna Interrupción identificada Ninguna 1 1 0 0 Error de serialización o Break 1 0 0 1 0 1 0 2 0 0 0 3 Dato Recibido Buffer del Transmisor vacío Entrada RS232 * 0 Es la más alta Tabla de Registros y el DLAB REGISTRO DE CONTROL DE FIFO Es un registro de solo escritura en la misma localidad del IIR ( el IIR es un registro de solo lectura). Se usa para habilitar y limpiar los FIFOs, pone el nivel de disparo del RCVR FIFO, y selecciona el tipo de señalización del DMA. Bit 0: poniéndole un 1 habilita tanto el FIFO del XMIT como del RCVR. Reseteando FCRO limpiará todos los bytes en ambos FIFOs M.C. Carlos E. Canto Quintal Registro DLAB A2 A1 A0 Lectura / Escritura 0 0 0 0 __ Receptor(lectura) Transmisor (escritura) 0 0 0 1 R/W Habilitación de interrupciones X 0 1 0 LECTURA Identificación de Interrupción X 0 1 1 R/W X 1 0 0 R/W Registro de Control del Modem X 1 0 1 R/W Registro de Status de Línea X 1 1 0 R/W Registro de Status del Modem X 1 1 1 R/W Scratch Pad 1 0 0 0 R/W Latch Divisor Menos Significativo 1 0 0 1 R/W Latch Divisor Más Significativo - 69 - de Control de Línea Laboratorio de Microprocesadores El UART Configuración de pines del UART National 8250 D7-D0 DISTR DOSTR INTRPT MR A0 A1 A2 SOUT SIN RTS DTR DCD CTS RI XTAL1 3.072 MHZ ADS “0” DOSTR DISTR CS2 CS1 “1” A conector RS-232 Manejadores EIA RS-232 DSR CS0 XTAL2 BAUDOUT RCLK Carlos Canto DISTRIBUCIÓN DE TERMINALES DEL UART16650 TERMINALES DEL UART16650 ADS, Address Strobe, Pin 25: Una transición positive en la señal de strobe de dirección (ADS) captura las señales del selección de registro (A0,A1,A2) y la de selección del Chip (CS0,CS1,CS2). Nota: se requiere una señal activa en ADS cuando las señales de selección de registro y de selección del Chip no se mantienen estables durante una operación de lectura o escritura. Si ADS no se requiere se conecta a BAJO. BAUDOUT, Baud Out, Pin 15: Es la señal 16X clocked la sección del transmisor del UART.La frecuencia del reloj es igual a la gfrecuencia del oscilador principal de referencia dividido entre el divisor especigficado en los Latches Divisor del Generador de Baudaje. El BAUDOUT también puede ser usado por la sección del receptor conectando esta salida a la entrada RCLK del chip. CS0, CS1, CS2, Chip Select, Pins 12±14:Cuando CS0 y CS1 están altos y CS2 en bajo, el chip es seleccionado. Esto habilita la comunicaciòn entre el UART y la CPU. M.C. Carlos E. Canto Quintal - 70 - Laboratorio de Microprocesadores El UART DDIS, Driver Disable, Pin 23: se va a bajo siempre que la CPU esté leyendo datos en la UART. Esta puede deshabilitar o controlar la dirección de un transceptor de bus de datos entre la CPU y la UART. MR, Master Reset, Pin 35: cuando esta en alto, limpia todos los registros ( excepto el Buffer del Receptor, Retén del Transmisor y los Latches Divisors), y el control lógico del UART . Los estados de varias señales de salida (SOUT, INTR, OUT1, OUT, RTS,DTR) se afectan al activar la entrada MR. RCLK, Receiver Clock, Pin 9: esta entrada es la frecuencia de reloj de 16X de la sección del receptor del chip. . CONEXIÓN DEL UART USANDO INTERRUPCIONES Bus Bus de de Datos Datos CPU CPU INTR UART UART Bus Bus de de Direcciones Direcciones Driver Driver RS232 RS232 MODEM MODEM LÍNEAS DE CONTROL Y DE STATUS (HANSDSHAKING) MATERIAL Y EQUIPO UTILIZADO: M.C. Carlos E. Canto Quintal - 71 - LÍNEA LÍNEA TELEFÒNICA TELEFÒNICA Laboratorio de Microprocesadores El UART 1 UART NS 8250A ó 16550 1 CI MAX232 1 CI 74LS08 1 cristal de 3.07 MHZ o 1.8432 Mhz Condensadores 30pf, 40 pf 1 resistencia de 1 MΩ, 1.5 KΩ 1 cable serie RS232 1 Conector DB-9 1 protoboard 1 Fuente de cd de 5 volts regulada 1 Analizador lógico ( o en su defecto osciloscopio multicanal CORRELACIÓN CON TEMAS DEL PROGRAMA VIGENTE: Con esta práctica se cubre algunos de los aspectos de la unidad II: Interfases METODOLOGÍA (DESARROLLO DE LA PRÁCTICA): I.-Implemente el circuito mostrado en el diagrama de abajo en un protoboard, tomando en cuenta la distribución planeada para la realización del sistema completo. II.- Use un cable serial RS232 estándar para conectar su sistema con una IBM PC compatible. Pins del puerto de comunicación de una PC Conector RS-232 DB-9 III,. Desarrolle un programa para el Z80 que nos permita transmitir a una computadora IBM PC, por el puerto serie RS232, una cadena de caracteres depositados en la memoria de programa EPROM . Inicie el programa para que transmita a 9600 bps, 7 bits de datos, sin paridad, 1 bit de stop. Use el programa Hyperterminal de Windows para recibir los caracteres y para desplegarlos en la pantalla de la PC. IV.- Calcule la duración de cada bit de acuerdo a la velocidad de transmisión establecida y compruébela con el osciloscopio M.C. Carlos E. Canto Quintal - 72 - Laboratorio de Microprocesadores El UART PRACTICA NUM. 6 IMPLEMENTACIÓN DE UN PUERTO SERIE USANDO EL UART NS8250 VCC=5v C5 1uF +5v 1 40 2 INT 7414 CS0 CS1 INT 21 18 22 19 25 35 IORD IOWR RESET BUS DE DATOS BUS DE DIRECCIONES A0 A1 A2 OUT1 OUT2 RD WR RD WR ADS RESET 1 2 3 4 5 6 7 8 D0-D7 C1 1uF VCC 12 13 30 1 U1 D0 D1 D2 D3 D4 D5 D6 D7 28 27 26 TXD RTS DTR RXD DCD DSR CTS RI 34 31 11 32 33 C2 1uF 5 TTL-OUT 11 12 10 38 37 36 39 C1+ C1C2+ C2- A2 1 A3 2 A4 3 A5 6 A6 4 A7 5 A B C G1 G2A G2B Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 DDIS NC CSOUT 74LS138 74LS08 3 6 C4 1uF T1IN T1OUT R1OUT R1IN 15 Vcc 14 RS232-OUT 13 RS232-IN BAUDOUT CS2 GND ó +5v 23 29 24 220 RCLK 1 15 9 2 7414 XIN 90H-97H XOUT A7 A6 A5 A4 A3 A2 A1 A0 1 0 0 1 0 X X X 16 2 1 17 3 4 7414 AL UART DIRECCIONES DE SELECCIÓN DEL UART 90H AL 97H Indicador de que el UART se ha seleccionado REOJ EXTERNO SALIDA OPCIONAL DEL RELOJ USANDO UN OSCILADOR EXTERNO, QUE PODRIA SER EL OSCILADOR USADO PARA E LCPU Carlos Canto M.C. Carlos E. Canto Quintal AL PUERTO RS232 DE LA PC GND SIN USO 1 2 XTAL2 20 fxtal=1.8432 3.072 Mhz V- 14 AL 8255 AL 15 8254 AL 14 ADC0804 13 12 11 10 9 7 1.5k V+ XTAL1/CLK 17 40-60pf C3 1uF 2 MAX232 1M 10-30pf Vcc 8250 A0 A1 A2 16 3 4 16 - 73 - Laboratorio de Microprocesadores El UART SUGERENCIA DIDÁCTICA: Resuelva el siguiente cuestionario 1.¿Cúal es el nivel lógico del pin de transmisión mientras que no se están transmitiendo caracteres ? 2.¿ En qué consiste el bit de de arranque (START BIT) ? 3.¿ Cúal es el nivel lógico de los bits de paro (STOP BIT)? 4.Explique por qué puede haber 1.5 bits de parada. 5.Explique qué es... a) paridad par. b) paridad impar. c) paridad marca. d) paridad espacio. REPORTE: I.-Incluya en su reporte, el diagrama de flujo y el listado del programa realizado para entablar la comunicación con la PC. II.-reporte si tuvo problemas con el manejo del puerto serial durante la práctica diga cuales fueron y como los resolvió. III.-reporte sus comentarios y conclusiones BIBLIOGRAFÍA: • • • • Manual de Zilog del Z80 Manual de Maxim del MAX232 Manual de National Semiconductor del 8250 Ramesh S. Gaonkar The Z80 Microprocessor: Architecture, Interfacing, Programming, and Design M.C. Carlos E. Canto Quintal - 74 -