Tema 2: Procesador y Placa Base

Anuncio

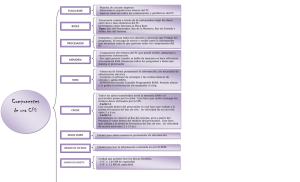

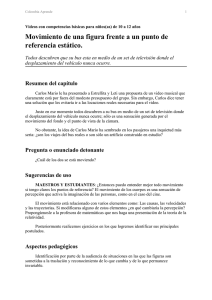

Tema 2: Procesador y Placa Base Periféricos e Interfaces Tema 2/1 Contenido Interfaz Procesador-Memoria Principal z Interfaz Procesador-Controladores E/S z Placa Base z Chipset z Tema 2/2 Historia: Procesadores 80x86 Intel i8086 200, ..., 700, 2000 MHz Bus del sistema RAM CPU (8086) Regs ROM Bus de Expans E/S Tema 2/3 ACCESO FISICO a la Memoria en el 80386 PROCESADOR 80386 F S B RESET Señales control: Ready, W/R, D/C Mux. de direcciones Buffer de escritura BE3..BE0 D31 .. D0 Control de mem Buffer de direcciones A31 .. A2 Buffer de datos PCLK CLK2 Control del bus Generador de reloj A31 .. A0 Din, Dout Controlador Sistema en Placa Base Tema 2/4 Memoria Principal Control de la memoria dinámica: RAS, CAS, WE, ... CICLOS DE BUS para el acceso físico a la memoria en sistemas con 80386 Ciclo de Estado CLK2 (FSB) 66 MHz PCLK (33 MHz) T1 Ciclo de Comando T2 1 CICLO de BUS T1 T2 Procesador A[31..2]; BE[3..0] /READY 4 Bytes D[31..0] 4 Bytes Tiempo de acceso A[31..2] W/R D[31..0] Tema 2/5 P M LECTURA ESCRITURA Ritmo de Transferencia = Ancho de Banda BW z Se mide en Bytes/Segundo z 4 bytes cada 4 ciclos del reloj del bus (CLK2), si no existen ciclos de espera – Suponer 100 MHz de FSB (T=10 ns) – BW= 4 / (4 ciclos x 10 ns) = 1e8 B/s = 100 MB/s 1B MEMORIA Bl.1 1B MEMORIA Bl.2 PROCESADOR 80386 1B MEMORIA Bl.3 1B MEMORIA Bl.4 Tema 2/6 “Bus Escalable” del Pentium Pro (PII, PIII, P4) BCLK Arbitraje Transacción 1 Petición Arbitraje Transacción 2 Bus Síncrono 64 bits datos 32 bits direcciones Tema 2/7 Error Snoop Petición Respuesta Datos Error Snoop Respuesta Datos ACCESO FISICO al Controlador de E/S del Periférico en sistemas 80386 80386 Señales control: (M/IO), ... Buffer de lect/escr PROCESADOR Decodific y control E/S D31 .. D0 Buffer de direcciones A15 .. A2 Controlador de E/S del Periférico Buffer de datos PCLK CLK2 Control del bus Generador de reloj Din, Dout A15 .. A0 IOR, IOW, ... Controlador de Entrada/Salida en Placa Base Tema 2/8 Memoria Principal CICLOS DE BUS del Sistema de E/S con procesadores 80386 CLK2 T1 T2 T1 PCLK A[15..2]; BE[3..0] /READY M/IO W/R D[31..0] Transacción de Lectura desde Controlador de Periférico Tema 2/9 T2 Ejemplo: Organización de la PLACA BASE basada en Pentium Bus Local Procesador/Memoria Control de la memoria DRAM (refresco, acceso secuencial, generación de patrones de señales, control de errores) Control de memoria cache Control del bus del sistema Bus del Sistema: PCI Control de memoria ROM Acceso al bus del sistema por parte de periféricos Buses de Expansión E/S Tema 2/10 Principales COMPONENTES de la placa base y sus interconexiones MEMORIA PRINCIPAL DRAM CACHE L2 Bus a la memoria principal PROCESADOR + CACHE L1 PUENTE NORTE Bus local compatible Socket 7 Bus AGP Placa Gráfica Bus PCI PUENTE SUR PLACA BASE Placa PCI Tema 2/11 Disco duro CDROM Ratón ... Chipset Intel 865G Intel D865GBF 3200 MB/s 3200 MB/s 266 MB/s 266 MB/s 480 Mb/s 300 MB/s Tema 2/12 Tema 2/13 Chipset Intel 865G Tema 2/14 Chips de soporte (CHIPSET) z Puente Norte – Controlador del sistema z z z Controlador DRAM Control de la transferencia de datos entre el procesador, la cache, DRAM, y bus PCI Controlador de la cache externa – Controlador de vídeo AGP – La frecuencia de funcionamiento determina la frecuencia máxima de la memoria principal Tema 2/15 Cada canal Puede consumir el ritmo de transferencia de 2 canales RAM Ritmo Máximo= FSB x 8 B/T FSB (4X) 533 MHz 533 MHz 533 MHz 666 MHz 640 MHz 800 MHz 8 Bytes/T Tema 2/16 Chips de soporte (CHIPSET) z Funciones Puente Sur (PIIX3, PIIX4) – – – – – – – – – – – Controlador del puente PCI-ISA Responsable de todas las comunicaciones ISA Controlador interrupciones Controlador DMA para interfaz IDE: Ultra-DMA/33, Ultra-DMA/66 Timer Reloj de tiempo real CMOS_RAM Ahorro de energía Controlador de la interfaz IDE/EIDE para 4 periféricos (HD y CD) Interfaz USB Controlador de bus serie I2C para generar señales de audio cuando existan alarmas (sobrecalentamientos o exceso de corrientes) – Otras interfaces a periféricos que se definan Tema 2/17 Tema 2/18 Tema 2/19 Tema 2/20 CMOS-RAM y Reloj de Tiempo Real (Puente Sur) Reloj de tiempo real Batería Registros de Estado del Reloj Registro de direcciones Hora/Fecha Espacio de direccionamiento E/S (64 K) FFFFH 71H: Registro Datos IRQ8 Datos de Configuración del Computador Zona de memoria: 64 posiciones x 8 bits Tema 2/21 Registro de datos 70H: Registro Direcciones 0000H M/IO# Rutina de Acceso a CMOS ; READ_CMOS ; read the contents of a specific CMOS register ; ; Call with: al = CMOS address to read (0x0 .. 0x7F) ; ; Returns: ah = Contents of register ; NMI enabled, if disabled read_CMOS proc near or al, 80h cli out 70h, al IODELAY in al, 71h mov ah, al mov al, 0 IODELAY out 70h, al sti ret read_CMOS endp Tema 2/22 ; disable NMI ; disable interrupts ; al= register to read ; returns contents of reg ; enable NMI ; enable interrupts Configuración de la Frecuencia de la Memoria Principal en Placa Base Espacio Configuración de Placa Base (Registros de Configuración) Espacio E/S ordenador: 2 registros para configurar la Registros Device 1 placa base Device 0 Direccion GMHCHCFG Dato Registros Tema 2/23 ¿Cómo se automatiza la configuración de la frecuencia de la memoria principal? Tema 2/24 ¿Cómo se automatiza la configuración de la frecuencia de la memoria principal? SMBus Tema 2/25 BIOS GMCH