Función de Coste Dinámica para Particionamiento HW/SW

Anuncio

S033C07F

1

Función de Coste Dinámica para

Particionamiento HW/SW Multiobjetivo

Elena Pérez, J. Javier Resano, Daniel Mozos, Hortensia Mecha, Sara Román

Departamento de Arquitectura de Computadores y Automática

Universidad Complutense Madrid.

{eperez, mozos, horten, sroman}@dacya.ucm.es, javier1@fdi.ucm.es

Resumen— Uno de los problemas más relevantes dentro del

codiseño hardware/software es la elección de una función de

cotes que guíe de forma adecuada la exploración del espacio de

diseño. Para medir la calidad de un diseño se utilizan una serie

de parámetros, que identifican distintas características del

sistema. El problema surge de la necesidad de mezcla todos estos

parámetro en un único termino que se identifica con la función

de coste.

En este articulo se presenta una función de coste dinámica que

evoluciona con el algoritmo de particionamiento y adapta su

comportamiento a la situación actual de la exploración del

espacio de diseño. Esta función de coste además recoge de forma

directa e intuitiva los distintos objetivos de codiseño.

Palabras Clave— Búsqueda tabú, codiseño, función de coste,

particionamiento.

I. INTRODUCCIÓN

Por codiseño se entiende el conjunto de pasos destinados a

la realización de forma automática de un diseño híbrido,

formado por un componente software (SW) y un componente

hardware (HW). Estos sistemas constan de una interfaz que

hace posible las comunicaciones entre dichos componentes.

Analizando las características de cada una de estas

plataformas, se observa que la implementación SW tiene un

coste reducido, pero su tiempo de ejecución es considerable.

Por otra parte, la implementación HW es mucho más rápida,

pero su coste es también muy elevado. Esto obliga a los

diseñadores a trabajar con parámetros totalmente opuestos a la

hora realizar un diseño que cumpla los requerimientos

exigidos, y a la vez aumenta considerablemente del número de

posibilidades de implementación para un mismo sistema.

Teniendo en cuenta esto y mediante la utilización de las

técnicas de codiseño es posible alcanzar las restricciones tanto

temporales como de coste impuestas, combinando

adecuadamente HW y SW.

Una de las fases más importantes del proceso de codiseño

es la que decide la parte de la funcionalidad del sistema que se

va a implementar en HW y la que se va a implementar en SW.

A

esta

fase

se

la denomina particionamiento

hardware/software (HW/SW).

Una vez particionado e implementado el sistema debe

cumplir unas determinadas restricciones, por ejemplo de área

HW y tiempo de ejecución. El particionamiento tiene como

objetivo encontrar entre todas las soluciones existentes una

solución óptima con respecto a las restricciones impuestas

inicialmente.

El particionamiento es por tanto un problema de

optimización clásico con ciertas particularidades, lo cual

permite emplear algoritmos de optimización conocidos. Dado

que se trata de un problema NP-completo, su resolución

implica el uso de heurísticas de optimización para la obtención

de resultados adecuados en un tiempo aceptable.

Cada vez que el algoritmo de particionamiento obtiene una

nueva solución, la calidad de dicha solución debe ser medida

para poder compararla con el resto de las posibles futuras

soluciones. La forma más precisa de comparación es la

medición de las características deseadas en la implementación

de la solución. Pero normalmente esta implementación no está

disponible durante el proceso de particionamiento. Por lo

tanto es necesario diseñar estimadores adecuados para medir

estas características.

Tan importante como los estimadores es la utilización de la

información que proporcionan para guiar la exploración del

espacio de soluciones de forma optima. Los diferentes

estimadores se han de combinar en una única función de coste

capaz de guiar la exploración del espacio de diseño hacia una

solución óptima. Esta es por tanto una de las tareas más

importantes a la hora de diseñar una herramienta de

particionamiento. Por otro lado no existe un criterio obvio

sobre como combinar los distintos estimadores, por lo que en

general funciones de costes muy heterogéneos guían

ineficientemente la exploración del espacio de soluciones.

En este estudio se demuestra la importancia de la elección

de una función de coste adecuada. Para ello hemos diseñado

una función de coste que evoluciona con el algoritmo de

particionamiento. Además esta función de coste combina el

área HW y el tiempo de ejecución de forma realista, evitando

la combinación de parámetros heterogéneo para estimar cada

una de ellas. Para demostrar la eficiencia de nuestra función

de coste hemos desarrollado una herramienta de

particionamiento basada en el algoritmo de búsqueda tabú.

II. TRABAJO PEVIO

Durante los últimos años el particionamiento ha sido uno de

S033C07F

los campos de mayor interés dentro del codiseño HW/SW

tanto en grupos universitarios [1], [2], como en la industria

[3]. Muchos de los algoritmos tradicionales de optimización

han sido adaptados para realizar el particionamiento con

diferente éxito, aunque se ha comprobado que más que el

algoritmo en sí, lo que mide la bondad de un particionador es

la calidad de los estimadores utilizados y la adecuación de la

función de coste. Como ya se ha comentado, la función de

coste es la encargada de evaluar la calidad de cada una de las

soluciones del espacio de búsqueda candidatas a ser visitadas

durante el particionamiento. Es por tanto la función de coste la

responsable de guiar al particionamiento en la búsqueda de

una solución óptima. De la fiabilidad de la función de coste

junto con la de los estimadores, va a depender la calidad de la

solución final.

La mayoría de los sistemas de codiseño no utilizan

estimaciones directas de los parámetros que quieren medir,

habitualmente tiempo y área, sino que utilizan medidas

indirectas de los mismos, como usar el número y complejidad

de las unidades funcionales para dar una indicación del área.

Por ejemplo, en [1] se presenta una función de coste que trata

de adaptarse en cada momento a la situación del diseño, pero

en la que se realizan cálculos en los que se suman parámetros

de carácter heterogéneo. [2] presenta una función de coste

también bastante heterogénea, en la que se combinan

características tan dispares como: la carga computacional

relativa, la uniformidad del proceso en cuanto a tipos de

operaciones distintas, el paralelismo subyacente dentro del

proceso y la adecuación para la implementación SW de sus

operaciones. Para a partir de ellos estimar la cantidad de

comunicaciones entre las particiones HW y SW, la interacción

entre los nodos que se encuentran en la partición HW y la

uniformidad de los pesos asociados a los nodos. Conceptos

todos ellos muy subjetivos e imposibles de combinar

adecuadamente en una función de coste fija. La utilización de

una función de coste tan complicada de manejar para el

diseñador, ya que ha de ajustar una gran cantidad de

parámetros para combinar las distintas características en una

única expresión, no garantiza que la solución obtenida cumpla

las restricciones tanto temporales como de área impuestas

inicialmente. Esto se debe a que no se garantiza la fidelidad

entre un valor menor de la función de coste y una mejor

solución para el sistema final implementado.

En [3] la función de coste sólo considera el tiempo de

ejecución sin tener en cuenta que cuando el objetivo de

rendimiento ya se ha conseguido es interesante mejorar algún

otro parámetro de diseño.

Este artículo presenta una función de coste sencilla, fiel y

adaptable, que considera tanto el tiempo de ejecución como el

área del diseño real, tratando de mejorar en diferente grado

uno u otro, según la situación del proceso de diseño en cada

instante. Además de hacer un especial hincapié en el efecto

del coste de las comunicaciones tanto en el rendimiento como

en el coste del sistema implementado.

2

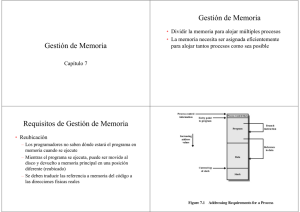

III. ARQUITECTURA DESTINO

Para la realización de este estudio se asume la utilización

de un entorno de codiseño básico formado por un

microprocesador SW y un coprocesador HW configurable, los

cuales comparten un único espacio de memoria y se

comunican mediante el bus del sistema.

El coprocesador HW y el procesador SW están trabajando

en paralelo, ya que la arquitectura no debe forzar la exclusión

mutua entre ambas plataformas. El microprocesador ofrece

además la posibilidad de interrumpir la ejecución del

programa SW cuando detecta un pulso en la señal de la línea

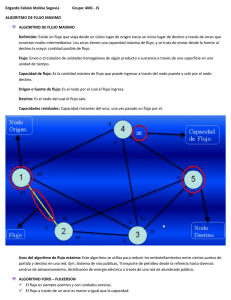

de interrupción. En la Fig. 1 se puede observar un esquema de

la arquitectura destino.

INT

µProcessor

Configurable

HW

Coprocessor

Shared Memory

Fig. 1. Arquitectrua destino.

En este tipo de sistemas la comunicación entre ambas

plataformas suele representar un cuello de botella importante

con respecto al rendimiento final del sistema. La influencia

negativa de las comunicaciones se pone todavía más de

manifiesto cuanto más rápidos son los componentes SW y

HW. Nuestra herramienta de particionamiento HW/SW tiene

en cuenta el impacto negativo de las comunicaciones, ya que a

la hora de definir estimadores necesarios para construir la

función de coste se han tenido en cuenta las características

reales del canal de comunicación entre particiones. Además se

ha desarrollado un planificador para manejar los conflictos de

acceso al canal de comunicación. Esta estimación del impacto

de las comunicaciones ha sido integrada dentro de la

herramienta de particionamiento HW/SW sin incrementar

significativamente el tiempo necesario para la exploración del

espacio de diseño. La aproximación utilizada para desarrollar

la planificación de acceso al canal de comunicación se

encuentra descrita detalladamente en [4].

IV. ALGORITMO DE PARTICIONAMIENTO

Para realizar el particionamiento se parte de una

especificación inicial del sistema a particionar en le que esté

aparece representado como un grafo dirigido y acíclico

denominado grafo de tareas. Una tarea representa una

determinada parte de la funcionalidad del sistema que va a ser

implementada de forma conjunta. En el grafo cada nodo se

corresponde con una tarea y cada arco representa un canal de

S033C07F

3

comunicación de datos entre las tareas de los nodos a los que

conecta.

Para realizar este estudio hemos utilizado como algoritmo

de particionamiento el algoritmo de búsqueda tabú [5].

La búsqueda tabú es un algoritmo determinista que parte de

una solución inicial e itera hasta una solución final, que ha de

cumplir unas determinas restricciones. Durante la exploración

del espacio de soluciones el algoritmo guarda información

relativa a los últimos movimientos realizados, para evitar

ciclos que podrían tener lugar si un determinado movimiento

llevase a visitar una solución que ya ha sido visitada

anteriormente. Para ello se utiliza una lista donde se

almacenan los movimientos inversos a los realizados,

denominada lista de movimientos tabú y que da nombre al

algoritmo.

La búsqueda tabú permite movimientos a soluciones más

costosas, para evitar que la exploración del espacio de

soluciones termine en mínimos locales. De esta forma

mediante la explotación de la información que almacena el

propio algoritmo acerca de la historia global de la búsqueda

estimula la convergencia hacia un óptimo global.

La búsqueda tabú es un algoritmo de vecindad, es decir,

una solución es candidata a ser visitada, si se obtiene mediante

el movimiento de un único nodo de la configuración actual de

una partición a otra, siempre que este movimiento no sea un

movimiento tabú.

V. GRAFO DE TAREAS

Una vez sintetizado, el sistema ha de alcanzar unas

determinadas cotas de rendimiento, en términos de velocidad

de ejecución y ciertas restricciones relativas al consumo de

recursos HW y SW. Estas cotas y restricciones vienen dadas

por el diseñador junto con la arquitectura destino en la que

será implementado el sistema. Todos estos parámetros se

definen durante la especificación inicial del sistema y han de

ser recogidos por la función de coste que guía el

particionamiento.

Para poder guiar el particionamiento a la consecución de

dichos objetivos se asigna a cada nodo y arco del grafo de

tareas unos determinados valores que recogen una serie de

características del sistema.

Para este estudio los valores asociados a los nodos indican

el tiempo de ejecución de la tarea a la que representan tanto si

se implementa en HW como en SW, y su área HW. Así como

los valores asociados a cada uno de los arcos recogen el coste

de la comunicación a la que representan, tanto en tiempo

como en área HW.

Para cada nodo que compone el grafo del sistema a

implementar vamos a calcular los siguientes parámetros:

• t_hwi = tiempo de ejecución del nodo i implementado en

HW.

• t_swi = tiempo de ejecución del nodo i implementado en

SW.

• a_hwi = área HW del nodo i implementado en HW.

No se ha tenido en cuenta el área SW de los nodos del grafo

de tareas, ya que se asume que el microprocesador tiene

suficiente memoria de datos e instrucciones para todos los

nodos de la partición SW. Si existe la posibilidad de que se

exceda la capacidad de la memoria tanto de datos o como de

instrucciones, el área SW debería ser incluida como una nueva

restricción que una solución valida debe cumplir.

Dado que el protocolo de comunicación se define de forma

distinta e independiente para cada uno de los sentidos de la

comunicación, el coste tanto en tiempo como en área de cada

una de las comunicaciones va a depender de la partición en la

que se encuentren los nodos origen y destino de la

comunicación. Si tanto el nodo origen como el nodo destino

pertenecen a la misma partición el coste de la comunicación es

nulo.

Para cada arco del grafo de tareas calculamos los siguientes

parámetros:

• t_cij = tiempo de ejecución de la comunicación entre el

nodo i y el nodo j, según los nodos i y j pertenezcan a HW

o SW.

• a_cij = área HW que supone la comunicación entre el nodo

i y el nodo j, según los nodos i y j pertenezcan a HW o SW.

El área SW de las comunicaciones, al igual que sucedía con

el área SW de los nodos, no es tenida en cuenta.

VI. FUNCIÓN DE COSTE

Una vez calculados los valores asociados a los nodos y

arcos del grafo de tareas se debe definir una función de coste

que los combine, de forma que guíe el particionamiento hacia

la consecución de los objetivos fijados inicialmente. Esta

función de coste además ha de ser sencilla de calcular, ya que

durante la exploración del espacio de diseño que realiza el

proceso de particionamiento vamos a visitar un amplio

numero de soluciones, y para cada posible nueva solución

intermedia es necesario calcular su valor. El algoritmo de

búsqueda tabú va a estar guiado por la minimización del valor

de la siguiente función de coste dinámica en el tiempo, que

varía según la solución actual se aproxime al cumplimiento de

los distintos objetivos del particionamiento:

C ( HW ,SW ) = Q1 ( t / T lim) + Q 2 ( a / A lim)

donde t es el tiempo de ejecución total del sistema. a

representa el área HW total del sistema. Tlim es el tiempo

máximo de ejecución del sistema. Alim es el área máxima del

sistema. Tlim y Alim son respectivamente las restricciones de

diseño para tiempo de ejecución y coste HW que ha de

cumplir el sistema una vez implementado. El área HW y el

tiempo de ejecución de una solución son estimados según las

siguientes expresiones:

t=

∑ t _ sw

( i )∈ Sw

a=

i

∑ a _ hw

( i )∈ Hw

+

∑ t _ hw

( i )∈ Hw

i

+

i

∑a_c

( ij )∈corte

+

∑t_c

( ij )∈ corte

ij

ij

S033C07F

donde corte es el conjunto de arcos que conectan las dos

particiones. t_swi es el tiempo de ejecución de la tarea del

nodo i si se implementa en SW. t_hwi es el tiempo de

ejecución de la tarea del nodo i si se implementa en HW. t_cij

es el tiempo necesario para realizar la comunicación entre las

tareas de los nodos i, j. a_hwi es el área HW de la tarea del

nodo i. a_cij es el área HW del driver necesario para realizar

la comunicación entre las tareas de los nodos i j. (i) es nodo i.

(ij) es el arco que conecta los nodos i y j.

Q1 y Q2 son los coeficientes que representan la influencia

relativa de cada uno de los dos términos que componen la

función de coste, tiempo de ejecución y coste HW

respectivamente, a la hora de seleccionar una nueva solución.

Estos dos coeficientes no son estáticos, sino que varían

durante la ejecución del algoritmo y dependen del grado de

adecuación de la solución actual al cumplimento de las

restricciones de diseño. La elección de una función de coste

dinámica viene motivada por el hecho de que una función que

se adapta a las características de la solución actual focaliza

más rápidamente la búsqueda.

Dicha función de coste dinámica nos ofrece además la

posibilidad de centrar la búsqueda en la optimización del

tiempo de ejecución o del área HW del sistema una vez

encontrada una primera solución que cumple las restricciones

iniciales de diseño. La actualización de los valores de Q1 y Q2

se lleva a cabo según la expresión de la Fig. 2, si la búsqueda

optimiza el tiempo.

if t >> Tlim then Q1 >> Q2

elsif t >≈ Tlim then

if a >> Alim then Q2 >> Q1

elsif a >≈ Alim then Q2 ≈ Q1

endif

elsif t < Tlim then

if a >> Alim then Q2 >> Q1

elsif a >≈ Alim then Q2 ≈ Q1

elsif a < Alim then Q1 >> Q2

/* 1ª solución valida encontrada */

endif

endif

Fig. 2. Pseudo-código del algoritmo de actualización de la función

de coste

De esta forma durante la exploración del espacio de

soluciones anteponemos el cumplimiento y posterior

optimización de las restricciones temporales, al cumplimiento

y optimización del coste HW. Si por el contrarío preferimos

que la búsqueda se centre primero en el cumplimiento y

optimización del área HW tendríamos una expresión idéntica

en la que se habrían reemplazado las expresiones temporales

por las expresiones de área y viceversa.

Una vez encontrada una solución que cumple las

restricciones tanto temporales como de área, los coeficientes

Q1 y Q2 son adaptados al objetivo de optimización fijado por

el diseñador.

4

VII. RESULTADOS EXPERIMENTALES

En los resultados experimentales obtenidos en este estudio

queda reflejada la importancia de la elección de una función

de coste que garantice la calidad del particionamiento

HW/SW. Para la realización de este estudio hemos

desarrollado una herramienta de particionamiento que

implementa el algoritmo de búsqueda tabú para dos funciones

de coste distintas. La primera fue aplicada por primera vez al

problema del particionamiento HW/SW en [2]. Esta función

de coste mezcla tres parámetros muy abstractos y

heterogéneos, como son, la cantidad de comunicaciones entre

las particiones HW y SW, la interacción entre los nodos que

se encuentran en la partición HW y la uniformidad de los

pesos asociados a los nodos. Estos tres parámetros son a su

vez estimados a partir de otras cuatro característica también

muy abstractas y heterogéneas: carga computacional relativa

de cada nodo, uniformidad del nodo en cuanto a tipos de

operaciones distintas, paralelismo subyacente dentro cada

nodo y adecuación para la implementación SW de sus

operaciones. Los tres parámetros que constituyen esta función

de coste a menudo compiten entre sí. Esta competencia es

regulada mediante la utilización de coeficientes, que los

diseñadores deben de determinar para controlar la influencia

relativa de las diferentes componentes. En este estudio se

muestra una comparativa entre los resultados obtenidos

utilizando la función de coste de [2] y la función de coste

dinámica descrita en el apartado anterior.

Para ello hemos realizado una gran cantidad de medidas

aplicando la herramienta de particionamiento a una aplicación

de reconocimiento de patrones. Esta aplicación realiza la

transformada de Hough [6] sobre una imagen dada, en la cual

se busca la existencia de figuras geométricas simples

predefinidas. Este tipo de aplicaciones son empleadas

normalmente en robótica y para el análisis de datos

astronómicos [7].

Para poder realizar una estimación adecuada del tiempo de

ejecución y del área HW de las comunicaciones, se ha

desarrollado un protocolo de comunicación entre las

plataformas HW y SW. Este protocolo de comunicación se ha

diseñado mediante el uso de memoria compartida e

interrupciones, teniendo en cuanta las características de la

arquitectura destino presentadas en la sección 3.

Para determinar los valores asociados a los nodos y a los

arcos del grafo de tareas se utilizan los resultados obtenidos

del estudio de la especificación inicial del sistema con

respecto a una arquitectura destino especifica y el protocolo

de comunicaciones HW/SW definido. En nuestro entorno de

cosdiseño la especificación inicial del sistema viene dada en

VHDL y C. El área HW y el tiempo de ejecución HW de cada

nodo, así como el área HW de las comunicaciones es estimado

mediante las herramientas de implementación y verificación

de XILINX Foundation. Para estimar el tiempo de ejecución

SW se ha utilizado un traductor automático ensamblador

8051/C.

Una vez completada la especificación inicial del sistema a

S033C07F

particionar en forma de grafo de tareas, dicho grafo de tareas

se pasa a la herramienta de particionamiento. Para obtener

distintas medidas se ha repetido el particionamiento para

distintas restricciones de área HW y tiempo de ejecución.

Para ilustrar este estudio se ha llevado a cabo dos conjuntos

de experimentos distintos. En el primero se ha impuesto una

restricción temporal, el algoritmo una vez encuentra una

solución que cumple las restricciones de diseño evoluciona

para mejorar el área HW. Para acotar el espacio de búsqueda

se fija también una restricción de coste HW máximo. En la

tabla I se muestran los resultados obtenidos para una

restricción temporal de 9500 unidades de tiempo

normalizadas, y distintos valores para la restricción de coste

HW máximo. La última fila de la tabla muestra el porcentaje

de optimización en área HW conseguido para la función de

coste dinámica propuesta con respecto a la función de coste

presentada en [2].

En el segundo conjunto de experimentos se ha fijado una

restricción de 350 unidades de área normalizadas y diferentes

cotas máximas para el tiempo de ejecución. Los resultados de

este conjunto de experimentos se muestran en la tabla II.

De los datos expuestos en la tabla I y en la tabla II, se

deduce que los resultados obtenidos por la herramienta de

particionamiento con la función de coste dinámica son

mejores que los obtenidos con la función de coste presentada

en [2]. Cuando el objetivo del particionamiento es cumplir la

restricción de tiempo y minimizar el área HW, nuestra función

de coste obtiene un ahorro en área superior en algunos casos

al 30% (20% aproximadamente en media), cumpliendo la

misma restricción temporal. Cuando el objetivo es cumplir la

restricción de área HW y minimizar el tiempo de ejecución,

nuestra función de coste reduce en media un 46% el tiempo de

ejecución. Esto es debido a que la función de coste dinámica

utiliza directamente los dos principales parámetros de diseño,

el área HW y el tiempo de ejecución, mientras que la otra

función de coste utiliza medidas indirectas de estos

parámetros de diseño. Por lo tanto, nuestra función de coste

tiene una mayor fiabilidad en términos de coste HW y tiempo

de ejecución que la función de coste [2], de acuerdo con la

definición de fidelidad en [8]. El echo de que en [2] la función

de coste sea el resultado de la combinación de varios factores

heterogéneos, que no reflejan las características resles de

diseño. Esta característica junto con el hecho de que dicha

función de coste no garantiza la fidelidad entre un valor menor

de la función de coste y una mejor solución para el sistema

final implementado, da lugar a situaciones en las cuales aun

existiendo una solución que cumpla las restricciones

impuestas, el algoritmo de particionamiento es incapaz de

encontrar una solución válida. Podemos observar un ejemplo

de ello en la ultima columna de la tabla I donde aun existiendo

soluciones validas la herramienta de particionamiento es

incapaz de encontrar una. Sin embargo cuando la herramienta

de particionamiento utiliza la función de coste presentada en

este articulo es siempre capaz de encontrar soluciones validas.

Esto es debido a que la convergencia fiable hacia soluciones

que representen una mejor opción de implementación es

5

mucho más fácil de conseguir utilizando funciones de coste en

las que se relaciona de forma intuitiva los objetivos

principales del particionamiento HW/SW.

Otro hecho importante a tener en cuenta es que aun

utilizando distintas funciones de coste, el número de

iteraciones es similar para cada uno de los procesos de

particionamiento realizados. Es de resaltar que con nuestra

función de coste se obtienen mejores soluciones de

particionamiento que las obtenidas con la función de coste [2]

para tiempos de computación muy parecidos.

En la tabla III y en la tabla IV se muestran los resultados

obtenidos por la herramienta de particionamiento propuesta en

este estudio. En la tabla III se presentan los resultados

experimentales obtenidos al identificar la función de coste con

la minimización del área HW, una vez se han cumplido todas

las restricciones del particionamiento. En la tabla IV se

muestran los resultados para el mismo tipo de estudio

identificando esta vez la función de coste con el tiempo de

ejecución. En la tabla III se muestra el área HW y el tiempo de

ejecución de la primera solución encontrada que cumple las

restricciones, el área HW y el tiempo de ejecución de la

solución final del particionamiento, así como el porcentaje de

optimización en coste entre ambas soluciones. En la tabla IV

se muestra el tiempo de ejecución y coste HW de la primera

solución que cumple las restricciones, el tiempo de ejecución

y coste de la solución final del particionamiento, así como el

porcentaje de optimización medio entre ambas soluciones con

respecto al tiempo.

Como ya hemos comentado el proceso de particionamiento

HW/SW guiado por muestra función de coste permite

focalizar la búsqueda en la minimización de uno de los

objetivos de diseño, una vez cumplidas las restricciones

iniciales del partricionamiento. En las tablas III y IV se

observa que el porcentaje optimización es en área HW en

media del 16%, y en tiempo de ejecución del 41% con

respecto a la primera solución encontrada que cumple las

restricciones de diseño.

VIII. CONCLUSIONES TRABAJO FUTURO

Este estudio pone de relieve la importancia de la elección

de una función de coste adecuada para garantizar la calidad de

los resultados del particionamiento HW/SW. Nuestra función

de coste dinámica analiza directamente los dos parámetros

principales de diseño, área HW y tiempo de ejecución. Por lo

tanto, esta función de coste tiene mucha más fiabilidad en

terminos de área y tiempo de ejecución que aquellas funciones

de coste que mezclan características heterogéneas.

La falta de fidelidad de este tipo de funciones de coste

puede llevar al proceso de particionamiento a realizar una

exploración ineficiente del espacio de soluciones. Además

cuando utilizamos nuestra función de coste la misma

herramienta de particionamiento es capaz de realizar una

mejor exploración del espacio de diseño minimizando el

tiempo de ejecución y el área de la solución final, sin

incrementar el tiempo de computo necesario para llevar a cabo

S033C07F

6

el proceso de particionamiento. En este articulo hemos

presentado una herramienta de particionamiento HW/SW que

minimiza el tiempo de ejecución y el área HW. En el futuro se

ampliará dicha función de coste para que considere también la

minimización del consumo de potencia del diseño como otro

nuevo objetivo de particionamiento.

Tabla I. Resultados del particionamiento para distintas restricciones de área y una misma restricción temporal,

optimizando en área para la búsqueda guiada por la función de coste dinámica.

Cota máxima de Área

350

325

300

275

250

dinámica

[2]

dinámica

[2]

dinámica

[2]

dinámica

[2]

dinámica

[2]

Función de coste

# Iteraciones algoritmo

420

407

407

441

412

405

410

423

416

446

Área solución final

236

338

250

321

244

300

250

274

223

---Tiempo solución final

9336 8892 8436 4428 8700 9216 8436 8292 8772 ---%Optimización área (dinámica respecto [2])

30,18%

22,12%

18,67%

8,76%

---Tabla II. Resultados del particionamiento para distintas restricciones temporales y una misma restricción de área,

optimizando en tiempo de ejecución para la búsqueda guiada por la función de coste dinámica.

Cota máxima de Tiempo

9500

9000

8500

8000

7500

dinámica

[2]

dinámica

[2]

dinámica

[2]

dinámica

[2]

dinámica

[2]

Función de coste

# Iteraciones algoritmo

410

424

409

420

409

421

404

435

406

436

Área solución final

276

300

284

276

276

293

300

298

276

293

Tiempo solución final

4440 9216 4440 8904 4440 7428 3996 7848 4440 7428

%Optimización tiempo (dinámica respecto [2])

51,82%

50,13%

40,23%

49,08%

40,23%

Tabla III. Resultados del particionamiento guiado por la función de coste dinámica, optimizando en área.

Cota máxima de Área

350

325

300

275

250

1ª

final

1ª

final

1ª

final

1ª

final

1ª

final

Solución

# Iteraciones algoritmo

5

232

3

270

10

258

9

209

12

233

Área solución

315

236

311

250

296

244

274

250

250

223

Tiempo solución

6372 9336 7920 8436 4920 8700 9192 8436 7512 8772

% Optimización área (final con respecto 1ª)

25,08%

19,61%

17,57%

8,76%

10,80%

Tabla IV. Resultados del particionamiento guiado por la función de coste dinámica, optimizando en tiempo.

Cota máxima de Tiempo

9500

9000

8500

8000

7500

1ª

final

1ª

final

1ª

final

1ª

final

1ª

final

Solución

# Iteraciones algoritmo

4

309

5

284

5

308

6

196

9

313

Área solución

279

276

276

284

294

276

277

300

267

276

Tiempo solución

7320 4440 8796 4440 8016 4440 7416 3996 6036 4440

% Optimización en tiempo (final con respecto 1ª)

39,34%

49,52%

44,61%

46,12%

26,44%

[7]

REFERENCIAS

[1]

[2]

[3]

[4]

[5]

[6]

“A Global Criticality/Local Phase Driven Algorithm for the Constrained

HW/SW Partitioning Problem”, A. Kalavade, E.A. Lee, Codes/Cashe'94.

“System Level HW/SW Partitioning based on simulated Annealing and

Tabu Search”, P. Eles, Z. Peng, K. Kuchcinski, A. Doboli. Design

Automation for Embedded Systems, Enero 1997.

“Hardware-Software Co-Design of Embedded Reconfigurable

Architectures”, Y. Li, T. Callahan, E. Darnell, R. Harr, U. Kurkure,

J.Stockwood, DAC’2000.

“Analyzing Communication Overhead during Hardware/Software

Partitioning” J. Resano, E. Pérez, D. Mozos, H. Mecha, J. Septién. First

International Wokshop on Embedded System Codesign ESCODES'02,

pp. 16-21 California 2002.

“Scheduling. Theory, algorithms, and systems”, M. Pinedo, Prentice

Hall, 2002.

“Introduction to Parallel Algorithms and Architectures”, F. Thomson

Leighton., pg 210-213. Morgan Kaufmann Publishers 1992.

[8]

“Applications of the Hough Transform”, P. Ballester. Astronomical Data

Analysis Software and Systems III, ASP Conference Series, Vol. 61,

1994.

“Specification and design of embedded systems”, D. D. Gajski, F.

Vahid, S. Narayan, J. Gong, Prentice Hall, 1994.