Circuitos Lógicos Combinatorios

Anuncio

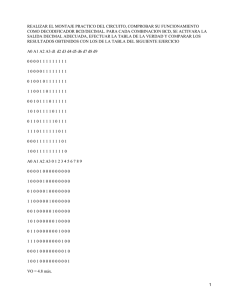

Ing. Yesid E. Santafe Ramon CIRCUITOS LÓGICOS COMBINATORIOS La evolución de la electrónica digital ha llevado a la comercialización de circuitos integrados de media escala de integración (MSI) que representan soluciones ya hechas a una gran variedad de problemas de lógica combinacional y secuencial. Así como su utilización y adaptación a diversos problemas mediante la lógica SSI (pequeña escala de integración) CIRCUITOS COMBINATORIOS Un circuito combinatorio es un arreglo de compuertas lógicas con un conjunto de entradas y salidas. En cualquier momento, los valores binarios de las salidas son una combinación binarias de las entradas. DIAGRAMA DE UN CIRCUITO COMBINATORIO n variables de entrada Circuito Combinatorio m variables de salida USO Los circuitos combinatorios se emplean en las computadoras digitales para generar decisiones de control binarias y para proporcionar los componentes digitales requeridos para el procesamiento de datos. ANÁLISIS DE UN C.C. El análisis de un C.C. inicia con un diagrama de circuito lógico determinado y culmina con un conjunto de funciones booleanas o una tabla de verdad. Ejemplo Semisumador Sumador Completo DISEÑO DE UN C.C. El diseño de un circuito combinatorio parte del planteamiento verbal del problema y termina con un diagrama lógico. El procedimiento es el siguiente: 1. 2. 3. 4. 5. Se establece el problema Se asignan símbolos a las variables de entrada y salida. Se extrae la tabla de verdad. Se obtienen las funciones booleanas simplificadas. Se traza el diagrama lógico EJEMPLOS DE DISEÑO Comparador de magnitud Medio sumador Sumador Completo Medio Restador Restador Completo Decodificador Multiplexor SEMISUMADOR (MEDIO SUMADOR O HALF ADDER) El circuito aritmético digital más simple es el de la suma de dos dígitos binarios. Un circuito combinatorio que ejecuta la suma de dos bits se llama semisumador Implementarlo DIAGRAMA LÓGICO DEL MEDIO-SUMADOR HALF-ADDER SUMADOR COMPLETO Otro método para sumar dos números de n bits consiste en utilizar circuitos separados para cada par correspondiente de bits: los dos bits que se van a sumar, junto con el acarreo resultante de la suma de los bits menos significativos, lo cual producirá como salidas un bit de la suma y un bit del acarreo de salida del bit más signifcativo. DIAGRAMA EN BLOQUE DE UN SUMADOR COMPLETO (FULL ADDER) Xi Si Full Adder F.A. Yi Ci+1 Ci Sumador completo de dos palabras de un bit IMPLEMENTACIÓN DE UN FA CON DOS HA • Un sumador completo resulta de la unión de dos medios sumadores. SUMADORES EN CASCADA Es posible realizar sumas de dos palabras de n bits, usando n sumadores completos en cascada, esto quiere decir que los acarreos de salida de los bits menos significativos deberán estar conectadas a las entradas de acarreo de los bits más significativos IMPLEMENTACIÓN DE UN SUMADOR EN CASCADA Para dos palabras de 4 bits. SUMADOR/RESTADOR A-B = A+B’+1, para realizar el complemento se usan las compuertas xor. MULTIPLEXORES Y DEMULTIPLEXORES La idea fundamental en la utilización de multiplexores (MUX) y demultiplexores (DEMUX) es el ahorro de líneas de comunicación, es decir, el uso de una sola línea para realizar múltiples funciones, o para conectar a través de ella múltiples fuentes de información o señales a transmitir. MULTIPLEXORES (SELECTORES) Existen dos tipos básicos de Multiplexores: De varias entradas a una salida, llamados de selectores de 2n a 1, o simplemente MUX (del inglés multiplexer) de 2n a 1. De una entrada a varias salidas, llamados selectores de 1 a 2n o simplemente DEMUX (del inglés demultiplexer) de 2n a 1. MULTIPLEXORES Definición Un multiplexor digital es un circuito con 2n líneas de entrada de datos y una línea de salida; también debe tener una manera de determinar la línea de entrada de datos específica que se va a seleccionar en cualquier momento. Esto se efectúa con otras n líneas de entrada, denominadas entradas de selección, cuya función es elegir una de las 2n entradas de datos para la conexión con la salida MULTIPLEXORES Problemática Los datos que se generan en una localidad se van a usar en otra, para esto se necesita un método para transmitirlos de una localidad a otra a través de algún canal de comunicaciones. Entrada de datos . . . Canal de comunicaciones . . . demultiplexor multiplexor Salida de datos DISEÑAR UN MUX DE 4 A 1 Solución: Para seleccionar 4=2^2 lineas de datos se requieren 2 lineas de selección, por lo tanto, el diagrama de bloques del circuito a diseñar es como sigue Como se puede ver, la tabla de verdad para describir el funcionamiento del circuito anterior requerirá 2^6= 64 renglones, por ello, en este caso se presenta una versión reducida de dicha tabla, para lograr esta versión reducida consideramos sólo como entradas las lineas de selección B, A y escribimos la salida en términos de las otras cuatro entradas: Este tipo de tabla de verdad se denomina Tabla de Verdad con Variables Introducidas, dado que para formarla se han introducido las 4 variables de entrada D0, D1, D2, D3 que en una tabla de verdad normal irían afuera de la tabla MULTIPLEXOR 4X1 La siguiente es una lista de los MUX de circuito integrado más populares de la familia TTL: 74157: Cuatro mux de 2 a 1 con señal strobe 74158: Cuatro mux de 2 a 1 con señal strobe salidas invertidas 74153: Dos mux de 4 a 1 con strobe 74151: Un mux de 8 a 1 (salida invertida y sin invertir), con strobe 74152: Un mux de 8 a 1 (salida invertida) 74150: Un mux de 16 a 1 con strobe MULTIPLEXOR 8 A 1 si se tiene duda de como funciona exactamente el circuito, se puede consultar la tabla de verdad en las hojas de datos del fabricante, como se muestra a continuación. En esta tabla se aclara el funcionamiento de la entrada “strobe” (S) que como se puede ver es una señal de habilitación/deshabilitación del mux. La señal Strobe (S) permite la interconexión de un mux con otros mux para expandir su capacidad a un mayor número de entradas TABLA DE FUNCIÓN DE UN MUX 4 A 1 Selección Salida S1 S0 Y 0 0 I0 0 1 I1 1 0 I2 1 1 I3 Esta tabla demuestra la relación entre las cuatro entradas De datos y la salida única como función de las entradas de Selección S1 y S0. MUX 8X1 PROBLEMA Implementación de un mux de 16 a 1 usando circuitos 74151. DECODIFICADORES Las cantidades discretas de información se representan en sistemas digitales con códigos binarios (ejemplo: BCD, EXCESO 3, 84-2-1, 2421, etc.). Un código binario de n bits es capaz de representar hasta 2n elementos distintos de información codificada. Un decodificador es un circuito combinatorio que convierte información binaria de n líneas de entrada a un máximo de 2n líneas únicas de salida o menos. Estos decodificadores son denominados decodificadores n-a-m líneas, donde m 2n. DECODIFICADORES Estos dispositivos normalmente cuentan con una entrada habilitadora. Cuando esta entrada vale 0, todas las salidas del codificador son 0. Cuando la entrada habilitadora vale 1, la salida correspondiente al minitérmino formado por la combinación presente en las n entradas tomará el valor 1 y las demás tomarán el valor 0. DECODIFICADOR 2 X 4 Un valor de x en las entradas indica que puede tomar el valor de 1 o 0. DEC 2x4 Hab. C1 C0 0 1 1 1 1 X 0 0 1 1 X 0 1 0 1 S0 S1 S2 S3 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 DECODIFICADOR 2X4 Las funciones lógicas para las salidas del codificador 2x4 son: S0 HC1C0 S1 HC1C0 S0 HC1C0 S0 HC1C0 DECODIFICADORES De forma semejante a como se define el decodificador 2x4, pueden definirse decodificadores de 3x8, 4x16, 5x32 y en forma general de nx2n. La principal utilización de este dispositivo es cuando se tiene N alternativas que se pueden seleccionar, pero se desea seleccionar solamente una de ella. También puede ser usado para construir funciones lógicas… ver ejemplo. EJEMPLO Diseño de un demux de 2 a 4, El diagrama de bloques correspondiente a un demux de 2 a 4 es como sigue De la tabla de verdad obtenemos con un poco de análisis :Yo = BAE, Y1 = BAE,Y2 = BAE, Y3 = BAE, lo cual nos conduce a la implementación que se muestra en la siguiente figura DECODIFICADOR 3X8 En la actualidad se tienen varios demultiplexores en circuito integrado. Por ejemplo, un circuito equivalente al diseñado en el ejemplo es el 74155. El 74155 es un CI que se puede usar como dos decodificadores de 2 a 4 ó bien como dos demultiplexores de 1 a 4 ó, como un decodificador de 3 a 8 ó un demultiplexor de 1 a 8. Ya que como ya se dijo, un demultiplexor se convierte en un decodificador al conectar su entrada a un estado lógico fijo. La siguiente es una lista de los demultiplexores/decodificadores más populares en cicuito integrado de la familia TTL 74138: Demux/decodificador de 3 a 8 74139: Demux/decodificador de 2 a 4, doble 74141: Decodificador/driver BCD - decimal 74154: Demux/Decodificador de 4 a 16 74159: Demux/decodificador de 4 a 16 con salidas de colector abierto 74155: Demux/decodificador doble de 2 a 4 74156: igual al 74155, pero con salidas de colector abierto. EJEMPLO En la siguiente figura se muestra como se implementaría un demux de 1 a 16 usando circuitos 74138 Existen algunos paquetes en circuito integrado que realizan funciones lógicas muy usuales y que representan una ligera variante a los decodificadores mencionados anteriormente, tales decodificadores especiales son:). 7445: Decodificador/driver de BCD a decimal (decodificador de 4 a 10 con capacidad de alta corriente (80 mA por salida). tiene salidas activas en bajo 7446, 7447: Decodificadores /driver de BCD a 7 segmentos con salidas de colector abierto. Estos circuitos manejan alto voltaje de salida (15 volts para el 7447 y 30 volts para el 7446). manejan alta corriente de salida y tienen salidas activas en bajo, lo cual los hace compatibles con desplegadores de 7 segmentos de ánodo común 7449: Decodificador/driver de BCD a 7 segmentos con salidas activas en alto (compatible con desplegadores de cátodo común). LT (Lamp Test).- Cuando esta señal se activa (en bajo) todas las salidas de segmento se activan. Esto sirve para probar si los leds del desplegador están o no en buen estado, ya que en esta condición todos deberán encender, si no es así, probablemente alguno este dañado). RBI/RBO (Right Blank Input/Output).- Esta es una salida de colector abierto que funciona en conjunción con la entrada RBI que se explica a continuación RBI (Right Blank Input).- Cuando esta entrada es activada (en bajo) y el dato BCD de entrada al 7447 es cero (DCBA = 0000) en lugar de activar el código de 7 segmentos del cero, apaga todos los segmentos y además activa RBO (en bajo). CODIFICADOR Un codificador es un circuito digital que ejecuta la operación inversa de un decodificador. Un codificador tiene 2n (o menos) líneas de entrada y n líneas de salida. Las líneas de salida generan un código binario correspondiente al valor de entrada binario. Ver codificador de octal a binario (tabla 2-2). CODIFICADOR OCTAL A BINARIO Entradas Salidas D7 D6 D5 D4 D3 D2 D1 D0 A2 A1 A0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 1 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 0 1 0 1 0 0 0 0 0 0 1 1 0 1 0 0 0 0 0 0 0 1 1 1 CODIFICADOR OCTAL A BINARIO El codificador puede implantarse con compuertas OR cuyas entradas se determinan directamente de la tabla de verdad. Por ejemplo, la salida es A0 será igual a 1 si el digito octal de entrada es 1 o 3 o 5 o 7. Las funciones de este codificador son las siguientes: A0 = D1+D3+D5+D7 A1 = D2+D3+D6+D7 A3 = D4+D5+D6+D7 CODIFICACIÓN DE TECLADOS Los teclados numéricos y alfanuméricos son un dispositivo extremadamente útil para la introducción de datos a un sistema digital. Las teclas de un teclado normalmente accionan interruptores que tienen dos contactos normalmente abiertos que se cierran cuando la tecla es presionada. Codificar un teclado significa asignar un código binario a cada una de las teclas que componen el teclado. Así como decodificarlo significa determinar cual de las teclas fue presionada de acuerdo al código que la representa. La codificación de teclados se puede realizar usando multiplexores y demultiplexores Como ejemplo enseguida se ilustra un esquema para codificar 64 teclas arregladas en una matriz de 8x8, usando un 74155 (como decodificador de 3 a 8) y un multiplexor 74152. En este ejemplo un nivel ALTO en la salida del 74152 indica que una tecla se oprimió y la combinación de las 3 entradas de selección del 74152 con las del 74155 determinan cual fue la tecla que se oprimió GRACIAS