Relc_tm5

Anuncio

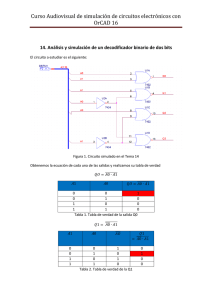

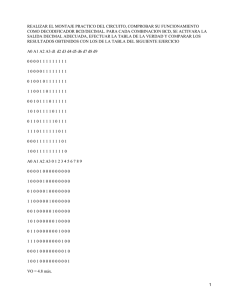

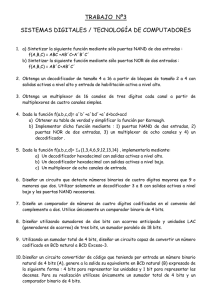

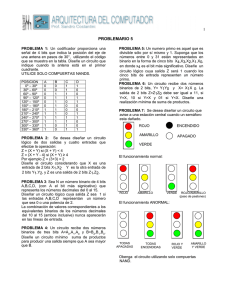

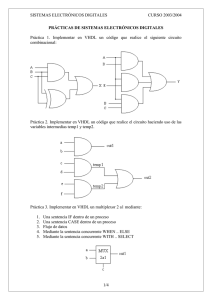

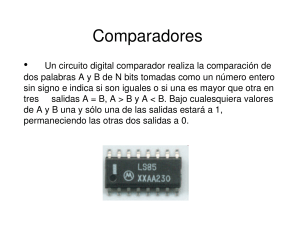

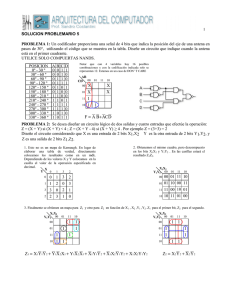

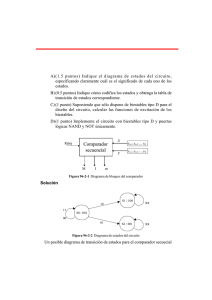

Escuela Técnica Superior de Ingenieros en Informática Sistemas Electrónicos Digitales Relación de Problemas del Capítulo 5 1.- Se dispone de decodificadores completos 2:4 con señal EN activa en valor alto (H). Realizar: a) Un decodificador 1:2 de las mismas características. b) Un decodificador 3:8 de las mismas características. c) Un decodificador 4:16 de las mismas características. d) Un decodificador decimal de las mismas características 2.- Realizar con decodificadores las funciones: a) f = (0, 2, 4, 6, 8, 10, 11, 12, 18, 20, 22, 26, 27) b) f = (0, 2, 9, 11, 13, 15, 16, 18, 25, 27, 28, 31) c) f = b c d + a b d + a b d e + a b c + a b d e + a b d + d Siendo d = d(a, b, c, d, e) = a b c d e + a b d e d) f = (0, 1, 3, 8, 9, 11, 15, 16, 17, 19, 24, 25, 29, 30, 31) e) f = (0, 1, 4, 5, 6, 7, 8, 9, 10, 12, 14, ) f) f = (0, 2, 3, 7, 8, 10, 11, 12, 14) g) f = (0, 1, 2, 3, 4, 6, 9, 10, 15, 16, 17, 18, 19, 20, 23, 25, 26, 31) h) f = (0, 2, 4, 5, 7, 8, 16, 18, 24, 32, 36, 40, 48, 56) i) f1 = (0, 1, 2, 3, 6, 7) f2 = (0, 1, 6, 7, 14, 15) f3 = (0, 1, 2, 3, 8, 9) j) f1 = (4, 5, 10, 11, 12) f2 = (0, 1, 3, 4, 8, 11) f3 = (0, 4, 10, 12, 14) k) f1 = (0, 1, 2, 3, 6, 7, 20, 21, 26, 27, 28) f2 = (0, 1, 6, 7, 14, 15, 16, 17, 19, 20, 24, 27) f3 = (0, 1, 2, 3, 8, 9, 16, 20, 26, 28, 30) l) f1 = (0, 1, 2, 8, 9, 10, 13, 16, 17, 18, 19, 24, 25) f2 = (0, 1, 3, 5, 7, 9, 13, 16, 17, 22, 23, 30, 31) f3 = (2, 3, 8, 9, 10, 11, 13, 15, 16, 17, 18, 19, 22, 23) 3.- Dado el circuito de la figura, donde el decodificador tiene salidas activas bajas, determine la expresión de conmutación mínima para f(W,X,Y,Z) en forma de suma de productos. 4.- Diseñe un circuito lógico que convierta un número de cuatro bits de formato signomagnitud al formato complemento a 2 5.- Realizar un convertidor de código para cada uno de los casos siguientes: BCD exceso-3, binario BCD, binario exceso-3. En cada uno de los casos utilizar módulos MSI de decodificación y/o codificación, describiéndolos adecuadamente. 6.- Diseñe un circuito codificador 4 a 2 con prioridad que sólo utilice puertas NOR. Las entradas a3a2a1a0, donde a3 tiene la máxima prioridad y a0 la mínima. Las salidas son y1y0, que indican la entrada activa con mayor prioridad, y G, la cual indica que al menos una entrada está activa. 7.- La figura representa un comparador de 2 bits con la señal de habilitación. Diseñar un comparador: a) de 3 bits ; b) de 4 bits; c) de 5 bits ; d) de 8 bit. Utilizar el comparador de la figura y, si es necesario, puertas lógicas, como elementos de diseño. 8.- Contestar si es posible construir un MUX-n usando como elemento MUX-m en los casos: a) m < n ; b) m > n. En caso afirmativo, proponer un ejemplo. 9.- Un MUX-n puede realizar una función de n + 1 variables si existe alguna entre ellas en doble rail. Esta función también puede ser realizada utilizando MUX-m, con m < n. Discutir el coste (número de módulos, número de terminales, número de conexiones, etc.) de cada una de esas lineas de diseño. 10.- Analizar el circuito de la figura. 11.- Analizar el circuito de la figura. 12.- Realizar la función f = (1,2,3,6,7) con MUX de 1, de 2 y de 3 variables de control. Discutir el coste y dar la solución óptima razonable. 13.- Sea f(a, b, c, d, e) = (0, 1, 2, 3, 5, 7, 8, 9, 10, 11, 13, 15, 17, 19, 21, 23, 24, 25, 26, 27, 29, 31). Realizar esta función en los siguientes casos: a)Con MUX-2, y a b como variables de control en el primer nivel. b)Con MUX-2, sabiendo que sólo la variable b está en doble rail c)Con MUX-2, sabiendo que sólo la variable e está en doble rail y que b en variable de control en el primer nivel. 14.- Realizar con MUX-2 la función f = x2x3 + x1x4x5 + x1x2x4 + x1x4x5 + x1x3x5 + x3x4x5. 15.- Repetir el problema anterior con MUX-3. 16.- Sea la función f = x1x2 + x1x2x3 + x1x3x4, realizarla con MUX-1 y MUX-2: a) MUX-2 en el nivel de salida y MUX-1 en el nivel de entrada. b)MUX-1 en el nivel de salida y MUX-2 en el nivel de entrada 17.- Realizar a nivel de puertas un DEMUX (1:2): a) con puertas AND; b con puertas NAND. Utilizar este módulo para realizar un DEMUX (1:4). 18.- Diseñe un comparador de magnitud de 3 bits con entradas A = (a2a1a0)2 y B = (b2b1b0)2 y tres salidas: EQ(A = B), GT(A > B) y LT(A < B).