Práctico 9

Anuncio

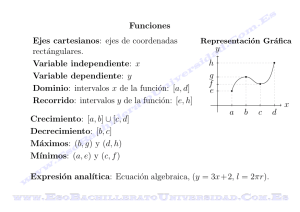

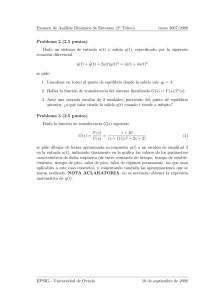

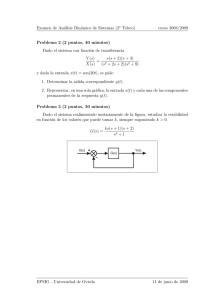

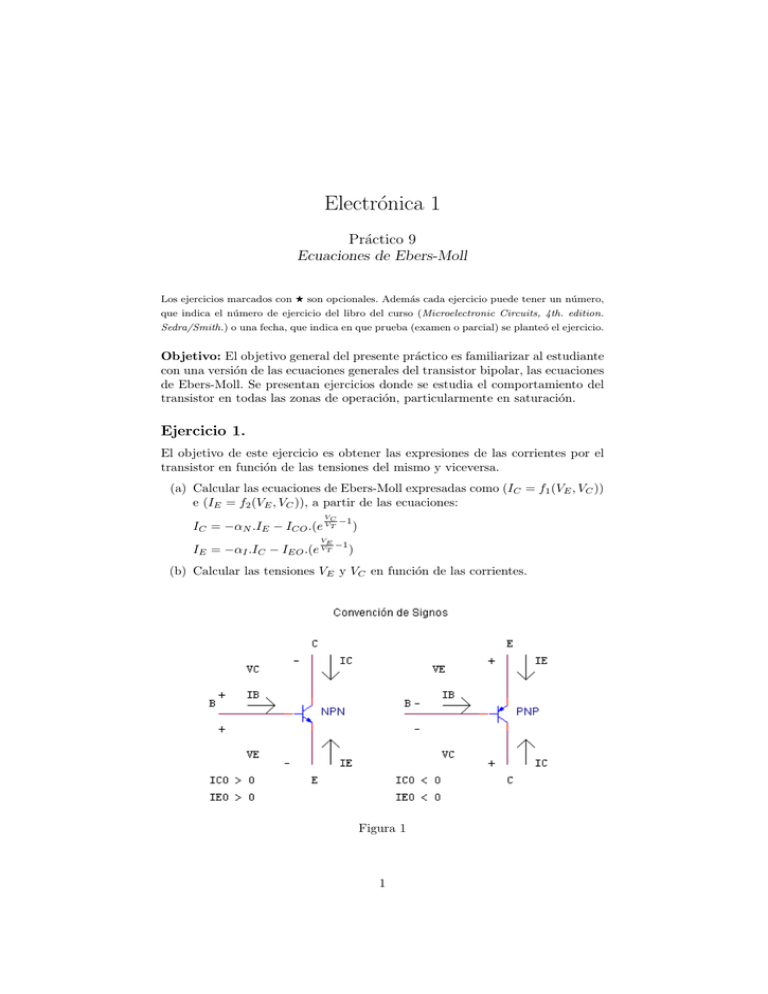

Electrónica 1 Práctico 9 Ecuaciones de Ebers-Moll Los ejercicios marcados con H son opcionales. Además cada ejercicio puede tener un número, que indica el número de ejercicio del libro del curso (Microelectronic Circuits, 4th. edition. Sedra/Smith.) o una fecha, que indica en que prueba (examen o parcial) se planteó el ejercicio. Objetivo: El objetivo general del presente práctico es familiarizar al estudiante con una versión de las ecuaciones generales del transistor bipolar, las ecuaciones de Ebers-Moll. Se presentan ejercicios donde se estudia el comportamiento del transistor en todas las zonas de operación, particularmente en saturación. Ejercicio 1. El objetivo de este ejercicio es obtener las expresiones de las corrientes por el transistor en función de las tensiones del mismo y viceversa. (a) Calcular las ecuaciones de Ebers-Moll expresadas como (IC = f1 (VE , VC )) e (IE = f2 (VE , VC )), a partir de las ecuaciones: VC IC = −αN .IE − ICO .(e VT IE = −αI .IC − IEO .(e VE VT −1 −1 ) ) (b) Calcular las tensiones VE y VC en función de las corrientes. Figura 1 1 Ejercicio 2. Este ejercicio aprovecha la validez general de la ecuaciones de Ebers y Moll para deducir la expresión de la caracterı́stica de salida VCE = f (IC , IB ), incluyendo la zona de saturación. (a) Demostrar que la expresión exacta de las caracterı́stica de salida en emisor comun de un transistor es: αN IE0 + IE + IC . (1 − αI ) VCE = ±VT log + log αI IC0 + αN IE − IC (1 − αN ) valiendo el signo ”+”para el NPN y el signo ”−”para el PNP. (b) Hallar y graficar la expresión simplificada si se cumple que: IB >> IE0 y αI αN y βI = (1−α . αN .IB >> IC0 . Expresarla en función de βN = (1−α N) I) En las partes (c) y (d) se aprovecha el resultado anterior para ver como la tensión VCE en saturación depende de cuan saturado este el transistor es decir del cociente iC /iB . (c) A partir de la expresión de la parte b) determinar una expresión para VCESAT = f (iC /iB ) (d) Graficar la misma en función de iC /iB para βN = 100, βI = 0, 05 e iC /iB entre 0 y N. Los ejercicios siguientes aprovechan las ecuaciones de Ebers y Moll para modelar diferentes formas de implementar un diodo a partir de un transistor bipolar. Ejercicio 3. Figura 3 (a) Derivar las expresiones de la caracterı́stica i-v de los transistores de la Figura 3 (conectados como diodos) en función de IS , αN , αI (IS = αN ISE = αI ISC ). (b) Cuando los dos transistores son idénticos y las corrientes i son iguales a un cierto valor I, se encuentra que la tensión v en (a) es de 0.7V y la tensión v en (b) es 0.6V . Con esto en cuenta hallar los tamaños relativos de las junturas emisor-base y colector-base 2 . Ejercicio 4. (a) Para el transistor de la Figura 4 hallar expresiones para iE e i en función de v, Is , βI y βN ( IS = αN ISE = αI ISC ). (b) Hallar la relación entre ambas corrientes (iE /i) Figura 4 Ejercicio 5. Para los transistores de la Figura 5 se tiene que: αN = 0.99 ; IE0 = −1.6nA e IC0 = −2.0nA. (a) Determinar las caracterı́sticas I(V ) en los dispositivos (1) y (2) y comparar los resultados obtenidos. Figura 5 3 Solución Ejercicio 1 (a) IE = IS (evBC /VT − 1) − αISN (evBE /VT − 1) IC = IS (evBE /VT − 1) − αISI (evBC /VT − 1) Donde IS = αN .ISE = αI .ISC (b) .IC )+IE0 VE = VT .Ln( −(IE +αIIE0 ) VC = VT .Ln( −(IC +αINC0.IE )+IC0 ) Ejercicio 2 (b) vCE = VT .Ln( IB (βI +1) I + βC βI I I IB − βC N ) Figura 6 (c) vCESAT = VT .Ln( (βIβ+1) + I (d) Ver figura 7 IC 1 IB β I ) Ejercicio 3 (a) Figura (a): i = αISN (ev/VT − 1) Figura (b): i = αISI (ev/ VT − 1) 4 Figura 7 Va −Vb AC VT (b) AE = e Donde Va es la tensión base emisor de la figura (a), Vb es la tensión base colector de la figura (b), AC y AE son los tamaños de las junturas colector-base y emisorbase respectivamente. Ejercicio 4 S (ev/VT − 1) (a) iE = βIN i = iB = IS ( β1N + β1I )(ev/VT − 1) Notar que en el dibujo iE se define saliente (no entrante como en la convención de signos dada en la figura 1) (b) iE i I = ( βNβ+β ) I Ejercicio 5 (a) Figura (1) i = −(1 − αN .αI )ISE (ev/VT − 1) Figura (2) i = −ISE (e−v/VT − 1) 5