capítulo 3: justificación y desarrollo

Anuncio

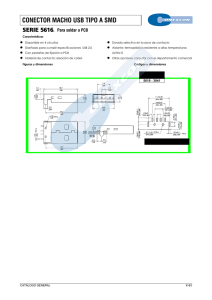

CAPÍTULO 3: JUSTIFICACIÓN Y DESARROLLO Introducción CAPÍTULO 3: JUSTIFICACIÓN Y DESARROLLO Introducción El propósito de este proyecto es principalmente, como ya se ha comentado, el desarrollo de un entorno hardware que permita la realización de test de un circuito integrado sometido a radiación en un acelerador de partículas. Para ello se ha diseñado a conciencia el circuito integrado para que sea más vulnerable a la radiación. El cual consiste funcionalmente en una estructura XOR que es como un detector de paridad que avisa donde se produce un error. La lista de pines del encapsulado del circuito integrado que se va a radiar corresponde con la Figura 3. FIG. 9 .- Pines del Circuito Integrado Su layout visto por un microscopio electrónico tiene el siguiente aspecto. Dto. Ingeniería Electrónica - 20 - Universidad de Sevilla CAPÍTULO 3: JUSTIFICACIÓN Y DESARROLLO Introducción El circuito integrado deberá tener abierto en su encapsulado de tal forma que quede al descubierto el dado. Deberá quedar cerrado y abrirlo en el momento del experimento posible para suciedad evitar en la superficie de dicho dado. FIG. 10 .- Fotografia del Chip Debemos intentar que la radiación sólo afecte a esa zona donde realmente está el circuito con tecnología CMOS y donde se pueden producir SEE. Durante el experimento se irán aplicando una serie de entradas, elegidas a propósito, que producirán distintas salidas para cada una de ellas. Todo el control del experimento, desde el inicio al final, deberá llevarse a cabo a través de alguna máquina de estados que hemos decidido implementar en una FPGA, en concreto, una Spartan II. El principal motivo por el que elegimos esta FPGA es porque aprovecharemos una plataforma que ya existe que nos permitirá comunicar los datos que recibamos en nuestra PCB con un ordenador mediante un cable de datos USB[3]. Y además contiene una FPGA Spartan II, en la cual introduciremos la máquina de estados necesaria para gobernar todo el proceso del test. En la figura 11 podemos ver un esquema de la PCB que se debe diseñar, con el chip que radiaremos y a su vez necesitará una interfaz USB para comunicarse con el exterior, con la sala de control. Dto. Ingeniería Electrónica - 21 - Universidad de Sevilla CAPÍTULO 3: JUSTIFICACIÓN Y DESARROLLO Introducción FIG. 11 .- Uso de la interfaz USB En la conexión de la plataforma USB con la PCB que nosotros hagamos la tendremos que conectar mediante un conector de 40 pines, tal y como aparece en la siguiente figura. FIG. 12 .- Conector Hembra IDC40M Existen una serie de puertos bidireccionales de entrada y salida que se pueden usar a nuestro antojo, y otras señales relativas a alimentación, señal de reloj, etc... La asignación que hemos realizado de pines es la que aparece en la figura que viene a continuación. Pin Señal Pin Señal 1 2 3 4 5 6 7 8 9 GND VDD5 VDD33D IOCHANGED SM_WR PORTB0 SM_D1 PORTB1 SM_D2 21 22 23 24 25 26 27 28 29 PORTA0 PORTB7 PORTA1 PORTC0 PORTA2 SM_DBG PORTA3 SM_RST PORTA4 Dto. Ingeniería Electrónica - 22 - Universidad de Sevilla CAPÍTULO 3: JUSTIFICACIÓN Y DESARROLLO Introducción 10 PORTB2 30 SM_RSM 11 SM_D3 31 PORTA5 12 PORTB3 32 SM_SNP 13 SM_D4 33 PORTA6 14 PORTB4 34 SM_BUSY 15 SM_D5 35 PORTA7 16 PORTB5 36 SM_PROG 17 SM_D6 37 SM_DONE 18 PORTB6 38 SM_INIT 19 SM_D7 39 SM_CCLK 20 SM_CS 40 SM_D0 FIG. 13 .- Pines del puerto de comunicaciones [3] Estamos ya en condiciones de comunicar el chip con la FPGA simplemente rutando adecuadamente la FPGA con líneas de datos desde el conector de 40 pines al chip. La siguiente tabla muestra con que pines de la interfaz usb hemos conectado el chip. Serán estas las configuraciones de pines a tener en cuenta cuando se vaya a realizar el volcado de la máquina de estados en la FPGA. Ya que así ésta conocerá la disposición de cada señal que llega o viene del chip y ver en qué pines deberá introducir las entradas al circuito, así como interpretar sus salidas. Pin Señal Señal Chip Pin Señal Señal Chip 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 GND VDD5 VDD33D IOCHANGED SM_WR PORTB0 SM_D1 PORTB1 SM_D2 PORTB2 SM_D3 PORTB3 SM_D4 PORTB4 SM_D5 PORTB5 SM_D6 PORTB6 SM_D7 SM_CS GND Vdd5 Vdd33 SETDET1B ALARMA* SPOUT1B SR0B CTRL_FPGA* SPOUT2C SPOUT1C SR0C ENA1 CLKSP1 - 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 PORTA0 PORTB7 PORTA1 PORTC0 PORTA2 SM_DBG PORTA3 SM_RST PORTA4 SM_RSM PORTA5 SM_SNP PORTA6 SM_BUSY SM_PORTA7 SM_PROG SM_DONE SM_INIT SM_CCLK SM_D0 SPOUT2B SR0A CLK* SPOUT1A SETDET1A SPOUT2A SRINP CLKSR LED1* LED2* LED3* - *Señales que no son del chip. Todas ellas las veremos en los siguientes capítulos. FIG. 14 .- Conexión entre el conector de datos y el chip Dto. Ingeniería Electrónica - 23 - Universidad de Sevilla CAPÍTULO 3: JUSTIFICACIÓN Y DESARROLLO Detección de SELs Detección de SELs Una vez resuelto como comunicaremos con el exterior el PCB, deberemos ver como podemos solucionar un problema que comentamos antes. Es la posible presencia de SELs. Explicaremos que es un SEL de una forma más detallada. Es un efecto que se produce principalmente en tecnologías CMOS. Se debe principalmente a la activación de un tiristor que hay parásito en este tipo de tecnologías. Si realizamos un corte transversal sobre un circuito CMOS podemos tener la siguiente figura. Como se observa tenemos la estructura típica de un tiristor. El efecto de esta estructura podríamos parásita hacer que tuviera poca incidencia sobre nuestro integrado si lo tenemos en cuenta en la fase de diseño de nuestro Layout. Es fácil ver que consiguiendo que las resistencias Rs sea muy alta y Rw muy pequeña, FIG. 15 .- Estructura de Latchup: a.- Corte Transversal. b.Tiristor que se forma. (Extraída de [4] ) podríamos disminuir la posibilidad de que se active esta estructura parásita. Hemos comentado como hacer que no aparezca este efecto pero no hemos dicho que provoca. Si un protón o ión pesado impactaran sobre el circuito integrado podría provocar una corriente por ejemplo en el transistor parásito pnp, de forma que se amplificaría en el transistor npn de forma que la corriente empezaría a aumentar, viendo la característica del tiristor, representada a continuación, que como se trata de una función Dto. Ingeniería Electrónica Universidad de Sevilla - 24 - CAPÍTULO 3: JUSTIFICACIÓN Y DESARROLLO Detección de SELs multievaluada podría producirse un aumento de corriente considerable, es decir, un camino de baja impedancia desde la fuente de alimentación a tierra. Con lo cual podríamos llegar a quemar el circuito integrado con todos sus componentes. Existe un umbral de tensión para el cual la función empieza a ser multievaluada y donde se pueden producir estos efectos dañinos, al que llamaremos Vh . Se ha separado en regiones las diferentes zonas de funcionamiento, y como se ve en la región III tenemos la posibilidad de tener una corriente muy alta provocando un daño considerable en nuestro integrado. Este efecto debemos tenerlo en cuenta en el diseño de nuestro FIG. 16 .- Característica V/I del Latchup (Extraída de [4]) entorno hardware porque podría producirse un SEL en cualquier instante donde el circuito bajo pruebas esté bajo radiación. Entonces nos convendría poder detectar cuando se ha producido un SEL y antes de que empiece a conducir una gran corriente o en cuanto se pueda detectarlo y cerrar el suministro de corriente al circuito integrado. Una vez pasado un tiempo prudencial volvemos a alimentar el chip. Hay que tener en cuenta que se trata de SEE, donde una partícula impacta sobre la red cristalina de silicio, y por tanto es un efecto transitorio. También realizaremos una estadística del número de SEL que se han producido durante la experiencia y además el instante en el que se produjo. Existen diversas técnicas de fabricación de layout para evitar este efecto, o disminuir la probabilidad que se produzca, pero dado que nos interesa estudiar el fenómeno, no usaremos ninguna.[13] Dto. Ingeniería Electrónica - 25 - Universidad de Sevilla CAPÍTULO 3: JUSTIFICACIÓN Y DESARROLLO Detección de SELs El problema que se nos presenta es claro. Necesitamos diseñar un detector de corriente lo más rápido posible y que consiga avisar a nuestra máquina de estados que gobierna el proceso. El diseño que se ha realizado consta de un comparador que estará comprobando si la tensión que se le suministra al integrado disminuye hasta cierto umbral ( Vdth ) a partir del cual se considera que ha ocurrido un SEL. FIG. 17 .- Detección y Control de Latchup La tensión Vdd representada en la figura es la que suministramos al Chip. Se ha colocado una llave que controlaremos desde la máquina de estados de la FPGA. Esta llave estará cortada para no dejar pasar la alimentación al chip cuando se detecte un SEL, es decir, una baja impedancia en el nudo de alimentación del chip. En la comparación deberemos tener una tensión lo más estable posible para poder realizar con cierta precisión la comparación. Para tal fin, usaremos un regulador de tensión ajustable, y así cambiando el valor de unas resistencias que colocaremos en serie podemos cambiar el valor de referencia de esta tensión. El valor variará en función del consumo del circuito integrado y de la resistencia que hemos colocado a la salida de la llave. Dto. Ingeniería Electrónica - 26 - Universidad de Sevilla CAPÍTULO 3: JUSTIFICACIÓN Y DESARROLLO Detección de SELs Resumiendo, mantendremos abierta la llave, dejando pasar corriente mientras no se produzcan SEL, en el momento que el comparador determine que le está llegando al circuito integrado más corriente de la que debiera, la FPGA mandaría cortar la llave y por consiguiente también el paso de corriente al integrado. Como se trata de procesos muy rápidos, nos interesa elegir unos componentes: llave y comparador muy rápidos. También convendría que la resistencia en on de la llave fuera lo más pequeña posible, y así la caída de tensión sería lo mejor posible al paso de la corriente por la llave. El comparador y la llave son de MAXIM y sus hojas de características (datasheets) se han adjuntado anexos en el apartado Hojas de Características. El comparador es el MAX9010 y la llave es el integrado MAX4741. Entre algunas de las características más destacadas del comparador está su retraso de 5ns , una alimentación de 5V y una salida de 3.3 V, que hará que sea compatible con la lógica de la FPGA. Por otro lado, de la llave elegida podemos decir que posee una resistencia en on bastante pequeña de 0.8Ω y la conmutación más lenta es de 18ns como valor típico. En el apartado de cálculos y planos queda más detallado como hemos realizado la elección de resistencias y que corriente consideraremos como máxima que podrá llegarle al circuito integrado. [Cálculos]. Aquí podremos comprobar como el circuito responde de forma satisfactoria a nuestros requisitos. Dto. Ingeniería Electrónica - 27 - Universidad de Sevilla CAPÍTULO 3: JUSTIFICACIÓN Y DESARROLLO Definición de la PCB Definición de la PCB Hasta este punto hemos realizado una solución funcional de nuestra plataforma hardware. A partir de ahora, trataremos como se ha abordado la implementación física de nuestro entorno hardware. El esquemático de nuestra tarjeta PCB podemos verlo en los Planos 1 y 2, y su layout en el Plano 3. Los esquemáticos se han dividido en dos planos funcionales, el de alimentación (o detección de latchup) y el de datos. El entorno de radiación en el que estará nuestra tarjeta PCB hace que tenga que haya que tener previsto una serie de factores diferentes a un entorno normal. Las diferentes consideraciones son las siguientes: -Dimensiones y distribución de componentes. -Copper. -Pistas de metal y componentes. -Alimentación. -Reloj. -Diodos. Dimensiones y distribución de componentes El experimento requiere que la tarjeta PCB que introduciremos en el ciclotrón debe poseer unas dimensiones para que pueda ser insertada y permanezca inmóvil y en su adecuada posición. Son necesarias unas dimensiones de 17.6 cm x 12 cm para que no se produzcan problemas. También debemos colocar el chip que será radiado en la parte inferior, lo más pegado al borde de la tarjeta PCB. Dicho chip tendrá accesible la zona del dado para su radiación. Sin embargo, es aconsejable para evitar radiación en otras del encapsulado, colocar un apantallamiento que cubra al encapsulado y dejar sólo abierto un rectángulo del tamaño del dado, de esta forma conseguimos disminuir la afluencia de protones que llega a otros componentes electrónicos de la PCB y conseguir que sea prácticamente el circuito integrado el destinatario de casi toda la radiación. Dto. Ingeniería Electrónica Universidad de Sevilla - 28 - CAPÍTULO 3: JUSTIFICACIÓN Y DESARROLLO Definición de la PCB La placa que usaremos será de 2 capas. Por ello, convendría colocar en una capa de forma aislada nuestro chip. Y por detrás, en la otra capa, el resto de componentes que sean necesarios, de forma que el chip quede en el lado donde se administra la radiación. Copper Consiste dejar metal cuando realizamos el etching (eliminado de metal) en la tarjeta PCB, en zonas donde no hay componentes ni pistas. Gracias a esta técnica podremos realizar una capa de apantallamiento para evitar así todo lo posible que la radiación acabe afectando a los componentes que controlan al experimento. Pistas de metal y componentes La experiencia de radiación será llevada a cabo aplicando el vacío sobre la zona donde colocaremos la circuitería . Esto implica que debemos tener especial cuidado con cualquier tipo de disipación de calor por efecto Joule, ya que un aumento de temperatura provocaría un aumento de corriente, debido a que no se puede disipar calor. Por ello todos los componentes han sido elegidos a partir de esta consideración. De hecho se han realizado unas pruebas de vacío que dieron un resultado satisfactorio. Además las pistas de metal de nuestro circuito se han hecho de un 1 mm de ancho, menos las conexiones de los componentes más pequeños, como el comparador y la llave. Este ancho se justifica también por el ambiente que tendrá el experimento. Realizando más anchas las pistas hacemos que el impacto de posibles protones que le lleguen a estas no supongan una cierta inyección de carga suficiente para que pueda causar algún tipo de daño. Se podría pensar que con ello aumentaríamos las pérdidas por efecto Joule, pero son tan pequeñas que no afectaría de forma considerable a nuestro sistema. Dto. Ingeniería Electrónica - 29 - Universidad de Sevilla CAPÍTULO 3: JUSTIFICACIÓN Y DESARROLLO Definición de la PCB Alimentación Usaremos como fuente de alimentación una batería de 8.5V . En nuestro sistema necesitaremos varias tensiones de alimentación. Para cada tensión que necesitemos la crearemos y estabilizaremos con reguladores. Las tensiones necesarias serán de 3.3 V y 5 V que alimentarán los chips y la FPGA. Además obligatoriamente tendremos que fijar una tensión de referencia para realizar la comparación en el detector de SELs, que conseguiremos gracias a un regulador ajustable.[Cálculos] Se ha elegido una batería que consiga aguantar durante todo el tiempo del experimento. De todas formas, la circuitería utilizada no tiene un alto consumo, por tanto no ha preocupado mucho esta cuestión en el diseño de la experiencia. Reloj Trabajaremos con una frecuencia de reloj de 50 Mhz. Para ello situaremos el reloj en el puerto PORTA2 del conector de datos. En realidad, si se mira detenidamente el esquemático. El puerto PORTA2 no es un puerto diseñado para recibir la señal de reloj en la plataforma USB, sin embargo realizando un pequeño cortocircuito con el pin adyacente de la FPGA GCK2, conseguimos introducir la señal del reloj, ya que este puerto si es para recibir un reloj externo. FIG. 18 .- Solución al reloj (Cortocircuito señalado con línea roja) Dto. Ingeniería Electrónica - 30 - Universidad de Sevilla CAPÍTULO 3: JUSTIFICACIÓN Y DESARROLLO Definición de la PCB Como disponíamos de espacio sobrante en la placa, hemos situado el reloj lo más cercano a su punto de conexión evitando así posibles reflexiones o cualquier otro tipo de problemas relacionado con el largo de la pista que lo comunica. Diodos Hemos introducido una serie de diodos con el único de propósito de poder comprobar el funcionamiento de cualquier parte de nuestro circuito en todo momento. Como ya es conocido los diodos suelen tener cierta corriente máxima que puede circular por ellos, por tanto tendremos que colocar unas resistencias limitadoras. Donde Vcc es la tensión de nivel alto que le llegará del pin de la FPGA. I F es la corriente máxima que deberá circular por el LED. Y V L será la tensión de caída directa del LED. Por consiguiente, queremos conseguir lo siguiente:[3] R≥ Vcc − VL 3.3V − 2V = = 65Ω IF 20mA Eligiendo un valor mayor que sesenta y cinco no FIG. 19 .- Diodo y resistencia limitadora de corriente tendríamos el problema de llegar a quemar el diodo. En nuestro caso hemos elegido R = 330Ω . El resultado final se puede ver en las figuras que vienen a continuación. Dto. Ingeniería Electrónica - 31 - Universidad de Sevilla CAPÍTULO 3: JUSTIFICACIÓN Y DESARROLLO Definición de la PCB FIG. 20 .- Fotografía de la PCB diseñada En la fotografía podemos distinguir claramente el circuito encargado de la detección de latchup, situado en la parte inferior. En la parte media conectaremos la plataforma USB. Y el chip iría por la otra cara. Dto. Ingeniería Electrónica - 32 - Universidad de Sevilla CAPÍTULO 3: JUSTIFICACIÓN Y DESARROLLO Definición de la PCB FIG. 21 .- Fotografía de la PCB diseñada Es destacable ver el apantallamiento gracias al copper que hemos dejado en la PCB y la abertura que tiene el chip para que pueda ser radiado su dado. Dto. Ingeniería Electrónica - 33 - Universidad de Sevilla