Registros de Tres Estados con la GAL22V10

Anuncio

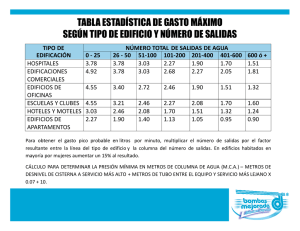

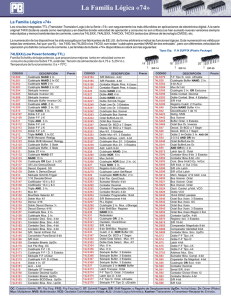

Registros de Tres Estados con la GAL22V10 Se presentan dos proyectos realizados con ABEL-HDL mediante el software de desarrollo isp LEVER starter de Lattice, ambos relacionados con salidas que pueden tomar tres estados: alto (1), bajo (0) y el tercer estado (alta impedancia). Al igual que las compuertas lógicas, se pueden empaquetar varios registros de tres estados independientes. Por ejemplo, la figura 1 muestra los diagramas de las terminales del 74LS125 y del 74LS126, cada uno de los cuales contiene cuatro registros de tres estados no inversores independientes en paquetes DIP de 14 pines. Nuestro primer proyecto consiste en emular al primero de ellos. Figura 1 Búferes cuádruples de tres estados. Para crear el buffer cuádruple de tres estados se empleó la herramienta esquemática, según ilustra la figura 2. La habilitación para cada buffer es en nivel bajo, como se observa. Figura 2 Captura esquemática para el primer proyecto. La figura 3 exhibe el reporte del grabador de fusibles con fórmulas y asignación de pines. Y4 Y4.OE = ( = ( A4 ); !C4 ); Y3 Y3.OE = ( = ( A3 ); !C3 ); Y2 Y2.OE = ( = ( A2 ); !C2 ); Y1 Y1.OE = ( = ( A1 ); !C1 ); Page 3 ispLEVER 5.0.00.47.19.05_Starter - Device Utilization Chart Sun Oct 21 20:50:04 2007 ls125.bls P22V10G Chip Diagram: P22V10G C4 C3 C2 C1 A4 A3 A2 A1 GND +---------\ /---------+ | \ / | | ----| | 1 24 | | | | 2 23 | | 3 22 | | 4 21 | | 5 20 | | | | 6 19 | | | | 7 18 | | | | 8 17 | | 9 16 | | 10 15 | | | | 11 14 | | 12 13 | | | `---------------------------' Vcc Y1 Y3 Y4 Y2 Figura 3 Reporte del mapa de fusibles con asignación de patitas. La siguiente figura muestra los vectores de simulación propuestos. MODULE VECTAS X,Z = .x.,.z.; " no importa y alta impedancia de salida " entradas C1,A1,C2,A2,C3,A3,C4,A4 PIN; "SALIDAS Y1,Y2,Y3,Y4 PIN ISTYPE 'COM'; TEST_VECTORS ([C1,A1,C2,A2,C3,A3,C4,A4]->[Y1,Y2,Y3,Y4]) [1,1, 1,0, 0,1, 0,0] ->[Z, X, X, 0]; [0,1, 0,1, 0,1, 1,0] ->[1, 1, X, Z]; [1,0, 1,0, 1,0, 0,1] ->[X, Z, X, 1]; [0,1, 0,0, 1,X, 1,0] ->[X, 0, X, Z]; END Figura 4 Archivo VECTAS.ABV que define cuatro vectores de prueba. Z = alta impedancia. La figura 5 brinda el resultado de la simulación del JEDEC grabado. Figura 5 Simulación de los cuatro vectores de prueba. El achurado implica alta impedancia. El segundo proyecto es emular el comportamiento del dispositivo octal 74LS541 de tres estados no inversor, ver figura 6. Octal significa que la parte contiene ocho buffers individuales. Este MSI tiene sus ocho entradas en un lado del integrado y sus ocho salidas en el otro lado. Ambas entradas de habilitación /E1 y /E2 deben activarse para habilitar las salidas del dispositivo de tres estados. Los símbolos rectangulares pequeños dentro de los símbolos del los búferes indican histéresis. Las entradas del 74LS541 tienen 0.4V de histéresis típicamente. Figura 6 Encapsulado de 20 pines del buffer octal 74LS541 de tres estados. A diferencia del proyecto previo, ahora no se usó la captura esquemática sino que se definió la relación de entrada-salida mediante un módulo de texto que se ofrece en la figura 7. MODULE tresEdosBuff TITLE 'Buffer octal de 3 estados con dos permisos' X,Z = .x.,.z.; " entradas E1,E2,D8..D1 pin 1,2,4..11; D = [D8..D1]; E = !(E1#E2); " Salidas Y8..Y1 pin 23..20, 18..15 istype 'com'; Y = [Y8..Y1]; equations Y = D; Y8.oe = Y7.oe = Y6.oe = Y5.oe = E; E; E; E; "!(E1#E2); "!(E1#E2); Y4.oe = !(E1#E2); Y3.oe = !(E1#E2); Y2.oe = !(E1#E2); Y1.oe = !(E1#E2); test_vectors ([E1,E2,D] -> Y) [X, 1, X] -> Z; [1, X, X] -> X; [0, 0,23] -> 23; [0, 0,45] -> X; [0, 1, X] -> Z; [1, 0, X] -> Z; [0, 0,93] -> X; [0, 0,159] -> 159; END Figura 7 Archivo LS541.ABL para definir la ecuación de salida, el control del tercer estado y ocho vectores de prueba. La figura 8 nos indica el formulado y la distribución de patitas de la GAL. Y8 Y8.OE Y7 Y7.OE = = = = ( ( ( ( D8 ); !E1 & !E2 ); D7 ); !E1 & !E2 ); Y6 Y6.OE = ( = ( D6 ); !E1 & !E2 ); Y5 Y5.OE Y4 Y4.OE = = = = ( ( ( ( D5 ); !E1 & !E2 ); D4 ); !E1 & !E2 ); Y3 Y3.OE = ( = ( D3 ); !E1 & !E2 ); Y2 Y2.OE = ( = ( D2 ); !E1 & !E2 ); Y1 Y1.OE = ( = ( D1 ); !E1 & !E2 ); ispLEVER 5.0.00.47.19.05_Starter 21 20:21:37 2007 - Device Utilization Chart Page 3 Sun Oct Buffer octal de 3 estados con dos permisos P22V10G Chip Diagram: ---------------------------------------------------------------------------P22V10G E1 E2 D8 D7 D6 D5 D4 D3 D2 D1 GND +---------\ /---------+ | \ / | | ----| | 1 24 | | | | 2 23 | | 3 22 | | 4 21 | | | | 5 20 | | 6 19 | | 7 18 | | | | 8 17 | | 9 16 | | | | 10 15 | | 11 14 | | | | 12 13 | | | | | `---------------------------' Vcc Y8 Y7 Y6 Y5 Y4 Y3 Y2 Y1 Figura 8 chip report para el segundo proyecto, mostrando relaciones y asignación de pines. La figura 9 ilustra la respuesta en tiempo de los ocho vectores de prueba. Figura 9 Comportamiento del mapa de fusibles grabado. Achurado = Tercer estado. El diseño realizado permite la conformación de buses o ductos. Un bus es compartido por varios dispositivos y para evitar que éstos se dañen, cuando algunos de ellos no deben poner sus señales en el bus se les pone en el tercer estado, de tal modo que sólo uno de ellos puede tener sus salidas activas. Memorias y puertos son dispositivos que se usan en el diseño de microcomputadoras y tienen la característica de que sus salidas se van al tercer estado cuando no son seleccionadas.