Algebra Booleana.

Anuncio

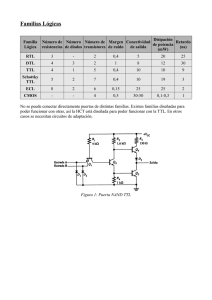

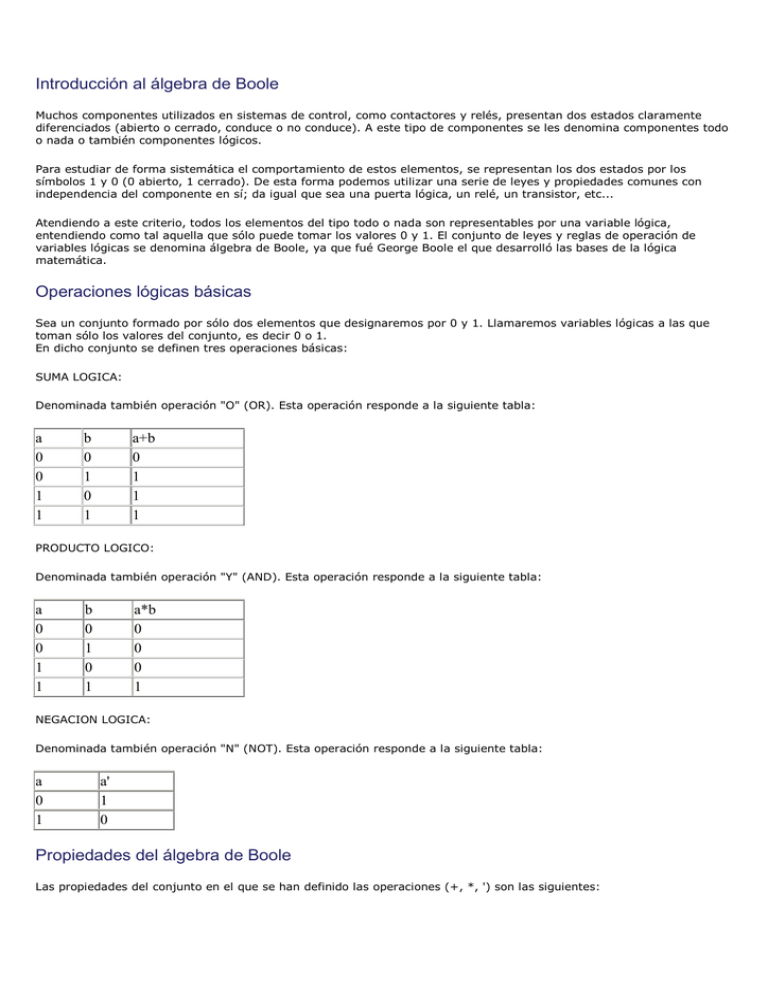

Introducción al álgebra de Boole Muchos componentes utilizados en sistemas de control, como contactores y relés, presentan dos estados claramente diferenciados (abierto o cerrado, conduce o no conduce). A este tipo de componentes se les denomina componentes todo o nada o también componentes lógicos. Para estudiar de forma sistemática el comportamiento de estos elementos, se representan los dos estados por los símbolos 1 y 0 (0 abierto, 1 cerrado). De esta forma podemos utilizar una serie de leyes y propiedades comunes con independencia del componente en sí; da igual que sea una puerta lógica, un relé, un transistor, etc... Atendiendo a este criterio, todos los elementos del tipo todo o nada son representables por una variable lógica, entendiendo como tal aquella que sólo puede tomar los valores 0 y 1. El conjunto de leyes y reglas de operación de variables lógicas se denomina álgebra de Boole, ya que fué George Boole el que desarrolló las bases de la lógica matemática. Operaciones lógicas básicas Sea un conjunto formado por sólo dos elementos que designaremos por 0 y 1. Llamaremos variables lógicas a las que toman sólo los valores del conjunto, es decir 0 o 1. En dicho conjunto se definen tres operaciones básicas: SUMA LOGICA: Denominada también operación "O" (OR). Esta operación responde a la siguiente tabla: a 0 0 1 1 b 0 1 0 1 a+b 0 1 1 1 PRODUCTO LOGICO: Denominada también operación "Y" (AND). Esta operación responde a la siguiente tabla: a 0 0 1 1 b 0 1 0 1 a*b 0 0 0 1 NEGACION LOGICA: Denominada también operación "N" (NOT). Esta operación responde a la siguiente tabla: a 0 1 a' 1 0 Propiedades del álgebra de Boole Las propiedades del conjunto en el que se han definido las operaciones (+, *, ') son las siguientes: PROPIEDAD CONMUTATIVA: De la suma: a+b = b+a Del producto: a*b = b*a PROPIEDAD ASOCIATIVA: De la suma: (a+b)+c = a+(b+c) = a+b+c Del producto: (a*b)*c = a*(b*c) = a*b*c LEYES DE IDEMPOTENCIA: De la suma: a+a = a ; a+a' = 1 Del producto: a*a = a ; a*a' = 0 PROPIEDAD DISTRIBUTIVA: De la suma respecto al producto: a*(b+c) = (a*b) + (a*c) Del producto respecto a la suma: a + (b*c) = (a+b) * (a+c) LEYES DE DE MORGAN: (a+b+c)' = a'*b'*c' (a*b*c)' = a'+b'+c' Otras operaciones lógicas A partir de las operaciones lógicas básicas se pueden realizar otras operaciones booleanas, las cuales son: NAND, cuya tabla correspondiente es: a 0 0 1 1 b 0 1 0 1 (a*b)' 1 1 1 0 NOR, cuya tabla correspondiente es: a 0 0 1 1 b 0 1 0 1 (a+b)' 1 0 0 0 XOR, también llamada función OR-EXCLUSIVA. Responde a la tabla: a 0 0 1 1 b 0 1 0 1 a(+)b 0 1 1 0 Puertas lógicas Todas las funciones lógicas vistas hasta el momento poseen una representación normalizada, la cual se muestra en la figura siguiente: Toda puerta lógica consta de 1 o más entradas y 1 o 2 salidas (puede darse el caso de proporcionarse la salida y su negada). En todos los símbolos las entradas se encuentran a la izquierda y las salidas a la derecha. Estas puertas las podemos encontrar empaquetadas dentro de distintos circuitos integrados. Por ejemplo, para la familia lógica TTL tenemos las siguientes referencias: 54/74 (LS) 00 Cuádruple puerta NAND de dos entradas 54/74 (LS) 02 Cuádruple puerta NOR de dos entradas 54/74 (LS) 04 Séxtuple puerta NOT 54/74 (LS) 08 Cuádruple puerta AND de dos entradas 54/74 (LS) 10 Triple puerta NAND de tres entradas 54/74 (LS) 11 Triple puerta AND de tres entradas 54/74 (LS) 20 Doble puerta NAND de cuatro entradas 54/74 (LS) 21 Doble puerta AND de cuatro entradas 54/74 (LS) 27 Triple puerta NOR de tres entradas 54/74 (LS) 30 Puerta NAND de ocho entradas 54/74 (LS) 32 Cuádruple puerta OR de dos entradas Las puertas lógicas más frecuentes, baratas, y fáciles de encontrar son las NAND. Debido a esto se suelen implementar circuitos digitales con el mayor número de dichas puertas. Hay que mencionar en este punto que los niveles de tensión que se corresponden con los niveles lógicos 1 y 0 dependen de la familia lógica empleada. De momento basta saber que la familia TTL se alimenta con +5V, por lo que los niveles de tensión se corresponderán con +5V para el 1 lógico y 0V para el 0 lógico (idealmente hablando, claro). Funciones lógicas La aplicación más directa de las puertas lógicas es la combinación entre dos o más de ellas para formar circuitos lógicos que responden a funciones lógicas. Una función lógica hace que una o más salidas tengan un determinado valor para un valor determinado de las entradas. Supongamos que tenemos dos entradas, A y B, y una salida F. Vamos a hacer que la salida sea 1 lógico cuando A y B tengan el mismo valor, siendo 0 la salida si A y B son diferentes. En primer lugar veamos los valores de A y B que hacen 1 la función: A=1yB=1 A=0yB=0 Es decir, podemos suponer dos funciones de respuesta para cada caso: F1 = A*B (A y B a 1 hacen F1 1) F2 = A'*B' (A y B a 0 hacen F2 1) La suma de estas funciones será la función lógica final que buscamos: F = F1 + F2 = (A*B)+(A'*B') A continuación vamos a ver como en muchos casos es posible simplificar la función lógica final en otra más simple sin alterar el funcionamiento del circuito. Simplificación de funciones Supongamos que tenemos un circuito donde "F" es la respuesta (salida) del mismo en función de las señales A, B, y C (entradas): F = A*B*C + A'*B*C + B*C Esta función puede ser simplificable aplicando las propiedades del álgebra de Boole. En primer lugar aplicamos la propiedad distributiva: F = B*C*(A+A') + B*C Ahora aplicamos las leyes de idempotencia: F = B*C + B*C = B*C Como hemos podido ver en este ejemplo en muchas ocasiones se puede simplificar la función (y por tanto el circuito) sin que ello afecte al resultado. Más adelante veremos como simplificar funciones empleando otros métodos más sencillos y fiables. Tabla de verdad DEFINICION: Es una forma de representación de una función en la que se indica el valor 0 o 1 para cada valor que toma ésta por cada una de las posibles combinaciones que las variables de entrada pueden tomar. Anteriormente hemos visto las tablas de respuesta de cada una de las operaciones lógicas; estas tablas son tablas de verdad de sus correspondientes puertas lógicas. La tabla de verdad es la herramienta que debemos emplear para obtener la forma canónica de la función del circuito, para así poder simplificar y conseguir la función más óptima. Familias lógicas Los circuitos digitales emplean componentes encapsulados, los cuales pueden albergar puertas lógicas o circuitos lógicos más complejos. Estos componentes están estandarizados, para que haya una compatibilidad entre fabricantes, de forma que las características más importantes sean comunes. De forma global los componentes lógicos se engloban dentro de una de las dos familias siguientes: TTL: diseñada para una alta velocidad. CMOS: diseñada para un bajo consumo. Actualmente dentro de estas dos familias se han creado otras, que intentan conseguir lo mejor de ambas: un bajo consumo y una alta velocidad. No se hace referencia a la familia lógica ECL, la cual se encuentra a caballo entre la TTL y la CMOS. Esta familia nació como un intento de conseguir la rapidez de TTL y el bajo consumo de CMOS, pero en raras ocasiones se emplea. Comparación de las familias PARAMETRO TTL estándar TTL 74L Fairchild 4000B TTL Schottky de CMOS (con baja potencia (LS) Vcc=5V) Fairchild 4000B CMOS (con Vcc=10V) Tiempo de propagación de puerta 10 ns 33 ns 5 ns 40 ns 20 ns Frecuencia máxima de funcionamiento 35 MHz 3 MHz 45 MHz 8 MHz 16 MHz Potencia disipada por puerta 10 mW 1 mW 2 mW 10 nW 10 nW Margen de ruido admisible 1V 1V 0'8 V 2V 4V Fan out 10 10 20 50 (*) 50 (*) (*) O lo que permita el tiempo de propagación admisible Dentro de la familia TTL encontramos las siguiente sub-familias: • • • • L: Low power = dsipación de potencia muy baja LS: Low power Schottky = disipación y tiempo de propagación pequeño. S: Schottky = disipación normal y tiempo de propagación pequeño. AS: Advanced Schottky = disipación normal y tiempo de propagación extremadamente pequeño. TENSION DE ALIMENTACION CMOS: 5 a 15 V (dependiendo de la tensión tendremos un tiempo de propagación). TTL: 5 V. Parámetros de puerta Las puertas lógicas no son dispositivos ideales, por lo que vamos a tener una serie de limitaciones impuestas por el propio diseño interno de los dispositivos lógicos. Internamente la familia TTL emplea transistores bipolares (de aquí su alto consumo), mientras que la familia CMOS emplea transistores MOS (a lo que debe su bajo consumo). MARGEN DEL CERO Es el rango de tensiones de entrada en que se considera un cero lógico: VIL máx: tensión máxima que se admite como cero lógico. VIL mín: tensión mínima que se admite como cero lógico. MARGEN DEL UNO Es el rango de tensiones de entrada en que se considera un uno lógico: VIH máx: tensión máxima que se admite como uno lógico. VIH mín: tensión mínima que se admite como uno lógico. MARGEN DE TRANSICION Se corresponde con el rango de tensiones en que la entrada es indeterminada y puede ser tomada como un uno o un cero. Esta zona no debe ser empleada nunca, ya que la puerta se comporta de forma incorrecta. MT = VIH mín - VIL máx AMPLITUD LOGICA Debido a que dos puertas de la misma familia no suelen tener las mismas características debemos emplear los valores extremos que tengamos, utilizando el valor de VIL máx más bajo y el valor de VIH mín más alto. AL máx: VH máx - VL mín AL mín: VH mín - VL máx RUIDO El ruido es el elemento más común que puede hacer que nuestro circuito no funcione habiendo sido diseñado perfectamente. El ruido puede ser inherente al propio circuito (como consecuencia de proximidad entre pistas o capacidades internas) o también como consecuencia de ruido exterior (el propio de un ambiente industrial). Si trabajamos muy cerca de los límites impuestos por VIH y VIL puede que el ruido impida el correcto funcionamiento del circuito. Por ello debemos trabajar teniendo en cuenta un margen de ruido: VMH (margen de ruido a nivel alto) = VOH mín - VIH mín VML (margen de ruido a nivel bajo) = VIL máx - VOL máx VOH y VOL son los niveles de tensión del uno y el cero respectivamente para la salida de la puerta lógica. Supongamos que trabajamos a un nivel bajo de VOL = 0'4 V con VIL máx = 0'8 V. En estas condiciones tendremos un margen de ruido para nivel bajo de: VML = 0'8 - 0'4 = 0'4 V FAN OUT Es el máximo número de puertas que podemos excitar sin salirnos de los márgenes garantizados por el fabricante. Nos asegura que en la entrada de las puertas excitadas: VOH es mayor que VOH mín VOL es menor que VOL mín Para el caso en que el FAN OUT sea diferente a nivel bajo y a nivel alto, escogeremos el FAN OUT más bajo para nuestros diseños. Si además nos encontramos con que el fabricante no nos proporciona el FAN OUT podemos calcularlo como: FAN OUT = IOL máx / IIL máx Donde IOL e IIL son las corrientes de salida y entrada mínimas de puerta. POTENCIA DISIPADA Es la media de potencia disipada a nivel alto y bajo. Se traduce en la potencia media que la puerta va a consumir. TIEMPOS DE PROPAGACION Definimos como tiempo de propagación el tiempo transcurrido desde que la señal de entrada pasa por un determinado valor hasta que la salida reacciona a dicho valor. vamos a tener dos tiempos de propagación: Tphl = tiempo de paso de nivel alto a bajo. Tplh = tiempo de paso de nivel bajo a alto. Como norma se suele emplear el tiempo medio de propagación, que se calcula como: Tpd = (Tphl + Tplh)/2 FRECUENCIA MAXIMA DE FUNCIONAMIENTO Se define como: Fmáx = 1 / (4 * Tpd)