Laboratorio Nº3 Procesamiento de señales con transistores

Anuncio

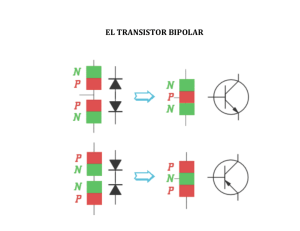

Laboratorio Nº3 Procesamiento de señales con transistores Objetivos Diseñar redes de polarización para operar transistores BJT y JFET en modo activo, y evaluar la estabilidad térmica de puntos de operación, desviación de parámetros de transistores y corrimiento de puntos de operación teóricos. Obtener los parámetros que caracterizan a un amplificador monoetapa: máxima incursión y excursión simétrica, ganancia de voltaje, ganancia de corriente, impedancia de entrada y salida, y respuesta en frecuencia. Diseñar redes de polarización para operar transistores en corte y saturación para la activación de contactores mediante señales lógicas. Actividades • • • • • • • • Diseñar una red de polarización para un amplificador con BJT en configuración Emisor Común (Fig.5) que cumpla con las siguientes especificaciones: Vceq = 6 [V] y Icq = 1 [mA]. Utilice un transistor npn BC-548. Considere una tensión de alimentación Vcc = 12 [V]. Medir y tabular voltajes y corrientes DC en cada componente. Obtener el punto de operación real y calcular β del transistor. Verifique su tensión de alimentación. Utilizando acoplamiento capacitivo de entrada y salida, medir la máxima excursión simétrica y la impedancia de entrada del amplificador. Considere una carga RL = 1 [kΩ] y una señal de entrada sinusoidal con una frecuencia de operación de 1 [kHz]. Medir la ganancia de voltaje y corriente, y el ancho de banda para una señal de entrada sinusoidal con una amplitud igual a la mitad de la máxima incursión simétrica. Retirar el condensador de bypass CE y medir nuevamente la ganancia de voltaje y corriente, y la impedancia de entrada del amplificador (Fig.6). Compare y comente resultados. Definir y montar los circuitos que permitan determinar experimentalmente los parámetros del JFET 2N5458 (corriente saturación IDSS, voltaje pinch-off Vp). Utilice una tensión de alimentación VDD = 15 [V]. Compare sus resultados con la información técnica del transistor proporcionada por el fabricante. Diseñar una red de polarización para un amplificador con JFET canal n en configuración Source Común (Fig.7), que permita obtener una ganancia de voltaje sin distorsión Av = -5 .Considere una carga RL = 1 [kΩ] y una señal de entrada sinusoidal de 100 [mV]/1 [kHz]. Visualice las formas de onda más relevantes. Tabule voltajes y corrientes AC, DC. Diseñar una red de polarización que permita operar un BJT como una compuerta lógica NOT (Fig.8). Considere una tensión de alimentación Vcc = 12 [V] y un tren de pulsos de 5[V]/1[kHz] como señal de control. Tabule los voltajes y corrientes en ambos estados. Mida los tiempos de retardo de encendido y apagado. Comente. ¿Qué se entiende por máxima excursión de señal? ¿Qué elementos definen la respuesta en baja y alta frecuencia de un amplificador monoetapa con BJT y JFET? Marco Teórico Los transistores son dispositivos semiconductores de tres terminales utilizados para el procesamiento y amplificación de señales. Estos se dividen en dos clases que caracterizan la estructura y los principios físicos que controlan las características corriente-voltaje del dispositivo. Las dos clases son el transistor de unión bipolar (BJT) y el transistor de efecto de campo (FET). El BJT se compone de 3 tipos de materiales semiconductores alternados: dos materiales tipo n y uno tipo p (transistor BJT npn), o dos materiales tipo p y uno tipo n (transistor BJT pnp). Sus símbolos respectivos se muestran en Fig.1. Los terminales del BJT se denominan Base (B), Colector (C) y Emisor (E). El transistor BJT opera como un amplificador de corriente controlado por la corriente de base (Ib) con una ganancia β. Las corrientes de colector (Ic) y de emisor (Ie) en un BJT se relacionan con la corriente de base de acuerdo a la siguiente expresión: Ie = Ic + Ib ≈ Ic = β Ib (1) El BJT presenta tres regiones de operación (Fig.2): Región de Corte, Región de Saturación y Región Activa. • Región de Corte: Un transistor esta en corte cuando Ib = 0 → Ic = Ie = 0. En este caso el voltaje entre colector y emisor del transistor (Vce) es igual al voltaje de alimentación. • Región de Saturación: Un transistor esta saturado cuando la corriente de base es lo suficientemente grande para provocar Vce → 0. En este caso la corriente de colector es máxima. Los estados de corte y saturación permiten utilizar el BJT en conmutación en la implementación de operaciones lógicas digitales y circuitos de disparo de semiconductores de potencia (MOSFET, IGBT, IGCT, etc) en aplicaciones de electrónica de potencia, o como interruptor de potencia en fuentes de poder conmutadas de baja potencia. • Región Activa: En esta zona el transistor opera como amplificador de señales alternas, verificándose (1). Para operar el BJT como amplificador lineal, se utilizan distintas técnicas de polarización basadas en redes de elementos pasivos que permiten definir un punto de operación en la zona activa del transistor. La elección del punto de operación permite definir distintos parámetros y características operacionales del amplificador tales como ganancia de voltaje y corriente, impedancia de entrada, ancho de banda o máxima excursión de salida. Por otro lado, dependiendo de la localización de las entradas, salidas y tierra, se definen cuatro configuraciones básicas de amplificadores con BJT: Emisor Común, Emisor Común con resistencia de Emisor, Colector Común (o Seguidor de Emisor), y Base Común. El JFET o FET de Juntura, es uno de los FET más comunes. Permite controlar el flujo de corriente a través de un canal semiconductor, variando la impedancia del canal al aplicar un campo eléctrico perpendicular a la trayectoria de la corriente. Existen 2 tipos de transistores JFET. Uno de ellos esta compuesto por una parte de semiconductor tipo n que constituye el canal, al que se le adicionan 2 regiones con impurezas tipo p unidas entre sí, llamado JFET canal n. El otro es el JFET canal p, donde el canal es de material tipo p y las regiones con impurezas son de tipo n. Sus símbolos respectivos se muestran en Fig.2. Los terminales del JFET se denominan Gate (G), Drain (D) y Source (S). El transistor JFET opera como un amplificador de corriente controlado por el voltaje aplicado entre gate y source (vGS). Utilizando la ecuación de Shockley, la corriente que circula a través del canal del transistor (iD) se define en función de la corriente de saturación drain-source (IDSS) y el voltaje de estrangulamiento del canal o Voltaje de pinch-off (Vp) como: ⎛ v iD ≈ I DSS ⎜1 − GS ⎜ Vp ⎝ ⎞ ⎟⎟ ⎠ (2) C B E C C E E B B a) b) Fig.1 Símbolos transistores BJT: a) pnp, b) npn. IC Saturación IB Región Activa Corte VCE Fig.2 Regiones de operación BJT. EL JFET presenta 3 regiones de operación (Fig.4): Región óhmica, Región de Saturación o Activa y Región de Ruptura. • Región Óhmica: En esta zona el transistor se comporta como una resistencia cuyo valor óhmico esta determinado por el voltaje vGS. A medida que disminuye este voltaje, el ancho de la región óhmica aumenta. El FET opera en esta región cuando se desea una resistencia variable y en aplicaciones de conmutación. • Región de Ruptura: Cuando el voltaje entre drain y source (vDS) crece más allá del estrangulamiento, se llega a un punto donde vDS se vuelve tan grande que ocurre la ruptura de avalancha del transistor, que destruye el dispositivo por el incremento abrupto de la corriente iD. • Región de Saturación o Activa: La región entre el voltaje de estrangulamiento y la ruptura de avalancha se denomina región activa. Esta región es útil para aplicaciones de amplificación lineal de señales. En esta región iD se satura y su valor depende de vGS, de acuerdo a (2). Los mismos circuitos básicos utilizados para la polarización de transistores BJT pueden ser utilizados para la polarización de JFET. Sin embargo, en el diseño de amplificadores con JFET debe asegurarse la operación del transistor en la región de saturación o activa. Dependiendo de la localización de las entradas, salidas y tierra, se definen cuatro configuraciones básicas de amplificadores con JFET análogas a las configuraciones de amplificadores con BJT: Source Común, Source Común con resistencia de Source, Drain Común y Gate Común. D D G G S S G D D p n n n G p S a) b) Fig.3 Símbolos transistores JFET: a) canal p, b) canal n. p S ID Región Óhmica Región de Ruptura Región Activa VGS VDS Fig.4 Regiones de operación JFET. Rc R2 C C + - Vin R1 VCC RL RE CE Fig.5 Amplificador con BJT configuración Emisor Común. R2 Rc C C Vin + R1 RE VCC RL Fig.6 Amplificador con BJT configuración Emisor Común con resistencia de Emisor. RD R2 C C + V - DD Vin R1 RL RS CS Fig.7 Amplificador con JFET configuración Source Común. RC RLED RB + V - CC Vin Fig.8 Puerta lógica NOT con BJT configurado en emisor común. Resumen de Diseño • Polarización BJT: R2 Rc Rc + - R1 RE VCC RB ⇒ VBB + - + V - CC RE Fig.9 Circuito polarización transistor BJT con resistencia de emisor y divisor de tensión de base. En el circuito de polarización mostrado en la figura 9, para brindar un margen de estabilidad al punto de polarización del BJT, se recomienda asumir en el diseño de la red de polarización para amplificadores: RB = R1 // R2 = 0,1β RE (3) Luego, conocida la tensión de alimentación (VCC), y calculado VBB es posible determinar las resistencias del divisor de tensión conectado a la base del transistor de la siguiente forma: VBB = VBE + I C ⋅1,11RE R1 = RB V 1 − BB VCC R2 = (4) VCC RB VBB (5) • Amplificador con BJT en Configuración Emisor Común: Utilizando el modelo equivalente AC del amplificador EC (Fig.5), y considerando el modelo para pequeña señal del BJT (modelo híbrido π), es posible determinar que los parámetros del amplificador están dados por las siguientes expresiones: Av = − g m ( RC // RL ) Ai = Rin = RB // rπ (6) Rin − RB RC Av = RL ⎛ RB + rπ ⎞ ⎜ β ⎟ ( RC + RL ) ⎝ ⎠ (8) rπ = β gm = (7) β ⎛ I Cq ⎞ ⎜ ⎟ ⎜ 26 [ mV ] ⎟ ⎝ ⎠ (9) • Amplificador con JFET en Configuración Source Común: Utilizando el modelo equivalente AC del amplificador SC (Fig.7), y considerando el modelo para pequeña señal del JFET (modelo híbrido π), es posible determinar que la ganancia de voltaje del amplificador corresponde a: Av = − g m ( RD // RL ) gm = −2 I DSS Vp ⎛ VGS ⎜⎜1 − ⎝ Vp (10) ⎞ ⎟⎟ ⎠ (11)