sistemes electronics digitals

Anuncio

SISTEMES ELECTRONICS DIGITALS

ETSE-URV

2 Septiembre 2005

Test: +1pto acertada, -1/3pto fallada

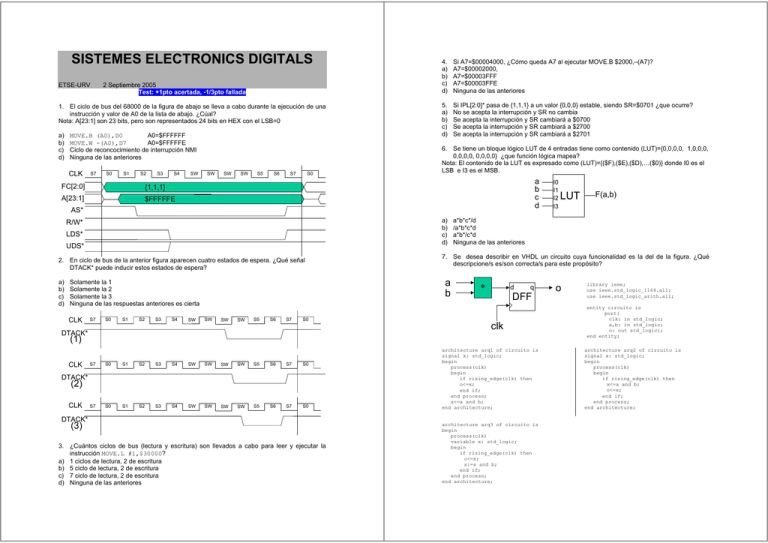

1. El ciclo de bus del 68000 de la figura de abajo se lleva a cabo durante la ejecución de una

instrucción y valor de A0 de la lista de abajo. ¿Cúal?

Nota: A[23:1] son 23 bits, pero son representados 24 bits en HEX con el LSB=0

a)

b)

c)

d)

MOVE.B (A0),D0

A0=$FFFFFF

MOVE.W -(A0),D7

A0=$FFFFFE

Ciclo de reconcocimiento de interrupción NMI

Ninguna de las anteriores

CLK

S7

S0

S1

S2

S3

S4

FC[2:0]

{1,1,1}

A[23:1]

$FFFFFE

SW

SW

SW

SW

S5

S6

S7

S0

4.

a)

b)

c)

d)

Si A7=$00004000, ¿Cómo queda A7 al ejecutar MOVE.B $2000,–(A7)?

A7=$00002000,

A7=$00003FFF

A7=$00003FFE

Ninguna de las anteriores

5.

a)

b)

c)

d)

Si IPL[2:0]* pasa de {1,1,1} a un valor {0,0,0} estable, siendo SR=$0701 ¿que ocurre?

No se acepta la interrupción y SR no cambia

Se acepta la interrupción y SR cambiará a $0700

Se acepta la interrupción y SR cambiará a $2700

Se acepta la interrupción y SR cambiará a $2701

6. Se tiene un bloque lógico LUT de 4 entradas tiene como contenido (LUT)={0,0,0,0, 1,0,0,0,

0,0,0,0, 0,0,0,0} ¿que función lógica mapea?

Nota: El contenido de la LUT es expresado como (LUT)={($F),($E),($D),…($0)} donde I0 es el

LSB e I3 es el MSB.

a

b

c

d

AS*

a)

b)

c)

d)

R/W*

LDS*

UDS*

2. En ciclo de bus de la anterior figura aparecen cuatro estados de espera. ¿Qué señal

DTACK* puede inducir estos estados de espera?

a)

b)

c)

d)

CLK

S7

S0

S1

S2

S3

S4

SW

SW

SW

SW

S5

S6

S7

S0

DTACK*

S7

S0

S1

S2

S3

S4

SW

SW

SW

SW

S5

S6

S7

S0

S7

S0

S1

S2

S3

S4

SW

SW

SW

SW

S5

S6

S7

S0

DTACK*

(2)

CLK

DTACK*

(3)

3. ¿Cuántos ciclos de bus (lectura y escritura) son llevados a cabo para leer y ejecutar la

instrucción MOVE.L #1,$30000?

a) 1 ciclos de lectura, 2 de escritura

b) 5 ciclo de lectura, 2 de escritura

c) 7 ciclo de lectura, 2 de escritura

d) Ninguna de las anteriores

F(a,b)

a*b*c*/d

/a*b*c*d

a*b*/c*d

Ninguna de las anteriores

*

d

q

DFF

clk

(1)

CLK

LUT

7. Se desea describir en VHDL un circuito cuya funcionalidad es la del de la figura. ¿Qué

descripcione/s es/son correcta/s para este propósito?

a

b

Solamente la 1

Solamente la 2

Solamente la 3

Ninguna de las respuestas anteriores es cierta

I0

I1

I2

I3

architecture arq1 of circuito is

signal x: std_logic;

begin

process(clk)

begin

if rising_edge(clk) then

o<=x;

end if;

end process;

x<=a and b;

end architecture;

architecture arq3 of circuito is

begin

process(clk)

variable x: std_logic;

begin

if rising_edge(clk) then

o<=x;

x:=a and b;

end if;

end process;

end architecture;

o

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity circuito is

port(

clk: in std_logic;

a,b: in std_logic;

o: out std_logic);

end entity;

architecture arq2 of circuito is

signal x: std_logic;

begin

process(clk)

begin

if rising_edge(clk) then

x<=a and b;

o<=x;

end if;

end process;

end architecture;

a)

b)

c)

d)

10.

a)

b)

c)

d)

Solo arq1

Solo arq2

Solo arq3

Todas

Señalar la afirmación incorrecta sobre el VHDL:

Las señales de tipo std_logic son de tipo resuelto

Las asignaciones de señales llevan siempre un retardo, si no es especificado es delta (δ)

Las asignaciones de variables nunca llevan retardo

Alguna de las anteriores es falsa

8. La funcionalidad del circuito descrito en VHDL es:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity cnt is

port(

clk,rst,e: in std_logic;

o: out std_logic_vector(0 to 7));

end entity;

a)

b)

c)

d)

architecture beh of cnt is

begin

process

variable a: signed(o'range);

begin

wait until rising_edge(clk);

if rst='1' then

a:=(others=>'0');

elsif e='1' then

a:=a-1;

end if;

o<=std_logic_vector(a);

end process;

end architecture;

Contador descendente BCD natural de 8-bits, con reset síncrono y habilitación

Contador descendente BCD natural de 8-bits, con reset asíncrono y habilitación

Contador descendente BCD complemento A2 de 8-bits, con reset síncrono y habilitación

Contador descendente BCD complemento A2 de 8-bits, con reset asíncrono y habilitación

9. A partir del anterior contador, se desea generar un contador de N-bits genérico conectando

W=N/8 contadores de 8-bits. Las descripciones estructurales correctas son:

library ieee;

use ieee.std_logic_1164.all;

entity cntX is

generic(N: integer:=32);

port(

clk,rst,e: in std_logic;

o: out std_logic_vector(0 to N-1));

end entity;

architecture str2 of cntX is

constant W: integer:=N/8;

signal ex: std_logic_vector(0 to W-1);

signal ox: std_logic_vector(o'range);

begin

o<=ox;

gen0: for i in 0 to W-1 generate

gen1a: if i=W-1 generate

ex(i)<=e;

end generate;

end1b: if i/=W-1 generate

ex(i)<=ox(8*(i+1)) and ex(i+1);

end generate;

cntx: entity work.cnt port map

(clk,rst,ex(i),ox(8*i to 8*(i+1)-1));

end generate;

end architecture;

a)

b)

c)

d)

Solo str1

str1 y str2

Solo str3

Todas

architecture str1 of cntX is

constant W: integer:=N/8;

signal ex: std_logic_vector(0 to W-1);

signal ox: std_logic_vector(o'range);

begin

o<=ox;

gen0: for i in W-1 downto 0 generate

gen1a: if i=W-1 generate

ex(i)<=e;

end generate;

end1b: if i/=W-1 generate

ex(i)<=ox(8*(i+1)) and ex(i+1);

end generate;

cntx: entity work.cnt port map

(clk,rst,ex(i),ox(8*i to 8*(i+1)-1));

end generate;

end architecture;

architecture str3 of cntX is

constant W: integer:=N/8;

signal ex: std_logic_vector(0 to W-1);

signal ox: std_logic_vector(o'range);

begin

o<=ox;

gen0: for i in 0 to W-1 generate

gen1a: if i=0 generate

ex(i)<=e;

end generate;

end1b: if i/=0 generate

ex(i)<=ox(8*i-1) and ex(i-1);

end generate;

cntx: entity work.cnt port map

(clk,rst,ex(i),ox(8*i to 8*(i+1)-1));

end generate;

end architecture;

Nombre________________________________________________________________

Pregunta

1

2

3

4

5

6

7

8

9

10

A

B

C

X

D

X

X

X

X

X

X

X

X

X