1. - Cenidet

Anuncio

. ...

S.E.I.T.

S.E.P.

D.G.I.T.

C E N T R 3 NACIONAL DE INVESTIGACION

Y DESARROLLO TECNOLOGICO

“DISEÑO DE UN EQUIPO PARA EL DIAGNOSTICO DE TARJETAS INTELIGENTES

CON BASE EN UNA COMPUTADORA

PERSONAL”

T

QUE

s

E

PARA

MAESTRO

OBTENER

EN

INGENIERIA

P

R

E

ANTONIO

S

s

I

EL

GRADO

DE

EN

CIENCIAS

u

cg* 1 LINT

ELECTRONICA

E

N

CARRILLO

T

A

:

GARCIA

CENTRO DE INFOP~ACION

CENIDET

JCUERNAVACA. MOR.

,

ABRIL

DE 1991

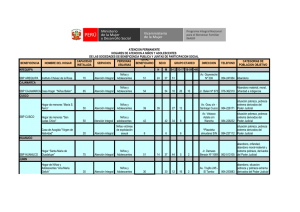

OlRECClON GENERAL DE INSTITUTOS TECNOLOGICOS

CENTRO NACIONAL DL NVEOtlQACKlNY KURROLLOTCCNOLOQiCO

ACADIWIA DE

LA WSTRIA EN iIüGENIERU ELEXTRüNICA

StCRElbRIA

Of

lDUUClON WOLICI

Cuernavaca, Mor., a 29 de abril de 1991.

DK. Juan Manuel Ricaño Castillo

Director del CENIDET

P r e s e n t e

Am.- M. C. Alejandro Díaz B .

Coordinador de Electrónica

Por este conducto, hacemos de su conocimiento que, después de

haber sometido a revisión el trabajo de tesis titulado:

-

" DISEÑO

DE UN EgUIPO PARA EL DIAGNOSTICO DE TARJETAS

INTELIGENTES CON BASE EN üNA COHPUTAMRA PERSONAL"

-

Desarrollado por el Ing. Antonio Carrillo Garcfa, y hab.iendo cumplido con todas las correciones que se le indicaron, estamos de

acuerdo en que se le conceda la fecha del examen de grado.

DlRECClON GENERAL DE INSTITUTOS TECNOLOGICOS

cEwrno m o t uOLP(VE~~ICK)I(Y KMRROLWTECUOLOOICO

COORD. ACADEIIICA.

C u e r n a v a c a , Mor.,

a 29 d e abri.1 d e 1991.

Ing. A n t o n i o C a r r i l l o G a r c f a

C a n d i d a t o al G r a d o d e M a e s t r o

en Ciencias en Ingenierfa

Electrónica.

P r e s e n t e .

D e s p u é s d e h a b e r s o m e t i d o a r e v i s i ó n su t r a b a j o d e t e s i s

titulado:

"

D I S E N I DE UN E Q U I P O PARA EL D I A G N O S T I C O DE TARJETAS =

I N T E L I G E N T E S CON BASE EN UNA COMPUTADORA PERSONAL

"

Y h a b i e n d o c u m p l i d o c o n t o d a s las i n d i c a c i o n e s q u e el

--

J u r a d o R e v i s o r d e t e s i s le hizo, s e l e c o m u n i c a q u e s e

le c o n c e d e a u t o r i z a c i 6 n . p a r a q u e p r o c e d a a la i m p r e s i ó n

d e la m i s m a , c o m o r e q u i s i t o para la o b t e n c i 6 n del grado.

A t e n t a m e- n t e

M.C.ordn$$$)A

Dfaz Sánchez

C o o r d i a o r d e la M a e s t r f a

en I n g e n i e r l a E l e c t r 6 n i c a .

C.C.P.:

Ilrr.

Expediente.

rl D

Dedico esta memoria de tesis:

A Dios por su grandeza.

A mis Padres Benita y Antonio

por el amor y cariño que me han

dado a lo largo de mi vida.

A mis hermanos Gerardo, Rosa Man's,

Juana Leticia, Octavio y Elodia

por su apoyo y confianza.

A mis sobrinos porque son

la esperanza de la familia.

Agradezco:

Al Centro Nacional de Investigación

y Desarrollo Tecnológico

(CENIDET)

Al Consejo Nacional de Ciencia y Tecnología

(CONACYT)

Al Instituto de Investigaciones Eléctricas

(IIE)

Al comité revisor:

M.C. José M. Gómez López

M.C. Alejandro Díaz Sánchez

M.C. José A. Herrera Corral

Especialmente al M.C. Guillermo Cahue Díaz.

y al Ing. Pablo R. de Buen Rodriguez.

el apoyo y comentarios brindados para la realización de este trabajo.

2

Contenido

Introducción

1 P a n o r a m a general de los equipos de prueba.

1.1

1.2

1.3

1.4

. . .... . . . .. . . .... . . ..

Cualidades deseables en un EP.

. . .. , . . . .. ..

Tipos de equipos de prueba. . . . . . . . . . . . . . . . . . . . . . . .

Técnicas de prueba. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.1 Emulación como técnica de prueba. . . . . . . . . . . . . . . .

1.4.1.1 Emulación de CPU. . . . . . . . . . . . . . . . . . .

1.4.1.2 Emulación de ROM. . . . . . . . . . . . . . . . . . .

Elementos de un equipo de diagnóstico de fallas.

1.4.1.3

Emulación basada en bus.

...............

2 P l a n t e a m i e n t o del proyecto.

. . . . I. . . . . .

.....,..........I .....

2.1

La computadora personal como estación de trabajo.

2.2

Técnica de prueba empleada.

I

I

i

3

7

8

9

11

12

13.

14

16

16

18

2.3

Características del sistema. . . . . . . . . . . . . . . . . . . . . . . . .

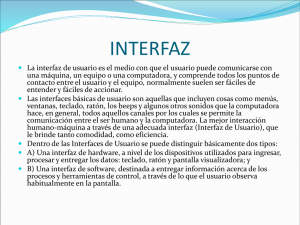

3 Descripción de la interfas

22

3.1

Descripción a bloques de la tarjeta interíaz .

3.2

Descripción detallada de cada bloque

24

3.2.1

24

...................

Sección procesadora . . . . . . . . . . . . . . . . . . . . .

..

3.2.1.1

Direccionamiento . . . . . . . . . . . . . . . . . . . .

3.2.3

Sección de interfaz . . . . . . . . . . . . . . . . . . . . . . . . . .

25

28

......................

Generador de firma . . . . . . . . . . . . . . . . . . . . . . . .

Interfae con la PC . . . . . . . . . . . . . . . . . . . . . . . . .

30

Teoría de funcionamiento. . . . . . . . . . . . . . . . . . . . . . . . .

34

3.2.6

Detector de nivel lógico

Software de la tarjeta interfaz

4.1

22

. . . . . . . . . . . . . . . . 25

Sección de control y temporización

3.2.5

3.3

..............

3.2.2

3.2.4

4

.

19

.

30

32

41

Interfaz con el usuario . . . . . . . . . . . . . . . . . . . . . . . . . . .

RAM . . . . . . . . . . . . . . . . . . . .

41

4.1.1

Pruebas de memoria

4.1.2

Pruebas a la memoria ROM . . . . . . . . . . . . . . . . . . . .

45

4.1.3

Obtener mapa de memoria .

...................

46

4.1.4

Localizar Fallas. . . . . . . . . . . . . . . . . . . . . . . . . . .

46

4.1.5

Punta de Prueba .

48

.........................

..

11

42

4.1.6

4.2

Control de líneas.

Programa monitor.

. . .. .. . . . . .. .. . . . .. .. .. . .

. ..... . . . .. . . . . ... .. . . . . . . ..

5 Pruebas al sistema.

48

48

62

5.1 Temporización de algunas señales de la tarjeta interfaz.

...... ..

e

54

6 Conclusiones.

60

A Rutas criticas.

87

B Características eléctricas y mecánicas de la tarjeta.

79

B.1 Características eléctricas.

. .. . . . . . .. .. . .. .. .... .. ..

B.2 Características mecánicas.

. . . . . . . . . . . .. . . . . . .. .. ..

73

74

C Componentes de la tarjeta.

76

D Funciones de los programas.

80

E Hojas de datos.

82

Glosario de términos técnicos

...

111

Las compañías electrónicas han buscado una forma efectiva de probar sus productos desde los primeros días de la radio.

Como la radio y los equipos electrónicos crecieron en complejidad, se tuvo la

necesidad de diseñar equipos con capacidades de prueba más precisas y confiables,

de tal forma que las organizaciones empezaron a confiar niás en la “electrónica que

prueba a la electrónica”.

Con los años, los bancos de prueba’ se multiplicaron tan rápido como la expansión del campo de la electrónica; osciladores, multímetros, osciloscopios llenaban dichos bancos. Para probar una tarjeta digital los técnicos le aplicaban voltaje,

montaban cables entre los puntos a probar y el equipo de prueba; colocaban los

valores deseados (escala, cuadrante, etc.), hacían las mediciones y grababan los resultados a través de un procedimiento de prueba paso a paso que algunas veces

tomaba horas. El método de banco de pruebas desperdiciaba mucho del tiempo del

técnico.

El paso lógico fué remover mucho del control humano en pasos de rutina y

automatización de ciclos de prueba. De ésta forma nacieron los Equipos Automáticos

de Pruebas (ATE, por las siglas en inglés Automated Test Equipment), los cuales

llevan a cabo las pruebas más rápido y eficientemente, además de consumir menos

tiempo durante el desarrollo de las miamas.

El uso de las computadoras personales’ y la automatización han reemplazado

a aquellos trabajadores que desempefian labores poco calificadas y repetitivas. Para

nadie es desconocido que la automatización inteligente provocará una segunda revolución industrial. No obstante, en esta revolución, los trabajadores que serán

reemplazados por las máquinas pertenecerán a un nivel medio, donde entrarían

todos aquellos trabajos que exigen la toma de decisiones mediatas.

Las innovaciones en hardware y software en el área de las computadoros personales, aunadas a la potencia y flexibilidad de los Equipos de Prueba (EP) ha provocado que la conjunción de los dos campos anteriores llegue a ser una herramienta

‘Area donde se instala equipo para la detección y corrección de fallas

ZA lo largo de éste trabajo se emplearan las siglas PC

iv

muy aceptada para probar sistemas, de esta forma la P C entró al mundo de los

equipos orientados a la detección de fallas, el cual fué una vez territorio exclusivo

de medianas y grandes computadoras. Es posible equipar una PC con una interfaz

hardware y el apropiado software para permitir que funcione como un instrumento

que maneje aplicaciones de los EP.

,

Este proyecto surgió de la necesidad que se tenía en el área de mantenimiento

de computadoras personales del Instituto de Investigaciones Eléctricas de contar con

una herramienta auxiliar para el diagnóstico de tarjetas inteligentes (basadas en el

microprocesador 8086 de Intel), que conformara ciertas características que dieran

sobre todo una facilidad de manejo para el usuario:

1. Debe ser operado a base de menúes, permitiendo introducir los datos más

necesarios.

2. A través de todo el procedimiento de diagnóstico, el usuario debe contar con

opciones de ayuda que de alguna manera expliquen la forma de ejecutar cierta

prueba.

3. El sistema debe tener una rutina de autoprueba e indicar si existe algún error

en el sistema de prueba.

4. Para un mejor u80 del sistema, es recomendable que el usuario tenga experien-

cia en la detección de fallas. El usuario debe comprender el funcionamiento

del sistema a probar.

OBJETIVO.

El objetivo de este proyecto es diseñar y construir un sinterna de diagnóstico,

capaz de ejecutar una serie de pruebas en circuitos digitales basados en el rnicmpmesador 8086, y orientadas éstas a detectar y aislar las fallas ezistentes, utilizando

como técnica de prueba la emulación de CPU.

En términos generales, el sistema consistirá de lo siguiente:

Una tarjeta interfaz, la cual se inserta en una ranura de expansión de una PC

compatible con IBM

V

vi

Un programa ejecutándose en la computadora cuya función será controlar a la

tarjeta y proporcionar un ambiente agradable al usuario.

Una punta de prueba, para obtener y aplicar niveles de voltaje.

Utilizando los componentes mencionados el sistema debe ser capaz de ejecutar

pruebas principalmente a la memoria RAM, ROM, accesar puertos de entrada y

salida, determinar el estado lógico para un punto dado del sistema bajo prueba

(SBP), leer y escribir localidades de memoria, aplicar pulsos a través de la punta de

prueba y obtener un análisis de firma para los puntos deseados.

El proyecto está desarrollado de la siguiente forma: En el capítulo 1s e presenta un panorama general de los equipos de prueba. El capítulo 2 comprende el

planteamiento del proyecto y las características que debe tener el sistema diseñado.

El capítulo 3 presenta la forma en que se diseiió la circuitería del sistema, en base

a los requerimientos establecidos. El capítulo 4 presenta el software que controla la

tarjeta interfaz. El capítulo 5 describe algunas pruebas de funcionamiento as1 conlo

la temporización de señales de la tarjeta interfaz desarrollada y en el capítulo 6 se

presentan las conclusiones.

Capítulo í

Panorama general de los equipos

de prueba.

Las organizaciones que utilizan equipo capaz de ejecutar prueban electrónicas, han

experimentado un gran número de beneficios. Pocos desarrollos han mejorado la

calidad de los productos y la productividad en la industria electrónica tanto como

los equipos de prueba.

Un equipo de pruebas puede definirse como un sistema capaz de ejecutar sobre un dispositivo una secuencia de pruebas predefinidaa y tomar decisiones concernientes al mismo en baae a los resultados de dichas pruebaa[i].

Estos equipos realizan pruebas en un tiempo menor al necesario para un conjunto de pruebas manuales donde las interconexiones, ajustes, mediciones y grabaciones deben ser realizadas manualmente. Un operador con un adiestramiento adecuado puede llevar a cabo pruebas muy complejas con un equipo de éstos. En

algunas ocasiones, las especificaciones y características del Sistema Bajo Prueba'

(SBP, por Sistema que va a ser probado) son tan complejas y los requerimientos de

datos son tantos, que solamente u n EP puede manejarlos.

,

Los EP también contribuyen a elevar la calidad del producto a través de la

transferencia de control sobre el ciclo de prueba del operador a un controlador

electrónico, esto es, la serie de pruebas que deben ser aplicadas a u n producto no

-

'A lo largo de éste trabajo se usara indistintamente sistema bajo prueba y tarjeta bajo prueba

1

CAPíTULO 1. PANORAMA GENERAL DE LOS EQUIPOS DE PRUEBA.

2

son realizadas manualmente, sino por un EP. Los departamentos de prueba pueden

entonces, minimizar los errores, omisiones, fallas de decisión, medidas erróneas y

otras tantas desventajas de un control humano. Este beneficio resulta en un período

de medición más corto y por consiguiente, en un ahorro monetario, ya que el costo

de corrección de errores y falias se incrementan en cada paso del proceso productivo

en que son olvidados. Además, un equipo de estos elimina muchos pasos repetitivo6

y tediosos, dejando al operador aquellos que requieren juicio humano.

Sin embargo, hoy en día los probadores de sistemas digitales independientemente de aplicar estímulos y verificar resultados deben hacer comparaciones y tomar

decisiones, debido principalmente al surgimiento de sistemas muy complejos que requieren pruebas más sofisticadas y con mayor precisión. Esto trae como consecuencia

que los probadores aumenten y mejoren sus capacidades de detección de fallas.

Algunas de las características típicas de los sistemas digitales modernos son:

1. Componentes complejos o arreglos de componentes, los cuales requieren cientos

de vectorea de prueba’ para ser verificados.

2. Reloj integrado, el cual controla la temporización de los circuitos en el sistema,

requiriendo que el probador se sincronice a él para poder controlar la actividad

del sistema.

3. Buses multiplexados los cuales llevan diferente información en diferente tiempo, requiriendo que un probador comprenda y ejecute el protocolo para acceBar

el bus.

4. Dispositivos secuenciales, tales como contadores y flip-flops con rangos de reloj

superiores a 1 Mhz.

5. Dispositivos “inteligentes”, tales como microprocesadores (pp) y microcontro-

ladores:

Las dos principales fuentes de problemas para llevar a cabo pruebas son la

complejidaddel circuito a ser probado y la escasez de contmlabilidad y observabilidad

de sus componentes[2]. Un método para reducir la complejidad es describirlo al nivel

de arquitectura (figura l . l ) ,en este nivel se tienen menos componentes y por lo tanto

‘Serie de pruebas predefinidas para ejecutarse en un equipo o componente

CAPITULO 1 . PANORAMA GENERAL D E LOS EQUIPOS DE PRUEBA.

NIVEL DE

NIVEL FUNCIONAL

3

I

COMPUERTA

RANSIS

Figura 1.1: Niveles de descripción de circuitos.

la descripción disminuye, aunque el control y la observabilidad sobre un elemento en

particular se pierde. Por otro lado, si se elige describir un circuito a nívei funcional

se tendrá m b control sobre sus componentes, pero la descnpuón (complejidad)

aumenta.

Como se muestra en la figura 1.1 el nivel más bajo para describir un circuito es

el nivel de transistor pero la cantidad de componentes es tan grande que resultaría

muy difícil llevarla a cabo. Un grupo de transistores constituyen las compuertas

lógicas que forman el siguiente nivel. Un grupo de compuertas constituyen a su vez

el siguiente nivel (funcional) que pueden ser sumadores, multiplexores, flip-flops, etc.

' En el nivel más alto bloques funcionales son combinados para formar dispositivos

más complejos como microprocesadores, microcontroladores y sus dispositivos de

soporte.

1.1

Cualidades deseables en un EP.

Las características de los sistemas digitales actuales implican la necesidad de que

un EP y en general cualquier equipo orientado al diagnóstico de fallas tenga las

cualidades enumeradas a continuación (se hace una analogía con lo escrito por

Fichtenbaum(3] para los EAP); aunque es importante mencionar que durante el

desarrollo de este trabajo se determinó que hacían falta otras dos: protecciones y

complejidad.

. .

CAPÍTULO 1. PANORAMA GENERAL DE LOS EQUIPOS D E PRUEBA.

ipREGISTRO

DIRECCION

CONDI-,RESUL-+

CION DE TAD0

SALTO

REUSXO

PIPELINE

MEMORIA

---)

REGISTRO

DEL +AL

PIPELINE

REG*STRo +COMPARA-- REGISTRO

DEL

DEL

CION

PlPELlNE

PlPELlNE

-

4

SBP

SBP

Figura 1.2: Estructura de un EP utilizando pipeline. El flujo de datos desde el

registro de dirección del controlador hasta el candado de resultados incluye 5 etapas.

1. VELOCIDAD DE PRUEBA. La habilidad para aplicar y sensar vectores de

prue6a a alta velocidad proporciona mucha ventaja a un EP. Un EP rápido

puede sincronizarse al sistema digital bajo prueba y operar los dispositivos

dinámicos a su máxima velocidad, mejorando de esta forma la eficiencia de la

prueba. Comparado con el hardware de un EP de baja velocidad, éste puede

requerir componentes más rápidos y sobre todo una estructura que permita

ejecutar más operaciones en paralelo. Las conexiones entre el EP y el SBP son

importantes, ya que deben llevar los vectores de prueba y obtener los resultados

con la m'nima cantidad de ruido posible (producido por la alta frecuencia) y

que las entradas del EP no "carguen" las salidas del SBP o viceversa además,

el flujo de señales internas del EP no deben producir retardos en las señales

de control del SBP.

2. PIPELINE. Cuando un EP opera a velocidades de prueba altas el tiempo

requerido para buscar un patrón de la memoria, aplicarlo al SBP, leer y cornparar la respuesta y tomar la decisión basada en la comparación de resultados

puede exceder el tiempo de un paso de prueba, haciendo lento el proceso; en

cambio si se tiene una estructura en pipeline la velocidad aumenta debido a

que todas su6 secciones procesan información en forma paralela. Lo anterior

trae como comecueticia rapidez en las pruebas y resultados inmediatos para el

operador.

En la figura 1.2 se muestra una estructura en pipeline, en la cual un dato de

una prueba debe avanzar de un registro a otro cada paso de prueba.

Aunque un patrón de prueba necesita 5 pasos de prueba para atravesar toda

la estructura, debido a la sucesión de etapas, un nuevo patrón es aplicado al

CAPíTULO 1. PANORAMA GENERAL DE LOS EQUIPOS DE PRUEBA.

SEÑAL DE COMPARACION

SBP-RELOJ

y w

I

SERAL DE ,

SlNCRONIA

DEL SBP DETECTOR

DE FASE

L

- 1

Y.c.o.

5

I

~ T E M P O R l Z A C I O N r

DEL EP

J

DEL EP

Figura 1.3: Un lazo amarrado en fase sincroniza la señal de temporización del EP

con una señal de reloj del SBP.

SBP cada vez que transcurre un paso de prueba, acelerando de esta forma el

ciclo.

3. SINCRONIZACION CON EL SBP. Cuando el sistema a ser probado contiene

su propio reloj, el EP debe tener la capacidad de sincronizarse a él, aún cuando

el EP suministre las señales de control básicas.

Existen varias clases de sincronización. En la primera, el EP debe alinear el

reloj interno y sus señales de tiempo a las señales del SBP, ésto es a menudo

llevado a cabo utilizando técnicas de amarrado en fase como la mostrada en

la figura 1.3.

*

Una segunda técnica de sincronización es utilizando señales de ESPERA y

LISTO; como ejemplo un microprocesador enviando un dato al puerto serie

y después esperar el reconocimiento por la línea LISTO; en el momento en

que ésta se active, enviar el siguiente dato y así sucesivamente. Si en un

determinado tiempo no se activa la señal LISTO se despliega un letrero de

error (ver figura 1.4).

Una técnica más sencilla es la que utiliza un mismo reloj tanto para el EP

como para el SBP, de tal forma que los dos sistemas trabajan al menos a la

misma velocidad. Esto es, el reloj del SBP es utilizado como base de tiempo

por el equipo de diagnóstico como se muestra en la figura 1.5.

4. OPERACION ORIENTADA AL BUS. Un EP que interactúa con dispositivos

orientados al bus, tales como la mayoría de los componentes de un sistema

basado en un microprocesador, debe actuar tal como un dispositivo de bus.

Más que conformar las características eléctricas del bus, debe manejar y visualizar el estado del bus en el momento exacto. El EP en cuestión requiere

--

CAPlTULO 1. PANORAMA GENERAL DE LOS EQUZPOS DE PRUEBA.

MICIIO'liOCESA DO A

EP

PUEIIIO

SERIE

DATOS

ESPERA

-

DATOS

RELOJ

4 SISTEMA

BAJO

J

PRUEBA

Figura 1.5: Sincronización utilizando un mismo reloj el El' y el SBP.

6

CAPi'TULO 1. PANORAMA GENERAL DE LOS EQUIPOS DE PRUEBA.

7

terminales con capacidades eléctricas de 3 estados, suficiente velocidad y a.

ceptable carga eléctrica.

En un

con microprocesador, éste ejecuta una sene de instrucciones,

cada instrucción consiste de una secuencia definida de

ciclos de

o

bus de varios tipos (por ejemplo: ciclo de lectura, de escritura, reconocimiento

de interrupción, etc.), y cada tipo de ciclo de bus tiene un patrón definido

de flancos de reloj, señales de control y transferencia de datos. Mientras las

particularidades de los ciclos de bus y de instrucción difieren entre los diferentes microprocesadores, Is estructura fundamental es la misma; esto es lo

siguiente: todo microprocesador para ejecutar una lectura a memoria debe

activar una señal de ledura, otra para indicar cuando se tiene una dirección

válida y debe contar con una señal para capturar el dato, no importa que tipo

de microprocesador se utilice, sus líneas de control son semejantes. Este hecho

puede ser usado para implementar un EP que pruebe sistemas basados en un

microprocesador, haciendo que la estructura del probador wfleje la estructura

de la actividad del bus.

Cuando un EP es construido para que tome la ventaja de esta estructura para

un SBP dado, el programador de la prueba escribe en términos de instrucciones

al procesador.

5. PRECISION. Es obvio que un EP cuyas mediciones sean precisas será mucho

máa confiable que otros. La alta precisión en las pruebas puede ser apropiada

para sistemas basados en flancos, esto es, sistemas que con cada cambio de

nivel en el reloj cambian su comportamiento. De nada vale el tener rapidez en

las pruebas si no se cuenta con la suficiente precisión.

6. PROTECCIONES. Sin duda alguna una parte fundamental de todo equipo

electrónico son las protecciones contra sobrecorriente, elevación del voltaje y

corto circuito. Los equipos de prueba deben contar con detectores contra las

situaciones ya mencionadas, reportarlas al operador y sobre todo realizar una

acción para aislar la falla y evitar algún posible daño a m i s componentes.

7. COMPLEJIDAD. Un EP muy complejo (en cuanta a manejo e interfaz con

el usiiario) puede ser difícil de utilizar, por lo tanto debe tener un aceptable

grado de sencillez sin perder ninguna de las características mencionadas anteriormente. Mientras más amigable al operador sea un equipo tendrá niayor

aceptación.

CAPíTULO 1. PANORAMA GENERAL DE LOS EQUIPOS DE PRiJEBA.

1.2

8

Elementos de un equipo de diagndstico de

fallas.

LOS

sistemas orientados al diagnóstico de fallas varían mucho en cuanto a su arquitectura, por lo tanto es muy difícil generalizar, sin embargo, la mayoría de ellos

contienen los siguientea elementos(4]:

1. Un controlador (Generalmente una minicomputadora, microcomputadora, calculadora o un controlador de bus dedicado).- Maneja el ciclo de prueba, controla el flujo de datos, recibe los resultados de las mediciones, ejecuta cálculos

y despliega la información en pantalla o impresora.

2. Generador de señales.- Suministra las señales de entrada al sistema bajo prueba,

puede ser una fuente de poder, generador de funciones o convertidores D / A .

Existen varios medios para aplicar estas señales (y también leerlas), algunos

pueden ser: bed of nails (camas de clavos), conectores, puntas de prueba, clips,

etc.

3. Instrumentos de medición.- Miden las señales de salida del sistema bajo prueha;

pueden ser contadores de frecuencia, multímetros digitales o cualquier otro

dispositivo de medición.

4. Sistema de conmutación.- Conmuta las señales entre el sistema bajo prueba y

otros elementos del equipo de pruebas.

5. Interfaz operador-equipo.- Puede aei parte del controlador, toma la forma de

luces, interruptores o una pantaiia en una consola de control. A menudo el

operador proporciona información al controlador por medio de un teclado.

Debido a la8 necesidades de expansión de los equipos de pruebas, un gran

número de compañías ha entrado al mercado, otras construyen sus propios sistemas

debido a que los pueden fabricar para una necesidad específica. Algunos equipos

de diagnóstico son totalmehe automáticos, ellos requieren solamente un operador

para que carge y remueva los SBP y presione un botón o dos. Los sistemas semiautomáticos requieren un técnico para que ajuste las señales, realice las mediciones o

controle una punta de prueba.

CAPíTULO 1. PANORAMA GENERAL DE LOS EQUIPOS DE PRUEBA.

9

Normdmente los EP funcionan a base de programas, los cuales contienen las

pruebas que se van a realizar en el sistema digital y el orden en que se desean realizar

las pruebas. Los programas de los equipos de diagnóstico para pruebas y localizacion

de fallas del SBP son generalmente creados de dos formas:

1. A través de un lenguaje de programación se describen los pasos que se llevan

a cabo para ejecutar las pruebas.

2. Un ingeniero utiliza un paquete de preparación de programas de pruebas utilizando herramientas CASE, CAE, CAD, etc..

1.3’ Tipos de equipos de prueba.

Establecer una clasificación de los equipos de prueba existentes depende de que

factor o característica es el predominante para llevarla a cabo, esto es lo siguiente:

cierta persona puede clasificar los equipos de prueba tomando como base el grado

en el cual interactúa con el usuario en: manuales, semiautomáticos y automáticos.

En los equipos de prueba manuales el usuario es el responsable de ajustar los

sontroles e incluso interpretar resultados y tomar decisiones; los semiautomáticos son

aquellos en que el control de las pruebas y las pruebas mismas son llevadas a cabo

tanto por el usuario como por el equipo; los automáticos comprenden los equipos en

que el usuario deja al equipo toda la responsabilidad de ejecutur pruebas, obtener

resultados y tomar decisiones.

Quizá una clasificación más utilizada es aquella en la cual se toma en cuenta la

técnica que el equipo de pruebas emplea para ejecutar las pruebas, por lo anterior

en la siguiente sección Be hace una descripción de las diferentes técnicas en las cuales

pueden estar basados los equipos de prueba.

I

1.4

TGcnicac de prueba.

Existen en el mercado una gran variedad de equipos de diagnóstico, ellos va1ía.n

considerablemente en su construcción, capacidades y sobre todo en la técnica para

CAPÍTULO 1. PANORAMA GENERAL DE LOS EQUIPOS DE PRUEBA. 10

detectar fallas. Las técnicas mas comúnmente utilizadas son: in-circuit, funcional,

comparación, semiconductores y componentes y emulación.

A continuación se describe brevemente cada una de estas técnicas.

1. 'I'ECNICA DE PRUEBA IN-CIRCUIT.

sistemas que utilizan esta técnica prueban la tarjeta bajo prueba a nivel

componente, esto es, pueden aislar los componentes y aplicarles señales a

uno de ellos en forma individual, en base a las respuestas obtenidas determina

Si alguno de éstos está fallando; además son capaces de detectar corto circuito

entre pistas y circuitos abiertos. Generalmente, la tarjeta se coloca en una

U

cama de clavos", la cual contiene un número de terminales que hacen contacto

en los puntos deseados de la tarjeta. Un sistema neumático la presiona contra

las terminales para obtener un buen contacto. A través de las terminales se

obtienen las señales para cada pista de la tarjeta. Ventajas: Se ha estimado

que estos sistemas aislan hasta un 98% de las fallas más comúnes en sistemas

digitales , tiene capacidad para detectar corto-circuito y es de las técnicas más

confiables. Desventajas: El principal problema al que se enfrenta esta técnica

es cuando la tarjeta bajo prueba (TBP) contiene pistas o puntos que no son

muy visibles a las terminales, además puede existir el caso en que no se logre

un buen contacto y las lecturas obtenidas sean erróneas.

LOS

2. TECNICA DE PRUEBA FUNCIONAL.

Considerada la técnica de prueba más tradicional para probar circuitos, consiste en ejecutar pruebas en u n CBP aplicandole varios estímulos en sus entradas, después se miden las salidas del sistema y se comparan los resultados

con las respuestas esperadas, previamente almacenadas en la memoria. Ventajas: es una técnica relativamente sencilla y confiable. Desventajas: es necesario contar con una buena base de datos para llegar a detectar el problema

y además con esta técnica no es posible probar todos los componentes del

sistema ya que realiza pruebas por módulo.

3. TECNICA DE PRUEBA POR COMPARACION.

Esta técnica consiste en comparar la TBP con una unidad de referencia que

funciona perfectamente. El probador aplica las mismas sexiales a ambas unidades simultáneamente, después compara sus salidas, si las respuestas difieren,

el sistema puede guiar al usuario hacia la localización de la falla usando una

técnica de probador-guía, la cual consiste en tener u n a punta de prueba controlada por el sistema y colocarla en puntos o pistas estratégicas de la TBP, de

..

CAPI’TULO 1. PANORAMA GENERAL DE LOS EQUIPOS DE PRUEBA.

11

esta forma se pueden detectar los puntos que no tienen el nivel lógico deseado.

Ventajas: Es posible probar todos los componentes de la TBP y e8 económico.

Desventajas: Bajo esta técnica muchas veces es tedioso estar controlando manualmente la punta de prueba, se pueden cometer errores al colocarla en el

lugar equivocado y el diagnóstico sería erróneo y además es necesario contar

con una unidad en buen estado.

4. TECNICA DE PRUEBA PARA SEMICONDUCTORES Y COMPONEN-

TES.

Esta técnica consiste en probar componentes individuales ya sean digitales:

compuertas (incluyendo circuitos VLSI), memorias y microprocesadores; otros

se especializan en dispositivos analógicos como transistores, diodos, tiristores,

etc. Ventajas: su construcción es relativamente barata, puede probar individualmente los componentes. Desventajas: Para probar los dispositivos contenidos en una TBP es necesarios removerlos sin dañarlos, lo cual puede resultar un procedimiento tedioso y durante el cud, si no se toman precauciones es

posible dañar la tarjeta.

5. TECNICA DE PRUEBA POR EMULACION.

Con esta técnica se tiene un dispositivo cuyo comportamiento es similar al de

otro dispositivo, e incluso es capaz de sustituirlo sin alterar en gran medida el

funcionamiento de la TBP. De tal forma que se tiene un control sobre el diapositivo emulador y por consiguiente sobre la TBP. Básicamente, existen tres

tipos de emulación(5): emulación de CPU,emulación de memoria y emulación

basada en bus.

Debido a que en este proyecto se utilizó fa emulación como técnica de prueba,

en párrafos siguientes se profundiza más en el tema.

Algunos sistemas de diagnóstico utilizan como complemento una técnica Ilamada Análiais de firnu, la cual se basa en una compresión del flujo de datos3 que

pasan por un determinado punto en un sistema digital, dando por resultado u n a

única firma para ese punto. Normalmente la firma está constituida por 4 dígitos

hexadeciniales. Si un mismo dato pasa por un mismo punto en un período de

tiempo, entonces ese punto tendrá la niisma firma cada vez.

%e refiere al hecho de transformar n bits serie a una palabra de m bits en paralelo

CAPíTULO 1. PANORAMA GENERAL DE LOS EQUIPOS DE PRUEBA.

1.4.1

12

Emulación como técnica de prueba.

Se define como Emulación a la capacidad que tienen atgunos dwpositiaos (o equipos)

de sustituir a otro igualando sua camcterísticas y/o capacidades, de tal modo que no

afecte en gmn medida el ambiente en el cual fmbaja.

,

Como se mencionó anteriormente existen tres tipos básicos de emulación:

1. Emulación de CPU. El microprocesador es reemplazado por una interfaz basada

en un CPU.

2. Emulación de Memoria. En la cual, la ROM es reemplazada por otra programada en forma separada y es utilizada para iniciar funciones de prueba.

3. Emulación basada en bus (bus-based emulation). En esta técnica el microprocesador es deshabilitado y el probador inicia funciones para probar el hardware desde el bus.

1.4.1.1

Emulación de CPU.

T o m o técnica de prueba, los emuladores disefiados específicamente para sistemas

basados en un microprocesador (pp) han sido usados desde 1980. Por un tiempo,

emuladores in-circuit 108 cuales accesaban la tarjeta vía la base del pp, fueron usados

en el ambiente de prueba de tarjetas, pero resultaron difíciles de manejar y de usar.

El paso evolucionario que diferenciaba la emulación de CPU de emuladores

in-circuit fue el desarrollo de tarjetas adaptadoms (adapters pods) para un microprocesador, las cuales consisten en un sistema mínimo basado en el ,up a emular

y circuiteda d e control, de tal forma que la tarjeta adaptadom sirve como interfaz

entre un controlador de pruebas y el SBP (figura 1.6).

La emulación de CPU es casi transparente (se refiere al hecho de que para

el SBP no existe diferencia entre el pp y el emulador), aunque existen diferencias

eléctricas en la capacidad de manejo de señales de acuerdo a los tipos de dispositivos que reciben las señales del emulador. El Pod CPU utiliza el reloj del SBP,

prohando el sistema a través de circuitos de conmutación especiales que conectan y

desconectan el SBP del emulador.

CAPITULO 1 . PANORAMA GENERAL DE LOS EQUIPOS DE PRUEBA. 13

f

\

EMULADOR

DE

MEMORIA

L

J

Figura 1.6: Emulación de CPU. El pp del SBP es físicamente removido y reemplazado con una conexión a una interfaz que contiene el pp equivalente. Permitiendo

que las operaciones sean totalmente controladas.

4CO

La emulación de CPU proporciona la habilidad de verificar el SBP desde adentro, lo cual permite observar y controlar totalmente el sistema. La otra ventaja de

este método es la habilidad para probar sietemas que no funcionan debido a fallas

en el flujo de direcciones-datos entre la memoria y el pp.

M

b

P

Gn

Las principales desventajas de la emulación de CPU Eon: se requiere un emulador diferente para cada microprocesador, los nuevos pp son muy difíciles de emular

debido a su complejidad y otra desventaja puede ser la velocidad del procesador;

"velocidades cercanas a los 25 Mhz exigen que las interconexiones entre el emulador

y el SBP deban ser de una alta calidad, para eliminar la posibilidad de problemas

de ruido eléctrico por alta frecuencia.

2

1.4.1.2

Emulación de ROM.

En su más simple forma un emulador de ROM es un pequeno circuito con una

RAM, algunos circuitos integrados de soporte y dos conectores. U n conector serie

o paralelo va a una PC o controlador y el otro conector se inserta en la Lase de

la ROM a emular del sistema digital. Las instrucciones son enviadas por la PC y

almacenadas en la RAM del emulador, estas instrucciones aparecerán en el área de

memoria del sistema digital como si la ROM estuviera presente. Los datos en la

memoria son las rutinas de prueba (figura 1.7). Cuando el microprocesador del SBP

inicia su rutina de inicialización en su lugar encuentra las pruebas a ejecutar.

0

U

4

s

e

- u

$ 0

z u =

nul

U

A

CAPITULO 1. PANORAMA GENERAL DE LOS EQUIPOS DE PRUEBA.

r

7

CONTROLADOR

r

EMULADOR

DEL

MICROPROCESADOR

Figura 1.7: Emulación de memoria. El p p del

7

I1

14

I

SBP es mantenido en su lugar, pero

las instrucciones de prueba se originan en una interfaz emuladora de ROM.

Una de las principales ventajas de la emulación de ROM es una mayor sencillez

y generalidad del hardware, el cual es fácilmente conectado al procesador y mucho

menos caro que una interfu de CPU; además, puede ser utilizado para una gran

variedad de tipos de pp. Durante la prueba el p p corre a su máxima velocidad mientras ejecuta el código. La más grande desventaja de esta técnica es su aislamiento

de fallas. Ya que el diagnóstico se origina en memoria, la visibilidad suministrada

por un acceso directo al pp se pierde. Si la emulación de ROM es el único método

de prueba y el pp está daiíado (o el sistema mínimo), la prueba falla desde el inicio.

Esta técnica también tiene dificultades cuando la ROM es interna al pp, como en el

"caso de varios microcontroladores. Efts técnica requiere una experiencia considerable en programación, y a que los emuladorea son programados generalmente en C,

UNIX o ensamblador.

1.4.1.3

Emulación basada en' bus.

Con esta técnica el emulador llega a ser el maestro del bus, accesandolo y controlándolo para iniciar la prueba, lo anterior lo realiza a través de interrupciones al

pp (figura 1.8)

Dentro de este tipo de emulación existe lo que se llama emulación de DMA,

en la cual el emulador se comporta como un controlador de DMA, robando ciclos al

procesador para realizar pruebas de lectura y escritura.

Las mismas características asociadas con la técnica de emulación de ROM están

CAPITULO 1. PANORAMA GENERAL DE LOS EQUiPOS DE PRUEBA.

DECOD DE DIR

15

TECLADO

MODEM

VIDEO

DIRECCIONES

Figura 1.8: Emulación basada en bus. Las funciones del sistema son probadas a

través del bus .

presentes en la emulación basada en bus. La principal diferencia es que la emulación

basada en bus es más fácil de implementar y menos costosa que ésta. A diferencia

de la emulación de CPU, la emulación basada en bus no requiere circuitería de

conmutación de bus muy complicada. La más grande ventaja de ésta técnica es

su capacidad de probar sistemas aún con el pp dañado. La principal desventaja

ea su velocidad de prueba y capacidad. Mientras que el pp corre a su máxima

kelocidad, las pruebas con esta técnica son efectuadas a una velocidad mucho mas

baja. Además no se tiene acceso a los registros de CPU y no hay posibilidad de

programación. Otra desventaja ocurre si el sistema no tiene capacidad para DMA.

Capítulo 2

Planteamiento del proyecto.

Como se mencionó al inicio de este trabajo, la tarjeta interfaz se instalará en una ranura de expansión de un PC y actuará como controladora de la prueba, sin embargo,

para que funcione como tal, existen varias consideraciones que se deben tomar en

cuenta, las cuales se mencionan en la siguiente sección.

2.1 La computadora personal como estaciáln de

trabajo.

Sin duda alguna la principal característica debido a la cual la PC esta invadiendo el

campo de los equipos de diagnóstico es su bus de expansión. Este permite que sea

adaptada a un requerimiento individual y que se hagan mejoras conforme avanza la

tecnología evitando la rápida obsolescencia; por lo anterior la PC ha llegado a ser

el cerebro de las estaciones de trabajo que interactúan con el medio ambiente.

Las estaciones de trabajo basadas en PC pueden ser consideradas como 5 partes

fundamentales[6]:

1. Prueba o experimentación.- Este es el medio ambiente externo' a la PC a ser

monitoreado y10 controlado.

'Cualquier sistema que se encuentra físicamente afuera de la PC.

16

CAPíTVLO 2. PLANTEAMIENTO DEL PROYECTO.

17

2. La interfaz.- Esta es la circuitería que convierte la señal analógica a un valor

digital y lo transfiere a la PC.

3. La PC.- Como cerebro de I s estación de trabajo es responsable de monitorear,

controlar, analizar y desplegar la información de la prueba o experimento.

4. Almacenamiento.-

Es el área donde los resultados de las pruebas son almace-

nados (discos flexibles y duros, cinta, etc.)

5. Impresoras.- Crean copias de resultados, tablas de datos y gráficas.

Dado su bajo costo y las caractexísticas mencionadas anteriormente, la PC está

encontrando un camino hacia los equipos de diagnóstico de fallas. Para que una PC

funcione como un equipo de éstos requiere una interfaz hardware y el apropiado

software para manejarla, además debe ser capaz de procesar los resultados de las

pruebas.

Para utilizar la PC como controlador de pruebas (utilizando el bus de expansión) se tienen dos opciones para realizar las transferencias de datos: a través

de acceso directo a memoria y por microprocesador. Para el diseño de este sistema

se optó por realizar transferencias utilizando el microprocesador por los siguiente:

Las transferencias utilizando el microprocesador requieren menos soporte de

hardware y software. Ya que el p p es un dispositivo inteligente su interfaz

puede no serlo tanto, lo anterior no ocurre con el DMA, el cual exige que su

operación sea programada al menos una vez.

o Los

lenguajes de alto nivel tienen implementadas instrucciones para enviar y

recibir datos del bus utilizando el pp, sin embargo para manejar transferencias

de DMA es necesario diseñar y ejecutar rutinas especiales.

o

En el diseño de la tarjeta no se implementan transferencias de bloques de

datos, por lo tanto un acceso por DMA podría no ser la solución óptima.

o

No se utiliza ningún canal de DMA y pueden ser utilizados por otra aplicacióii

que maneja la velocidad como factor crítico.

Es más sencillo implementar transferencias por microprocesador.

Desde el inicio del proyecto se trabajo con la idea diseiiar con los componrntes

que se tenían y de ahorrar espacio en la construcción de la tarjeta, como se

mencionó anteriormente las transferencias por pp requieren menos hardware.

r<

CAPITULO 2. PLANTEAMIENTO DEL PROYECTO.

2.2

18

Técnica de prueba empleada.

Escoger una técnica de prueba por emulación depende de un número de factores

globales induyendo costo, estrategias de prueba, necesidades y tipos de producto

a probar. Los expertos están de acuerdo en que la emulación de CPU ea un poco

más atractiva que las otras dos debido a su c a t r u l y obsemubilidud, a pesar del

inconveniente de utilizar un emulador para cada pp.

El sistema desarrollado utiliza la técnica de emulación de CPU por las siguientes

razones:

Bajo esta técnica se tiene un control sobre el emulador y por consiguiente sobre

todo el sistema, esto es, se pueden enviar órdenes a los dispositivos de soporte

y a los externos y observar su comportamiento; se tiene una observabiíidad

del sistema por el hecho de que todos los dispositivos pueden se manejados y

monitoreados por el pp. No hay que olvidar que una PC tiene en su tarjeta

base un controlador de teclado, interrupciones, video, disco, DMA que en un

momento dado se requieren probar.

No se requieren puntos de contacto especiales entre el sistema de pruebas y el

circuito a probar, ya que la comunicación se realiza a través de la base del pp.

Lo anterior facilita un poco el diseño de la tarjeta.

Como se mencionó en el capítulo anterior la emulación de memoria y la basada

en bus no tienen todo el control necesario para probar tarjetas inteligentes. Si

falla el bus de datos o el de direcciones las técnicas anteriores no pueden

detectarlo.

rn

Existe más variedad de pruebas a realizarse emulando al CPU que las otras,

por ejemplo, probar el bu5, análisis de firma, aplicar pulsos de voltaje.

o

Aunque el costo de utilizar una técnica u otra podría ser similar, éste no fué

un factor determinante en la elección de la misma, cada una de ellas con su

grado de complejidad.

o Por último, se deseaba estudiar la emulación de CPU y su posibilidad de

implementarla.

CAPITULO 2. PLANTEAMIENTO DEL PROYECTO.

2.3

19

Características del sistema.

A continuación se enumeran las principales características que debe tener el software

del sistema.

Deberá manejarse a base de menúes.

Debe tener una opción de ayuda.

Capacidad para almacenar las señales provenientes de la tarjeta, manejarlas y

desplegarlas al usuario.

Desplegar los errores encontrados en el SBP o en la misma tarjeta interfaz.

Detectar errores en los datos introducidos por el usuario.

El lenguaje de programació elegido fué el lenguaje C, aunque se pudo haber

seleccionado otro debido a que actualmente io que Be ejecuta en un lenguaje puede ser

transportado a otro, cuidando ciertas reglas asociadas a él. Una característica que

influyó un poco para elegir al C fué su robustez en el manejo de tipos de datos(22j.

A continuación se enumeran las principales características que debe tener el

hardware del sistema.

=.

Capacidad de autoprueba. Si llegara a detectar un error interno enviar el

reporte a la PC.

Emular y ejecutar la orden proveniente de la PC en tiempo real.

Debe tener inclu'da una punta de prueba para adquirir o aplicar pulsos al SBP.

Puesto que se instalará en el bus de expansión de la PC debe comprender el

protocolo utilizado.

Capacidad para detectar fallas de voltaje en el SBP.

Puesto que la tarjeta se instalará en una PC, el voltaje necesario para su

funcionamiento es suministrado por la misma; la temporización de la tarjeta, esto

i

CAPiTULO 2. PLANTEAMIENTO DEL PROYECTO.

RANURA DE

EXPANSION

20

RO M

El&)< TARJETA

INTERFAZ

B

/---7

3-

RAM

' f

\

PUNTA

DE PRUEBA

U

SISTEMA BAJO PRUEBA

(SBP)

Figura 2.1: Esquema del EP y la forma de conectarse al SBP.

es, la señal de reloj que utilizará será la del SBP, de esta forma se sincroniza a 61

logrando una ejecución de las instrucciones en tiempo real.

Una vez que se definió el proyecto se procedió a planear el sistema, constando

éste, en forma general, de los elementos que se enlistan a continuación (figura 2.1):

1. Una tarjeta interfa', que se inserta en una ranura de expansión de una computadora personal compatible con IBM.

2. Un programa ejecutándose en la computadora, para enviar Órdenes a la tarjeta;

según la orden, ésta ilevará a cabo tina acción sobre el circuito a probar,

constituyendo además, en la interfaz hombre/máquina.

3. Una punta de prueba, para detectar estados lógicos y apljcar puleos al circuito

digital, la cual será controlada por el usuario.

La razón de haber elegido el tener como base del sistema una PC y no otro

equipo, independientemente de las razones ya mencionadas, está el gran mercado

existente alrededor de ella. Normalmente los usuarios buscan en un equipo o sistema independientemente de poder computacional una posibilidad de crecimiento y

compatibilidad.

Ien adelante se usará indistintamente tarjeta iníerfas y tarjeta emuladora

,

CAPíTULO 2. PLANTEAMIENTO DEL PROYECTO.

23

'

El principio básico de operación es el siguiente: La tarjeta interfaz estará instalada en una ranura de expansión de la PC y conectada al SBP según se muestra eii la

figura 2.1, el usuario ejecuta un programa en la computadora y aparecerá un menú

indicando los tipos de prueba disponibles. Este menú principal puede dividirse a

su vez, hasta obtener la opción de una prueba en particular a ejecutar, si se lleva a

cabo la prueba puede encontrarse o no un error; en ambas situaciones el programa

debe indicarlo, quedando al usuario la responsabilidad de tomar una decisión dependiendo del resultado de la prueba. Si se llegara a detectar un error en el nivel

de voltaje del SBP se debe desplegar también un letrero indicando la anomalía.

Dada la arquitectura del sistema propuesto, las partes que constituyen el sistema no tienen la capacidad de funcionar independientemente, incluso el programa

que se ejecuta en la PC debe detectar si la tarjeta interfaz se encuentra instalada.

En los siguientes capítulos se describe en detalle el diseño de cada uno de los

elementos anteriores.

__ . .

Capitulo 3

Descripción de la interfaz.

Este capítulo presenta la descripción de la tarjeta interfaz, sus partes principales,

su diseño y funcionamiento.

3.1

Descripción a bloques de la tarjeta interfaz.

La tarjeta interfaz tiene la función de sustituir al microprocesador del SBP y proveer

la interfaz para ser instalada en una ranura de expansión de una PC IBM o cornpatible (utilizando el bus de 8 bits). Está constituida por 6 secciones l

a cuales

se describen a continuación, al final del capítulo Be encuentran los diagrama de

conexión para cada sección:

1. SECCION PROCESADORA: Integrada por un sistema mínimo basado en

el rnicroprocesador 8086 de Intel. Considerado el “corazóu” de la tarjeta e-

muladora; recibe órdenes de la computadora personal a través de la sección

inferfoz con la PC, ejecuta la rutina correspondiente, almacena resultados de

las pruebas y lleva a cabo una autoprueba de la tarjeta.

2. SECCION DE CONTROL Y TEMPORIZACION: Controla los contenedores

(buffers) y drivers de la sección ¿e interfaz y también la conmutación entre

esta sección y la procesadom. Genera además, las señales “falsas”’ que sou

‘mas adelante se describen est& señales

22

C A P ~ T U L O3. D E S C R I P C I ~ ND E L A I N T E R F A Z .

23

Figura 3.1: Diagrama a bloques de la tarjeta interfaz.

necesarias para que el SBP "no vea" la ausencia del microprocesador.

3. SECCION DE INTERFAZ: Formada por loa buffers y drivers necesarios para

hacer la conexión entre el sistema bajo prueba y la tarjeta. Un detector de

falla de voltaje esta integrado en esta sección; el detector monitorea el voltaje

del SBP, indicando si existe alguna disminución o elevación del mismo.

4. DETECTOR DE NIVEL LOGICO: Recibe e interpreta los niveles lógicos que

son obtenidos a través de la punta de prueba.

5. GENERADOR DE FIRMA: Este bloque genera un dato en formato hexadeci-

mal para un determinado punto del sistema bajo prueba, utilizando la técnica

de análisis de firma.

6. INTERFAZ CON LA PC: Constituída por 105 puertos de entrada y salida

de la tarjeta emuladora, necesarios para transferir información a la PC y/o

viceversa.

i

CAP~TULO3. D E S C R I P C I ~ NW E L A I N T ERF A Z .

24

DIRECCIONES/DATOS

Figura 3.2: Seccion procesadora.

3.2

3.2.1

Descripción detallada de cada bloque.

Sección procesadora.

El microprocesador ( V i ) , RAM’S (U4,U5) y ROM’s (U2 y U3) constituyen un sis-

tema mínimo (figura 3.2), donde reside todo el control de la tarjeta interfaz (diagrama l). Debido a que el microprocesador 8086 tiene un bus de datos y direcciones

multiplexado se utilizan candados (U8,U9) para mantener una dirección válida. El

lado de datos de la memoria RAM y ROM están conectados directamente al microprocesador para evitar retardos. La entrada y salida de datos de el sistema mínimo

se hace a través de buffers (U6 y U7), principalmente para reducir la carga en las

líneas del microprocesador.

La circuiten’a de decodificación de dirección (U10, V i l ) es la que indica qué

c.i. se habilita para poner datos en el bus. La señal SBP controla estos r.i. de

.

..* _ _ _

CAP I TULO 3. DESCRIPCidN DE LA ZNTERFAZ.

25

td forma que cada vez que se accese al sistema bajo prueba, el sistema mínimo es

deshabilitado. Lo anterior se realiza para que no exista una contención entre los

componentes de la tarjeta interfaz y los del SBP, lo que podría provocar resultados

desastrosos en ambos sistemas.

Este sistema mfnimo tiene instalado dos memorias RAM de 2048 palabras por

8 bits, produciendo entre las dos una memoria de 4 kbytes, cuyo número de catálogo

es HM6116LP-4.

La memoria ROM esta formada por dos c.i. 2732-A los cuaies tienen un tiempo

de acceso de 200 ns; lo que resulta suficiente para que el microprocesador pueda

accesarla. Cada uno de los c.i. es de 4 kbytes por 8 bits, dando en total 8 kbytea

de memoria ROM.

3.2.1.1

Direccionamiento.

Esta sección presenta las direcciones internas de la tarjeta interíaz así como las

necesarias para establecer el protocolo con la PC

La tarjeta interfaz tiene el mapa de direcciones que ae muestra en la tabla 3.1.

Como se observa, tiene puertos de entrada y salida integrados, mismos que son

.accesados en la misma forma que las localidades de memoria.

La tabla 3.2 muestra la dirección asignada a cada uno de los puertos de entrada

y salida de la tarjeta.

Las direcciones anteriores, según el mapa de la PC compatible, no están asig-

nadas a otro dispositivo.

3.2.2

Sección de control y temporización.

Esta sección genera las señales necesarias para conmutar los drivers de la tarjeta

emuladora hacia el SBP y las señales falsas, además, detecta el modo en el cual el

microprocesador 8086 del SBP está trabajando (figura 3.3).

El c.i. U17 (diagrama 2) produce las señales IALE e

m,utilizadas para

-

. .

...

CAPITULO 3. D E S C R I P C I ~ NDE LA INTERFAZ.

26

HEX

OFFF

1111

0001

RAM

RAM

O000

1000

1001

1010

1011

1100

1101

1110

1111

O000

1111

~~

Descripción

1800

1900

IAOO

lBOO

1

coo

lDOO

iEOO

lFOO

EO00

FFFF

-

No asignado

Puntade prueba

Estado

ES

Pto. de entrada

Pto. de salida

Tiempo

ROM

ROM

Tabla 3.1: Mapa de direcciones de la tarjeta emuladora.

Puerto

Entrada a la tarjeta

Salida de la tarjeta

Salida de la tarjeta

Salida de la tarjeta

I Dirección 1 Función

1

3ECH

3ECH

3EDH

3EEH

FF

-1

I Comunicación de la PC

con la tarjeta

Acceso de la PC

ai contador de eventos

Acceso de la PC al

generador de firma

CAPíTULO 3. DESCRIPCIÓN DE LA INTERFAZ.

I l l

A1 RELOJ

-

MULTI-

: PLEXOR

--

-

I

I l l

IICL auao

BUS DE DATOS

DE LA SECC.

c /I

-

27

BUFFER

CONTADOR

t

INTA ALE

*

4

+

LOGlCA

COMBINACIONAL

MGICA

SECUENCIA1

ERFAZ

CONTROL

DEL S B P

SENALB

FAEAS

A LA SECC. DE

INTERFAZ

Figura 3.3: Sección de control y temporización.

CAPITULO 3. D E S C R I P C I ~ ND E L A INTERFAZ.

28

el funcionamiento interno de la tarjeta emuladora; su temponzación es idéntica a

las producidas por el 8086; esto es por lo siguiente: El 8086 puede funcionar en

dos modos distintos, modo máximo y modo mínimo. En el modo mínimo el 8086

produce directamente las señales para controlar los dispositivos periféricos. Sin

embargo, en el modo máximo necesita otro c.i. (8288) para generar las señales de

control. La tarjeta emuladora no tiene incluída un 8288, y si se tiene un SBP cuyo

8086 trabaja en modo máximo la tarjeta no podría trabajar correctamente (debido

a que el microprocesador de la tarjeta emuladora debe funcionar en el modo en que

se encuentra el SBP). Debido

a lo anterior se tienen dos flip-flops cuya función es

__

generar las señales IALE e INTA, cuando el pp se encuentre en modo máximo. Las

señales IALE e

son utilizadas Únicamente por la tarjeta. Esta sección cuenta

con un buffer (U19) y una lógica cornbinacional cuya función es producir y forzar

algunas líneas de control del microprocesador a uno o a cero, según sea programado

por el usuario. El contador ascendente/descendente (UZO) y un flip flop (U26)

producen la señal SBP, que marca el inicio de un acceso al SBP. Un arreglo de flip

- flops (U26, U27 y U12) producen las seniles FDEN y FRD (la temporización es

similar a las que produce el 8086). FRD marca el fin de un acceso al SBP. Las

señales que tienen una letra F al inicio de su nombre son utilizadas para realizar las

lecturas falsas y las señales que tiene una letra I al inicio son utilizadas internamente

por la tarjeta.

-

-3.2.3

Sección de interfas.

Esta sección comunica al SBP y a la tarjeta emuladora (figura 3.4).

Las señales de habilitar g dirección de los buffers y tranareceptores (U44, U45,

U46 y U47 ) son generadas por la lógica de control la que a su vez recibe entradas

de la sección de temporización y control (diagrama 3).

Los transreceptores de dirección-datos (U44, U46) son habilitados cuando la

sección procesadora se comunica con el SBP. Los drivers de dirección falsa (U45 y

U47 ) son habilitados durante las lecturas falsas, exactamente en la porción en la

cual es necesario tener en el bus de direcciones FFFFOH.

El c.i. U48 selecciona las señales de control (RD, LOCK, SO, S1) según se

realice un acceso al SBP o una lectura falsa; éste c.i. también es controlado por la

sección de control y temporizacaón.

CAP I TULO 3. DESCRIPCIÓN DE LA INTERFAZ.

29

Figura 3.4: Sección de interfaz.

Esta sección cuenta además con candados de control, que sirven para monitorear las señales de control más importantes de la tarjeta emuladora cuando realice

un acceso al SBP. El usuario puede desplegar en pantalla el estado de las señales y

tomar alguna decisión.

El circuito de detección de falla de voltaje (diagrama 4) monitorea el voltaje

de alimentación del SBP,los niveles permitidos deben estar entre 4.5 y 5.5 V. La

PC puede monitorear la salida del circuito a través del bit D6 del puerto 3EEH, si

detecta un nivel alto despliega un mensaje de falla de voltaje del SBP, y al mismo

tiempo se deshabilita la sección de interfaz, ésto se hace con el fin de proteger al

SBP,ya que las señales de control, dirección y datos lo pueden dañar.

Si se reestablece el voltaje, la sección de interfaz vuelve a activarse, iniciando

el proceso normalmente.

CAPiTULO 3. DESCRIPCIÓN DE LA INTERFAZ.

3.2.4

30

Detector de nivel iógico

Esta sección (figura 3.5) de la tarjeta emuladora tiene las siguientes funciones:

1. Detectsr el nivel lógico (alto, bajo) presente en la punta de prueba.

2. Detectar estados inválidos comprendidos entre 0.8 y 2.4 V.

3. Suministrar pulsos sincronizados a través de la punta de prueba.

El c.i. U56,(amplificador operacional doble) forma junto con un arreglo de re-

sistencias un detector de nivel lógico (diagrama 5); para esta aplicación se considera

un estado cero aquellos niveles de voltaje que estén por debajo de 0.81 V y un estado

uno los niveles de voltaje arriba de 2.2 V. El c.i. U55 son flip-flops cuya función es

capturar el estado lógico. El c.i. U54 es un multiplexor para seleccionar si se desea

aplicar pulsos sincronizados con el funcionamiento de la tarjeta al SBP. Se tiene

un temporieador U53, funcionando a una frecuencia de 180 khz (con una duración

del pulso alto de 1.8 as.), aunque es factible alterarla cambiando el valor de sus

componentes; este temporizador proporciona una base de tiempo para suministrar

pulsos no sincronieados a la tarjeta emuladora.

3.2.5

Generador de firma.

El circuito generador de firma (figura 3.6) como ya se mencionó es un circuito cuya

función es comprimir un flujo de datos (presentes en un nodo del SBP) en una firma

hexadecimal (2 digitos). La entrada al generador es la señal DATOS que viene del

bloque detector de nivel lógico, de tal forma que cualquier cambio de nivel en esta

línea producirá una variación en la salida del registro de corrimiento (U41),siempre

y cuando se active la señal SINC,la cual se sincroniea al funcionamiento del SBP.

Se tiene además una retroalimentación (U43) (diagrama 6 ) a base de compuertas

XOR que ayuda a que la firma sea más significativa para un punto dado.

Este bloque cuenta además con un contador de eventos (U42)cuya función

es contar los cambios de nivel que ocurren en la línea DATOS, por lo tanto, para

un nodo cualquiera, aparte de obtener su firma (compresión de datos), se lleva a

31

C A P ~ T U L O3. D E S C R I P C I ~ ND E L A INTERFAZ.

DATOS

WNr

h

LUZ

MULTI-

PLEXOR

----U hW

HABILITAR

CONTROL

Figura 3.5: Detector de nivel lógico.

H AB1LITAR-7

--BUFFER

+REGISTRO

DE

FIRMA

4

HABILITAR

CONTABUFFER

EVENTOS

Figura 3.6: Generador de firma.

VERDE

CAP I TULO 3. DESCRIPClÓN DE L A INTERFAZ.

32

Figura 3.7: Interfaz con la PC.

cabo un conteo de eventos, lo anterior se realiza por si llegara a suceder que un

determinado nodo tuviera una firma semejante a otro.

La PC puede accesar tanto la firma como la cuenta a través de dos buffers

(U39 y U40) en forma independiente a la tarjeta emuladora. Estos dos buffers son

habilitados a través de una dirección asignada previamente.

3.2.6

Interfae con la PC.

Este bloque es el encargado de decodificar la dirección que está presente en el bus

de direcciones de la computadora y activar los correspondientes puertos de entrada

y salida de la tarjeta emuladora (figura 3.7).

Dentro de esta sección se encuentran dos flip-flops cuya función es establecer

el protocolo de comunicación entre la tarjeta y el SBP. El protocolo funciona de la

siguiente forma:

En el momento en que la computadora envíe un dato a la tarjeta emuladora,

ésta activará el F F i (su salida cambia

a

un nivel alto), la tarjeta emuladora rnoti-

CAPíTULO 3. DESCRIPCIÓN DE LA INTERFAZ.

ENVIO DATO

LA PC

DE LA PC A LA TARJETA

33

LA TARJETA

LEYO EL

FFl

RECONOCIMIENTO

DATO RECIBIDO

FF2

DE LA TARJETA A LA PC

LA PC

LEYO EL DATO

FE

RECONOCIMIENTO

DATO RECIBIDO

iJM

DENTlFlCA

pc

EL

RECONOCJMIEN’D

FFI

LA TARJETA

IDENTIFICA EL

RECONOCIMIENTO

Figura 3.8: Protocolo de comunicación entre la PC y la tarjeta interfaz.

itorea esta señal por medio de un lazo; en el instante en que detecte el nivel alto,

va a una eutina cuya función es leer el puerto de entrada de la tarjeta. Al leer el

puerto limpia el FF1 (su salida va a nivel bajo) y comunica a la PC que ha recibido

el dato; la forma de hacerlo es realizando un acceso al puerto de salida (lEOOH),

lo anterior produce que el FF2 envie su salida a un nivel alto. La PC identifica

este reconocimiento a través del bit D7 del puerto 3EEH. La figura 3.8 muestra un

diagrama del protocolo utilizado.

El protocolo anterior tiene principalmente dos ventajas:

1. N o se requieren retardos en el software utilizando.

2. Se evitan lecturas indeseables, es decir, el hecho de leer un dato dos o más

veces, ya que todas las transferencias son controladas por los flip-flops.

CAPíTULO 3. DESCRZPCIÓN DE LA INTERFAZ.

3.3

34

Teoría de funcionamiento.

Como se mencionó anteriormente la tarjeta emuladora es, en sí, un sistema controlado por un microprocesador. Cuando no está en comunicación ni con la computadora personal, ni con el sistema bajo prueba, se encuentra en un ciclo, el cual

consiste en una lectura a la dirección lBOOH en donde el bit D7 (salida del FFl)

indica si la computadora ha enviado un dato.

Al mismo tiempo del ciclo y en cualquier instante en el cual la tarjeta emuladora

no esté en comunicación con el SBP se estarán realizando lecturas falsas, la cual es

una operación de lectura que la tarjeta emuladora hace en la localidad FFFFOH

del sistema bajo prueba, llevada a cabo por las señales falsas que se prodücen en

la sección de control y temporización. Estas operaciones son necesarias ya que el

SBP necesita algunas señales para que a sus componentes les sea transparente el

funcionamiento de la tarjeta; en base a lo apterior se concluye que la tarjeta realiza

dos tareas al mismo tiempo: el ciclo para sensar la transmisión de datos y las lecturas

falsas.

Cuando la tarjeta interfaz detecta que la PC le ha enviado un dato suspende el

ciclo y lee el dato del puerto de entrada (dirección 1DOOH); el primer byte ai inicio

de toda transmisión puede indicar dos situaciones: si la orden puede ser ejecutada

sin necesidad de otra transmisión (por ejemplo: Obtener el estado de las líneas de

control, suministrar un pulso alto, etc) o si la orden necesita más transmisiones (por

ejemplo: leer localidad, escribir una localidad, etc.). En la primer situación el byte

se obtiene y se ejecuta la orden dependiendo de su valor, en la segunda situación

este byte le indica a la tarjeta la cantidad de bytes que serán enviados por la PC,

siendo esta la forma en que interfaz conoce cuantas lecturas debe realizar al puerto

de entrada antes de ejecutar la orden en el SBP.

Todos los datos que van llegatido de la PC son almacenados en una área de

memoria especial. Cuando el emulador se disponga a ejecutar el comando en el

SBP tiene que sacar los datos de esta área. El primer dato que va a sacar es el

correspondiente al número de transmisiones que se llevaron a cabo (entre la tarjeta

y la PC) y lo almacena en un c.i. contador (UZO,véase el diagrama 2) y en el

momento en que empiece a sacar los siguientes datos, este contador decrementa

su cuenta en 1 por cada dato; cuando ha accesado toda la memoria, produce un

pulso (borrow), que activa un flip flop y éste a su vez produce la señal SBI’, que

desactiva los componentes de la tarjeta interfaz y redirecciona los buffers hacia CBP.

CA PIT ULO 3. D E S C R I P C I ~ NDE L A INTERFAZ.

35

De tal forma que la instrucción se ejecuta en el SBP. Los buffers permanecen activos

todo

-el tiempo que dure el ciclo de la instrucción, este ciclo termina con la señai

FRD, desactivando los buffers y entrando en funcionamiento el sistema mínimo de la

tarjeta. Este sistema captura el resultado de la operación (si ea esperado) y lo envía

inmediatamente a la PC, para después entrar al lazo y sensar si llega otra orden

de la PC. El ciclo anterior se repite para cada operación que la tarjeta emuladora

realice en el SBP.

!

s

.

m

I

1

CAP I TULO 3. DESCRIPCIÓN DE LA INTERFAZ.

t 5v.

R1 330

t 5v.

39

a

R2 220a

R3 330c2-t 260n

R4 POT 10Kc2

R5 3.3Kn

R6 3.3Kc2

-

salida

9

Diagrama 4. Detector de falla de voltaje.

BIB DE DATOS

Diagrama 5. Detector de nivel lógico.

CAPíTULO 3. DESCRIPCIÓN DE LA INTERFAZ.

c

Diagrama 6. Generador de firma.

40

Capítulo 4

Software de la tarjeta interfaz.

Este capítulo presenta el software que controla la tarjeta in¿Lrfaz y se divide en dos

secciones:

1. La interfaz con el usuario (programa ejecutándose en la computadora personal).

2. Un programa monitor, almacenado en la memoria ROM de la tarjeta.

En las siguientes secciones se describen cada uno de ellos.

4.1

Interfaz con el usuario.

La figure 4.1 muestra el diagrama de flujo de las funciones que realiza la interfaz

con el usuario, siendo las más importantes:

1. Desplegar las funciones del sistema a base de menúes, presentando de ésta

forma un ambiente agradable al usuario.

2. Ejecutar el protocolo PC-tarjeta, transfiriendo y/o recibiendo los datos y comandos a través del bus de expansión de 8 bits de la PC.

CAPITULO 4. SOFTWARE DE LA TARJETA INTERFAZ.

42

3. Procesar los datos que son enviados por la tarjeta y si es necesario desplegarlos

en pantalla.

El programa consiste de varios módulos (figura 4.2), cada uno de ellos corresponde al tipo de prueba que se va efectuar sobre el SBP. En las siguientes secciones

se presenta su descripción.

4.1.1

Pruebas de memoria RAM.

FUNCIONES RAM.- En esta opción se encuentran las funciones que efectúan pruebas a la memoria RAM del SBP. Básicamente se cuenta con dos tipos de prueba,

ambas se complementan, esto es, algunos errores pueden ser detectados por la prueha

2 pero no por la prueba 1 y viceversa.

P r u e b a 1.- Esta prueba está constituída por dos pasos los cuales se enumeran

a continuación.

El primero consiste en inicializar la dirección O y las direcciones primarias

(Le. 1,2,4,6,16 ...) a un valor de O. La prueba de condición a i'(stuck 1) es

realizada leyendo esos ceros. Para probar la condición a O' (stuck O), un valor

de 1 es escrito en la dirección O y leído. Si la memoria pasa las dos pruebas

anteriores, se asegura que las líneas de datos no se encuentran a O ó 1. También

se demuestra que los controles de la memoria RAM funcionan bien.

El segundo. De la operación anterior las direcciones primariaa contienen ceros.

Esta prueba consiste en leer 108 ceros, después se escriben datoe iguales a

las direcciones primarias, a continuación se lee el dato que se escribió. La

prueba anterior verifica que las líneas de dirección a& como las de datos no se

encuentran a cero o a uno permanentemente. Asegura también que ninguna

línea de dirección o de datos se encuentra en corto circuito. Si el número de

líneas de datos es menor que el número de líneas de dirección se mantiene el

bit de más alto orden y se cambian los menos significativos. Como datos de

entrada recibe la direccióii iiiicial y final de bloque,de memoria a probar.

P r u e b a 2.- Esta prueba detecta interacción entre un bit y otro de cualquier

byte o palabra, entre celdas adyascentes, o algunas líneas de control. Se ha

'Se refiere n1 hecho d e que una linen tiene u n valor permanente de 1 lOgico

'Se refiere al hecho d e que uno Iínen tiene u n valor permanente de O lógico

CAPÍTULO 4. SOFTWARE DE LA TARJETA INTERFA;.

Figura 4.1: Diagrama de flujo del programa Interfaz con el usuario

43

I PRINCIPAL

I

AYUDA

FUNCIONES

RAM

I

FUNCIONES

>

-

ROM

MAPEAR

MEMORIA

,

Inspeccionar RAM

1

LOCALIZAR

FALLAS

PUNTA DE

PRUEBA

Localizar

Suministrar pulso alto sincronizado

Escribir una

localidad

localidad

Figura 4.2: Módulos del programa Interfaz con el usuario.

CONTROL

DE LINEAS

..

I

CAP I TULO 4 . SOFTWARE DE LA TARJETA INTERFAZ.

45

10000000

1o 1o 1o 1o

01010101

11001100

O01 10011

11110000

00001111

11111110

Tabla 4.1: Patrones de prueba utilizados.

demostrado que esta prueba detecta un 97% o más de las faiias anteriores[7].

La prueba empieza inicializando todas las localidades con cero.

Después se accesa cada dirección para leerlos, a continuación se utiliza un

grupo de patrones especiales que se van escribiendo uno por uno en cada

dirección de la memoria. El grupo de patrones se muestra en la tabla 4.1

Como datos de entrada recibe la dirección inicial y final del bloque de memoria

a probar.

Leer una localidad de memoria.- A través de esta opción se puede leer

cualquier dirección de memoria (RAM,ROM o E/S) del SBP. El dato de

entrada es la localidad a leer.

Escribir en una localidad.- Con esta opción se puede almacenar un dato

en cualquier localidad de la memoria RAM o enviar datos hacia un puerto de

E/S. Los datos de entrada son el dato a almacenar y la localidad.

4.1.2

Pruebas a la memoria ROM.

Probar ROM.- Esta opción prueba la memoria ROM del SBP de la siguiente forma: se accesa la primer localidad de la memoria y al dato se le aplica

un XOR con el contenido de la siguiente, al resultado de la operacibn an-

terior se le aplica una vez más el XOR con el contenido de la siguiente y

así sucesivamente hasta completar toda la memoria ROM. De esta forma se

CAPíTULO 4 . SOFTWARE DE L A TARJETA INTERFAZ.

46

51

obtiene una firma característica que se compara con otra previamente almacenada. Si las firmas difieren, el sistema detectará un error desplegando Is

información en pantalla. Esta opción requiere que previamente se obtenga

una firma característica (cuando el SBP se encuentre en buen estadoj para

hacer la comparación final. Como datos de entrada recibe la dirección inicial,

final y la firma característica del bolque de memoria ROM que se va a probar.

4.1.3

Obtener mapa de memoria.

- Obtener mapa.- Si el usuario no conoce el mapa de memoria del SBP,

utilizando esta opción puede obtenerlo. Se pueden detectar las áreas de

memoria RAM,ROM y E y S, en base a las siguientes consideraciones:

1. Una localidad de memoria cuyo contenido puede ser alterado esto es,

escribir y leer el dato, se considera una localidad de memoria RAM.

2. Una localidad cuyo contenido no puede ser alterado esto es, se puede

leer pero no rscribir en ella, se considera una localidad de memoria

ROM (localidades de memoria ROM no usadas contienen FFFFM).

3. Una localidad que tiene bits que pueden ser alterados y otros no se

considera un puerto de E/S.

Como datos de entrada recibe el área total de memoria que se desea

mapear.

- Inspeccionar memoria RAM.- Despliega el inicio y fin de las áreas de

memoria RAM encontradas por la opción Obtener m a p .

- Inspeccionar memoria R0M.- Despliega el inicio y fin de las áreas de

memoria ROM encontradas por la opción Obtener m a p .

- Inspeccionar E/S.- Despliega el inicio y fin de las áreas dedicadas a los

puertos de E/S encontradas por la opción O¿tener >napa.

Las opciones anteriores no requieren datos de entrada.

4.1.4

Localizar Fallas.

- Ejecutar

un programa.- Es posible cargar programas completos en

la memoria del SBP y después ejecutarlos utilizando esta opción. Este