Descarga aquí - Escuela Superior Politécnica de Chimborazo

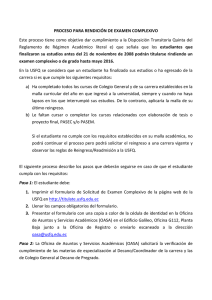

Anuncio

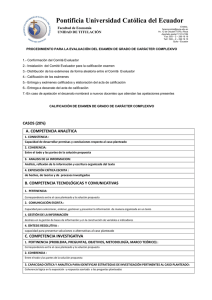

ESCUELA SUPERIOR POLITÉCNICA DE CHIMBORAZO FACULTAD DE INFORMÁTICA Y ELECTRÓNICA ESCUELA DE INGENIERÍA ENELECTRÓNICA ENCONTROL Y REDES INDUSTRIALES GUÍA PARA EL EXAMEN COMPLEXIVO Tecnólogo en Informática Aplicada CONTENIDO 1. 2. 3. 4. 5. 6. 7. 8. 9. 1. PRESENTACIÓN OBJETIVO CARACTERÍSTICAS DEL EXAMEN COMPLEXIVO EVALUACION TEMAS, SUBTEMAS PREGUNTAS Y PONDERACIÓN EJEMPLOS BIBLIOGRAFÍA INSTRUCTIVO PARA EL ESTUDIANTE PRESENTACIÓN Con fecha 09 de Abril del 2014, el Consejo de Educación Superior aprobó reformas al Reglamento de Régimen Académico, de entre las cuales está la Disposición Transitoria Quinta, acápite e) “Los estudiantes que hayan finalizado sus estudios antes del 21 de noviembre de 2008, deberán aprobar un examen Complexivo o de grado articulado al perfil de una carrera o programa vigente o no vigente habilitada para registro de títulos. En caso que la carrera o programa ya no sea ofertada por la IES. El estudiante podrá homologar estudios en una carrera o programa vigente, de conformidad con lo establecido en el presente Reglamento, antes de la realización del correspondiente examen de grado. A partir del 21 de mayo de 2015 estos estudiantes deberán acogerse a la disposición general cuarta del presente Reglamento" La presente guía es un documento institucional, dirigida al estudiante de la Escuela de Ingeniería en Electrónica y Tecnología en Computación de la ESPOCH y que pretende facilitar la comprensión de las particularidades del Examen Complexivo al que puede acceder como alternativa para su de titulación. En tal virtud, la Escuela de Ingeniería Electrónica en Control y Redes Industriales de la ESPOCH tomando como sustento estas disposiciones legales y con la intención de proporcionar un mecanismo de información y orientación del estudiante politécnico, prepara y entrega la presente guía. 2. OBJETIVO Entregar al estudiante de la Escuela de Ingeniería en Electrónica y Tecnología en Computación de la ESPOCH una guía para rendir el Examen Complexivo en el marco de las disposiciones legales implementadas por el Consejo de Educación Superior como alternativa de titulación de estudiantes de tercer nivel. 3. CARACTERÍSTICAS DEL EXAMEN COMPLEXIVO Entre las características del Examen Complexivo que se implementa en la Escuela de Ingeniería en Electrónica y Tecnología en Computación de la ESPOCH se anotan: 4. Es una forma de evaluación total o final que permite valorar los logros o resultados de aprendizaje del futuro profesional, previstos en la planificación curricular de la carrera. Este mecanismo de titulación está contemplado en la estructura curricular de las Escuelas de Ingeniería en Electrónica de la ESPOCH y para el caso de los estudiantes que han concluido la malla curricular antes del 21 de noviembre de 2008 (es decir, haber aprobado hasta el período Marzo – Agosto 2008) es la única opción de titulación prevista en el Reglamento de Régimen Académico. Esta forma de titulación, al igual que los otros mecanismos de titulación en la formación de grado, tiene un nivel de complejidad, tiempo de preparación y demostración de competencias (conocimientos, aptitudes y actitudes) por parte del estudiante, coherentes con las exigencias profesionales. El Examen Complexivo guarda correspondencia con los aprendizajes adquiridos en la carrera y utiliza un nivel de argumentación coherente con los dominios del campo del conocimiento abordados por la profesión. El Examen Complexivo se sustenta en el campo de formación de la praxis profesional. EVALUACION Las preguntas serán de selección múltiple con una sola opción válida. El examen contemplará una duración de 1 hora para la evaluación teórica y de 2 horas para la evaluación práctica, y deberá ser aprobado con una nota mínima de 14,00 puntos sobre 20,00. En caso de que un estudiante no apruebe el primer examen Complexivo, podrá rendir un segundo examen por una sola vez, en fechas que posteriormente se definirán y que serán publicadas en la página web de la institución. 5. TEMAS, SUBTEMAS a. Examen complexivo para optar por el título de Tecnólogo en Informática Aplicada Las asignaturas, temas y subtemas a evaluar son los que a continuación se detallan: ASIGNATURA CIRCUITOS II TEMA UNIDAD 1: CONCEPTOS Y DEFINICIÓN DE CIRCUITOS UNIDAD 2:LEYES EXPERIMENTALES Y CIRCUITOS SIMPLES UNIDAD 3: TÉCNICAS PARA EL ANÁLISIS DE CIRCUITOS. UNIDAD 4: FASORES. UNIDAD 5: POTENCIA PROMEDIO Y VALORES RMS. UNIDAD 6: CIRCUITOS TRIFASICOS. ELECTRONICA ANALOGICA UNIDAD 1 Diodos semiconductores UNIDAD 2 Aplicaciones con Diodos UNIDAD 3 Transistores bipolares de unión UNIDAD 4 Polarización de DC-BJT SUBTEMA 1.1 Tipos de fuentes. 1.2 Elementos de circuitos. 1.3 Corriente, tensión y potencia. 1.4 Signos convencionales. 1.5 Elementos en arreglo serie y en paralelo. 2.1 Ley de Ohm. 2.2 Leyes de Kirchhoff: Ley de tensión. Ley de corriente. 2.3 Circuito de un solo lazo. 2.4 Circuito con un solo par de nodos. 2.5 Combinación de resistencias y de fuentes. 2.6 Divisores de tensión y corriente 3.1 Análisis de malla. 3.2 Análisis de nodos. 3.3Transformacion de fuentes. 3.4 linealidad y superposición. 3.5 Teorema de Thevenin. 3.6 Teorema de Norton. 3.7 Teorema de la máxima transferencia de potencia. 4.1 Características de la Función excitatriz Senoidal. 4.2 Aplicación a circuitos sencillos. 4.3 Función excitatriz compleja. 4.4 El fasor. 4.5 Relaciones fasoriales para R, L y C. 4.6 Impedancia y admitancia. Problemas de aplicación. 4.7 Diagramas fasoriales. 5.1 Potencia instantánea. 5.2 Potencia Promedio. 5.3 Valores eficaces de corriente y tensión. 5.4 Potencia activa y factor de potencia. 5.5 Potencia reactiva, aparente y compleja. 5.6 Mejoramiento del factor de potencia. 6.1 Generación de voltajes Trifásicos. 6.2 Sistemas conectados en Estrella y en Delta. 6.3 Cargas balanceadas. 6.4 uso del vatímetro. 1.1 Materiales tipo P y tipo N 1.2 Recta de carga 1.3 Niveles de resistencia. 2.1 Análisis mediante la recta de carga. 2.2 Configuraciones de diodos. 2.3 Diodo como rectificador. 2.4 Niveles de resistencia. 2.5 Recortadores. 2.6 Recortadores de nivel. 2.7 Diodo zener. 2.8 Circuitos multiplicadores de voltaje. 3.1 Introducción. 3.2 Operación del transistor. 3.3 Regiones: activa, de corte y de saturación. 3.4 Configuraciones del transistor. 3.5 Acción amplificadora del transistor. 4.1 Introducción. 4.2 Punto de operación. 4.3 Circuitos de polarización. 4.4 Operaciones de diseño. UNIDAD 5 Polarización de DC-BJT UNIDAD 6 Polarización del FET UNIDAD 7 Modelaje de transistores DISPOSITIVOS ELECTRONICOS UNIDAD 1 FUENTES DE VOLTAJE UNIDAD 2 DISPOSITIVOS DE 4 CAPAS UNIDAD 3 RETROALIMENTACIÓN UNIDAD 4 AMPLIFICADORES OPERACIONALES UNIDAD 5 CIRCUITOS INTEGRADOS LINEALES ELECTRONICA DIGITAL UNIDAD 1 FLIP - FLOPS 5.1 Introducción 5.2 Construcción y características de los JFET. 5.3 Tipos de MOSFET. 5.4 VMOS. 5.5 CMOS. 6.1 Introducción 6.2 Configuraciones. 6.3 MOSFET. 7.1 Introducción 7,2 Amplificación en el dominio AC. 7.3 Modelaje de los transistores BJT. 7.4 Parámetros: Zi, Zo ,Av, A 1.1 Valor medio 1.2 Valor RMS 1.3 Rectificación De Media Onda 1.4 Rectificador De Onda Completa. 1.5 Rectificación De Onda Completa Red Puente 1.6 Filtros : C / LC / Π 1.7 Reguladores De Voltaje: Zener / Con Transistores 2.1 Diodo Shockley. 2.2 Rectificador controlado de Silicio. 2.2.1 Operación Básica. 2.2.2 Activación / Desactivación 2.2.3 Protección dv/dt di/dt. 2.3 Otros Dispositivos de cuatro capas 2.3.1 DIAC 2.3.2 TRIAC 2.3.3 Reguladores Electrónicos. 3.1 Retroalimentación Negativa 3.1.1 Parámetros Característicos 3.2 Retroalimentación Positiva 3.2.1 Osciladores 3.2.2 Desplazamiento De Fase 3.2.3 Puente De Wien 3.2.4 Colpitts - Hartley - Clapp 3.3 Oscilador De Cristal 4.1 Método De Análisis Lazo Abierto / Lazo Cerrado 4.2 Seguidor Unitario o Seguidor Acoplador De Voltaje 4.3 Comparadores / Detectores de Nivel de Voltaje. 4.4 Amplificador Inversor / No Inversor. 4.5 Amplificador Sumador, Sumador Inversor. 4.6 Restador, Amplificador de Diferencias. 4.7 Diferenciador / Integrador. 5.1 Temporizador 555 5.2 Modos de Funcionamiento astable / monoestable 5.3 Oscilador Controlado por Voltaje ( VCO ). 5.4 Conversión Digital Analógica (Red En Escalera) 5.5 Funcionamiento Del Convertidor D / A. 5.6 Conversión Analógica Digital A / D. 5.7 Técnicas de conversión 1.1 El Latch básico. 1.2 Retardos de propagación. 1.3 Latch asincrónico: S, R, D, T, J-K, maestro – esclavo. 1.4 El multiplexor con Latch. 1.5 Diseño y conversión de Latch. 1.6 El reloj, tipos y tiempos: Tsu, Th. 1.7 Flip Flop D maestros – esclavo. 1.8 Flip flops disparados por flaco: T, J-K, J-K maestro-esclavo. 1.9 Latch vs. Flip flops. 1.10 Registro con Flip Flops. UNIDAD 2 Diseño de FF 2.1 Diseño lógico secuencial. 2.2 Flip-Flops: D, T, J-K. 2.3 Registros con FF. UNIDAD 3 Máquinas secuenciales síncronas 3.1 Diagramas de estado. 3.2 Clases de máquinas A, B, C, D, E. 3.3 Diseño de máquinas secuenciales síncronas mediante máquinas de estado. 3.4 Contadores. 3.5 Registros. UNIDAD 4 Introducción a VHDL 4.1 Generalidades. 4.2 Introducción a Xilinx ISE. 4.3 VHDL, organización y arquitectura. 4.4 Operadores y expresiones. 4.5 Tipos de datos. 4.6 Atributos. 4.7 Declaraciones de constantes, variables y señales. 4.8 Declaración de entidad y arquitectura. UNIDAD 5 Combinacional con VHDL UNIDAD 6 Diseño de controladores digitales mediante ASM y VHDL 5.1 Programación de estructuras básicas mediante declaraciones concurrentes. 5.2 Programación y estructuras básicas mediante declaraciones secuenciales. 6.1 Simbología ASM. 6.2 Diseño de controladores secuenciales síncronos mediantes diagramas ASM. 6.3 Implementación de diagramas ASM mediante VHDL. LENGUAJES DE PROGRAMACION II UNIDAD 1 Introducción al desarrollo de software UNIDAD 2 Fundamentos de la Programación Orientada a Objetos (POO) UNIDAD 3 Entorno de desarrollo integrado de software (IDE) y lenguaje de programación orientada a objetos (LPOO) 1.1 Proceso de desarrollo de software 1.2 Paradigmas de desarrollo de software 1.3 Técnicas de programación 2.1 Conceptos fundamentales y características de POO. 2.2 Clases y objetos 2.3 Atributos y comportamiento 2.4 Abstracción 2.5 Encapsulación 2.6 Herencia 2.7 Polimorfismo 2.8 Relaciones entre clases 2.9 Diagramas de Clases. Graficación en UML 2.10 Ejercicios 3.1 Conceptos y características del IDE. 3.2 Proyectos en consola. 3.3 Proyectos en ambiente visual. 3.4 Variables, operadores y expresiones. Sentencias. 3.5 Estructuras de control. 3.6 Implementación de clases y objetos. 3.7 Arreglos y colecciones. BASE DE DATOS UNIDAD 1. INTRODUCCIÓN A LA TECNOLOGÍA DE ALMACENAMIENTO DE DATOS UNIDAD 2. DISEÑO DE BASE DE DATOS RELACIONALES. 6. DE 2.1 Modelo Conceptual: Entidad Relación Asociaciones entre entidades, Cardinalidad de Asociaciones Claves candidatas y claves primarias, Atributos multivaluados Reglas del Negocio 2.2 Modelo Lógico:Relacional Modelo Lógico Transformación de entidades y relaciones 3.1 Introducción. 3.2 Comandos SQL – DDL (lenguaje de definición de datos). 3.3 Comandos SQL – DML (lenguaje de manipulación de datos). 1.1 Definición y conceptos básicos 1.2 Tipos de redes y topologías 1.3 Arquitectura de Red 1.4 Modelo OSI 1.5 Modelo TCP/IP UNIDAD 2. SQL REDES COMPUTADORES I 3.8 Manejo de errores y excepciones. 3.9 Herencia. Polimorfismo. 3.10 Definición y manejo de componentes. 3.11 Manejo de eventos. 3.12 Gráficos y animación. 3.13 Almacenamiento de Información. 3.14 Tópicos especiales. 3.15 Ejercicios y aplicaciones. 1.1 Definiciones generales: dato, base de datos, sistemas de gestión de base de datos (SGBD). 1.2 Enfoque archivos VS. base de datos. Sistemas de base de datos: definición y componentes, objetivos. UNIDAD 1 INTRODUCCIÓN UNIDAD 2 CAPA FISICA 2.1 Funciones de la capa física 2.2 Características del canal de transmisión. 2.3 Transmisión de Señales 2.4 Medios de Transmisión UNIDAD 3 CAPA DE ENLACE DE DATOS 3.1 Funciones de la capa de enlace 3.2 Entramado 3.3 Control de Flujo 3.4 Control de Errores 3.5 Compartición de Medios UNIDAD 4 REDES DE AREA LOCAL 4.1 Ethernet 4.2 Formatos de la Cabecera 4.3 Tecnologías Ethernet 4.4 Operaciones del Conmutador ESTRUCTURA Y PONDERACIÓN DEL EXAMEN COMPLEXIVO La estructura del Examen Complexivo se basa en dos componentes: a. Prueba de Base Estructurada: con las siguientes características: Tipo de prueba Tipo de preguntas Número de distractores Número de preguntas Objetiva Selección múltiple Cuatro (4) Sesenta (60) Tiempo de duración de la prueba Ponderación Evaluación b. Prueba de base no estructurada: con las siguientes características: Tipo de prueba Tipo de preguntas o problemas Número de preguntas Tiempo de duración de la prueba Ponderación Evaluadores 7. Sesenta (60) minutos Cuarenta por ciento (40%) de la nota final Matriz de resultados No estructurada Libre Tres (3) Ciento Veinte (120) minutos Sesenta por ciento (60%) de la nota final Tribunal del Examen EJEMPLOS Para el caso de las pruebas objetivas se utilizarán preguntas (reactivos), debidamente validados, sobre asignaturas del campo de la praxis profesional, que a manera de ejemplo se muestran a continuación: Pregunta 1. Si se tiene implementada la clase "señales", cuáles serían sus propiedades? A) B) C) D) Tipo, periódicas, frecuencia y periodo Tipo, intensidad, periódicas, aperiódicas, frecuencia y periodo Tipo, intensidad, aperiódicas y periodo ) Intensidad, periódicas, aperiódicas y frecuencia Pregunta 2. Si se tiene implementada la clase "señales" con el método "intensidad", cómo se realiza una instancia de la misma? A) señales analogica = new analogica(); B) señales analogica = new digital(intensidad, 10); C) señales analogica = new señales(); m=analogica.intensidad(a); D) señales m = new señales(); analogica=m.analogica(intensidad); Pregunta 3. La figura representa una transformación de F/F, por tanto, que funciones corresponden al bloque de arreglo combinacional (&): A) B) C) D) Pregunta 4. La figura muestra un registro con F/F, de acuerdo a la clasificación según el tipo de entrada/salida, que tipo es: A) B) C) D) SISO PISO PIPO SIPO Pregunta 5. En un regulador de voltaje con un diodo Zener, alimentados por un voltaje directo Vi; el diodo zener está en estado encendido, si la resistencia de carga RL se desconecta la potencia que disipa el diodo Zener es igual a: A) B) C) D) = ∗( = ∗( = = ) ∗( ) ∗( − − ) ) Pregunta 6. Qué tipo de Ruta Estática en IPV6 se debe usar en el Router de la Empresa para poder enviar tráfico de Red a Internet: A) B) C) D) Ruta Estática Normal Ruta Estática Sumarizada Ruta Estática por Defecto Ruta estática Flotante 8. BIBLIOGRAFÍA Las referencias bibliográficas que se recomiendan son las siguientes: A) Circuitos Hayt Junior William H., Kemmerly Jack E., Durbin Steven M (2012). Análisis de Circuitos en Ingeniería (8° Ed.), McGraw-Hill Educación B) Electrónica Digital Tokheim, R. (2008). Electrónica Digital: principios y aplicaciones (7a ed.). España: McGrawHilI Interamericana. Brown, S., & Vranesic, Z. (2006). Fundamentos de lógica digital con diseño VHDL (2a ed.). España: McGraw-HilI Interamericana. C) Electrónica Analógica y Dispositivos Electrónicos BOYLESTAD, R. (2009) ELECTRONICA: TEORÍA DE CIRCUITOS Y DISPOSITIVOS ELECTRÓNICOS, Prentice Hall, Décima Edición FLOYD, T. (2008) Dispositivos Electrónicos, Pearson Prentice Hall, octava edición. MALONEY, T. J. (2006) Electrónica Industrial Moderna, PEARSON EDUCATION, Quinta Edición D) Lenguajes de Programación Martinez, J. (2014). Fundamentos de programación en Java. Madrid: EME. Lemay, L. (2008). Java 6. España: Anaya. Joyanes, L. (2005). Programación orientada a objetos. Madrid: McGraw-Hill. E) Base de Datos Pérez Marqués, María, “SQL Server 2008 R2: motor de base de datos y administración”, editorial ALFAOMEGA, Año 2012 Reinosa, Enrique José , Y otros, “Bases de Datos”, editorial ALFAOMEGA, Año 2012 F) Redes de Computadores TANENBAUM, Andrew, Redes de Computadoras Prentice Hall, 2012: STALLINGS, William, Data and Computer Communications. 9 ª Ed Prentice Hall, 2010. 9. INSTRUCTIVO PARA EL ESTUDIANTE El estudiante que opta por rendir el Examen Complexivo deberá observar las siguientes consideraciones: I. Haber recibido la aprobación oficial de la inscripción para la presentación del Examen Complexivo por parte de la Escuela de Ingeniería en Electrónica en Control y Redes Industriales. II. Cancelar el valor estipulado en la Tesorería de la Institución III. Presentarse con puntualidad al lugar de recepción del Examen Complexivo en la fecha y hora establecidas por la Escuela de Ingeniería en Electrónica en Control y Redes Industriales. IV. Identificarse con documentos originales (cédula de ciudadanía o pasaporte) y la factura de pago ante el Presidente del Tribunal de recepción del Examen Complexivo. V. Observar las disposiciones que cada Coordinador de Comisiones de Examen Complexivo proporcionará al momento de la prueba. VI. Desarrollar con la mejor pertinencia las pruebas correspondientes al Examen Complexivo. VII. Para la prueba estructurada de tipo objetiva, se podrá utilizar la plataforma virtual institucional. VIII. Para la prueba no estructurada, recibirá las preguntas / problemas específicos que deberá desarrollar el estudiante, de temas y subtemas específicos de la carrera. IX. El estudiante deberá identificarse en la prueba escribiendo sus nombres completos, número de cédula de ciudadanía o pasaporte. X. Al concluir las pruebas, deberá entregar al Coordinador de las Pruebas el desarrollo efectuado. XI. Para la prueba estructurada esta totalmente prohibido el uso de dispositivos de comunicación como celulares, tablets, etc. XII. Cualquier intento de fraude comprobado, será penalizado con el retiro de la prueba estructurada y tendrá una calificación de 0 puntos. XIII. De no estar conforme con las calificaciones de la prueba no estructurada, podrá ejercer el derecho de recalificación establecido. Ing. Alberto Arellano A. DIRECTOR EIECRI Dra. Narcisa Salazar MIEMBRO COMISION EXAMEN COMPLEXIVO Dr. Alonso Alvarez MIEMBRO COMISION EXAMEN COMPLEXIVO