Memorias - Campus Virtual ORT

Anuncio

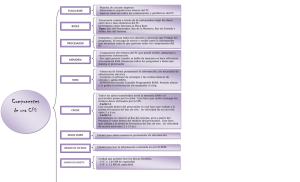

Unidad 4 – Memorias MEMORIAS 3 PARÁMETROS QUE CARACTERIZAN A LAS MEMORIAS 3 CAPACIDAD DE ALMACENAMIENTO 3 TIEMPO DE ACCESO 3 COSTO POR BIT ALMACENADO 3 MODO DE ACCESO 4 CLASES DE MEMORIAS 5 REGISTROS 5 MEMORIA PRINCIPAL (MP) 5 MEMORIA CACHÉ 5 MEMORIA PRINCIPAL 5 TAMAÑO DE LA MEMORIA 6 PALABRA DE MEMORIA 6 DIRECCIONAMIENTO DE MEMORIA 7 ACCESO A MEMORIA – CICLO DE MEMORIA 8 OPERACIÓN DE LECTURA 9 OPERACIÓN DE ESCRITURA 9 TIEMPO DE ACCESO A MEMORIA 9 CHIPS DE MEMORIA 10 ACCESO RANDOM O ALEATORIO 11 TIPOS DE MEMORIA 11 MEMORIAS RAM 12 MEMORIAS ROM 13 VERIFICACIÓN DE INTEGRIDAD DE DATOS 14 BIT DE PARIDAD 14 CÓDIGO DE CORRECCIÓN DE ERRORES 15 REGISTROS 15 ASCI / Introducción a la Informática / Unidad 4 1 BUFFERS 16 MEMORIA CACHÉ 16 JERARQUÍA DE MEMORIAS 19 BUSES DE LA COMPUTADORA 20 BIBLIOGRAFÍA 22 ASCI / Introducción a la Informática / Unidad 4 2 Memorias Una memoria es cualquier elemento que nos permite almacenar la información que deseemos y luego recuperarla cuando la necesitemos. En un sistema de computación, debemos almacenar información bajo nuestro control (es decir saber dónde la colocamos) y poder recuperarla en el momento necesario. En esta unidad veremos cómo se almacena información y cómo se recupera, en los distintos tipos de memorias de un sistema de procesamiento de datos. Parámetros que caracterizan a las memorias Las memorias difieren entre sí por cuatro características, que se constituyen en sus parámetros fundamentales: 1. Su capacidad de almacenamiento. 2. Su tiempo de acceso. 3. Su costo por bit almacenado. 4. Su modo de acceso. Capacidad de almacenamiento Es la cantidad de información que una memoria puede contener simultáneamente y se mide normalmente en bytes. Actualmente esta capacidad debe expresarse en grandes múltiplos del byte. Es importante el concepto de simultaneidad ya que, si la midiéramos a lo largo del tiempo, la rotación de los valores almacenados podría distorsionar este valor. El tiempo de permanencia, que llamaremos persistencia, de la información almacenada, es un parámetro asociado al uso de la memoria, pero no a la memoria en sí misma. Tiempo de acceso Es el tiempo requerido para leer o grabar un valor en una memoria. En algunos casos, este tiempo será absoluto, es decir, independiente de las circunstancias y propio exclusivamente de la memoria en sí misma. En otros, dependerá de estas circunstancias, en cuyo caso deberemos hablar de tiempos promedio de acceso. Costo por bit almacenado Una memoria con mayor capacidad de almacenamiento y menor tiempo de acceso, cuesta más que un equivalente con menores prestaciones. ASCI / Introducción a la Informática / Unidad 4 3 Modo de acceso Podemos distinguir tres formas de clasificar las memorias: 1) Por la cantidad de información involucrada en cada acceso: ● Memorias de acceso a palabra. EJEMPLO: la MP. ● Memorias de acceso a bloque. EJEMPLOS: discos (bloques de tamaño fijo) y cintas (bloques de tamaño no necesariamente fijo). 2) Por la forma de ubicar la información en la memoria. ● Acceso por nombre o identificación lógica del elemento de almacenamiento que la contiene. EJEMPLO: Registros de datos o de uso general. ● Acceso por dirección. EJEMPLO: Memoria RAM. ● Acceso por contenido. EJEMPLO: Memoria caché. 3) Por la forma en que la información es recuperada o grabada en el medio. ● Acceso directo. EJEMPLO: discos. ● Acceso aleatorio. EJEMPLO: RAM. ● Acceso secuencial. EJEMPLO: cintas. En los accesos directo y aleatorio, las diferentes posiciones de la memoria pueden accederse en cualquier orden, mientras que en los de acceso secuencial, las grabaciones y lecturas deben hacerse en forma consecutiva, es decir, para acceder a la posición n es necesario pasar previamente por las n-1 anteriores. ASCI / Introducción a la Informática / Unidad 4 4 Clases de memorias Registros Pequeñas memorias (del orden de 8, 16 hasta 64 bits), de acceso extremadamente rápido y con una persistencia normalmente mínima, que son piezas clave en el funcionamiento del sistema. Memoria Principal (MP) Memoria en la cual se almacenan las instrucciones y datos de los procesos que están siendo ejecutados en un instante de tiempo. Memoria caché Memoria rápida y de pequeña capacidad destinada a acelerar el acceso a la información almacenada en la MP, transparente al usuario y de ninguna manera imprescindible para el funcionamiento del sistema. Memoria principal La memoria principal es la parte de la computadora donde se almacenan programas y datos. Sin una memoria en la cual los procesadores puedan leer y escribir información, no existirían los computadores de programa almacenado. La memoria principal almacena bits en celdas independientes, aisladas entre sí, que contienen 1 byte de información. Cada celda se localiza en el conjunto mediante un número binario identificatorio, que constituye su dirección, o indicación de su posición en ese conjunto, por lo tanto en relación con cada celda se tienen dos números binarios: ● Un número fijo, la dirección (de más de 32 o 64 bits en la actualidad) que presentado en los circuitos de la memoria permite acceder a una celda. Este número no se puede alterar, ya que está establecido circuitalmente. ● Un conjunto de 8 bits, que es el contenido informativo de esa celda. Este número puede cambiarse si la memoria es alterable. ASCI / Introducción a la Informática / Unidad 4 5 En cada dirección de memoria (celda) sólo pueden leerse o escribirse 8 bits por vez, sin posibilidad de operar menor cantidad de bits o un bit aislado. Dado que la palabra “registro” en un significado general indica algún lugar dónde los datos se pueden registrar, guardar, podría designarse así a cada celda de memoria, y decir que la memoria principal está formada por un conjunto de registros independientes de 8 bits cada uno. Tamaño de la memoria Las computadoras, que emplean como representación interna el sistema de numeración binario, expresan las direcciones de memoria como un número binario. Si una dirección tiene m bits, el número máximo de celdas direccionables es 2m. El número de bits de la dirección determina el número máximo de celdas direccionables directamente en la memoria y es independiente del número de bits por celda. En una memoria que guarda un byte por posición, debe haber tantas posiciones como bytes tenga la memoria. Esto es, una memoria de 2 MB implica que se deben identificar 2097152 posiciones distintas, asignándole un número binario distinto para cada una, que es su dirección. Una memoria tiene un número N de celdas que siempre es una potencia de 2, por lo cual las mismas se localizan mediante direcciones que van de 00..00 hasta 11..11. De esto se deduce que, al aumentar en uno el exponente del número dos, se duplica la cantidad de memoria. O sea si una memoria tiene el doble de capacidad que otra, los números que forman las direcciones de la primera deben tener un bit más que los números que forman las direcciones de la segunda. Es decir, 2 memoria * 2n = 2(n+1) Siendo n la cantidad de bits que ocupa la dirección de Palabra de memoria Cuando los datos o instrucciones ocupan más de un byte se almacenan fragmentados en varios bytes, los cuales deben estar contenidos en celdas correspondientes a posiciones consecutivas de memoria, o sea en direcciones sucesivas. En una operación de lectura o escritura de memoria principal se puede acceder a varias celdas consecutivas simultáneamente. El número máximo de éstas constituye la palabra (word) de memoria. Dicho número puede ser 1, 2, 4 u 8 bytes, dependiendo de la cantidad de líneas de datos que salen del procesador hacia memoria. Una computadora con palabras de 32 bits tiene 4 byte/palabra, mientras que una con palabra de 64 bits tiene 8 byte/palabra. La importancia de las palabras es que casi todas las instrucciones operan con palabras enteras y sus registros tienen capacidad para albergarlas. ASCI / Introducción a la Informática / Unidad 4 6 00000010000001111000 La dirección 02078 (expresada en hexadecimal) contiene el 0110001 como información. Cuando se habla de una palabra (o word) de memoria o “longitud de palabra”, se hace referencia a la máxima cantidad de bytes que la UCP puede leer o escribir en cada acceso a memoria principal. Entonces, el bus que conecta la UCP y la memoria principal debe tener tantas líneas de datos como bits tenga la longitud de palabra del modelo de computador que se trate. Así mismo, en el ámbito de los microprocesadores, se menciona procesadores de 8, 16, 32 o 64 bits para indicar el número máximo de bits que puede tener un dato a operar por la UAL de cada uno. En consonancia con ello, los registros de la UCP para datos o resultados deben tener una longitud igual al tamaño de los datos que opera la UAL. Se comprende que un procesador de mayor número de bits sea más rápido que otro que opere con menos, pues en una sola instrucción puede manipular más bits. El número de bits de un procesador se define cuando se diseña el mismo, y es indicativo de su potencia de procesamiento. Direccionamiento de memoria En relación con la memoria principal, sólo son posibles dos operaciones que puede ordenar la UCP: la lectura o la escritura, pero antes de realizar cualquiera de ellas, la UCP debe direccionar la memoria principal. En la UCP, la memoria central tiene asociados dos registros para la realización de operaciones de lectura y escritura y un dispositivo encargado de seleccionar una celda de memoria en cada operación de acceso a la misma. Ellos son: ASCI / Introducción a la Informática / Unidad 4 7 ● Registro de Dirección de memoria (RDM o RDI): antes de la realización de una operación de lectura o escritura se ha de colocar en este registro la dirección de la celda que se va a utilizar en la operación, bien para grabar en ella o para extraer de la misma el dato correspondiente. ● Registro de Datos (RDA): si se trata de una operación de lectura de memoria, este registro es el que recibe el dato de la memoria señalado por el RDM para su envío por medio del bus del sistema a la unidad que lo requiere. Si se trata de una operación de escritura en memoria, la información que hay que grabar, procedente de cualquier unidad funcional, es depositada por medio del bus en el RDA para que desde él se transfiera a la posición de memoria indicada por el RDM. ● Decodificador de direcciones: Este dispositivo se activa cada vez que se produce una orden de lectura o escritura, conectando la celda de memoria, cuya dirección figura en el RDM, con el RDA y posibilitando la transferencia de los datos en un sentido o en otro. La acción de direccionar o “direccionamiento” consiste en colocar en las líneas de dirección del bus, que llegan a la memoria principal, la dirección de la celda a la que se quiere acceder, para leerla o escribirla. Igualmente si se quiere acceder a 2, 4 o 8 posiciones consecutivas de memoria sólo se debe dar la posición de la primera. La MMU (“Memory Management Unit”) es un elemento de hardware responsable de realizar (en los sistemas en que esto es posible) la traducción de la dirección lógica generada por la UCP a la dirección física en la que la información será realmente almacenada en la memoria. Esta transformación se realiza durante la ejecución del proceso, denominándose en consecuencia reubicación dinámica. En consecuencia, la MMU genera siempre las direcciones físicas dónde se almacenará la información. Acceso a memoria – Ciclo de memoria Los ordenadores de hoy, por lo general almacenan datos en microcircuitos electrónicos de estado sólido (chips). Existen cierto número de configuraciones circuitales que permiten “escribir” datos en ellas, almacenarlos allí y posteriormente ASCI / Introducción a la Informática / Unidad 4 8 “leerlos”; y que pueden ser “sobrescritas” con nuevos datos cuando los antiguos dejan de hacer falta. Llamaremos ciclo de memoria a la secuencia de operaciones necesarias para producir una transferencia (lectura/ escritura) entre la UCP y la memoria principal. Operación de lectura LA UCP debe indicar la dirección de la celda a la que quiere acceder para que la memoria principal le proporcione el contenido de la celda direccionada. La operación de lectura de una palabra comprende los siguientes pasos: ● A partir del contenido del RDM, en las líneas de dirección del bus, la UCP coloca la dirección de la primera celda que se quiere leer. ● La UCP ordena la lectura mediante la línea de control del bus (de lectura/escritura) que va de la Unidad de Control a la memoria principal. ● Luego de un tiempo una copia del contenido de la dirección seleccionada y del contenido de la/s siguiente/s, aparece juntas en las líneas de datos del bus, a disposición de la UCP. Luego de viajar por el bus, constituyen el contenido del RDA. Operación de escritura Si en cambio, el acceso corresponde a una operación de escritura en memoria, la combinación de ceros y unos que está contenida en las celdas que conforman la palabra de memoria direccionada, se deberá cambiar. En una operación de escritura los pasos son los siguientes: ● La combinación binaria a almacenar en las celdas es colocada por la UCP en las líneas de datos del bus desde el RDA. ● En las líneas de dirección del bus la UCP coloca la dirección de la primera celda que se quiere escribir desde el RDM. ● La UCP ordena la escritura mediante la línea de control. ● Luego de un tiempo, una copia de la combinación enviada a MP queda almacenada en la celda direccionada y en la/s siguiente/s. De esto se deduce que una escritura es destructiva, ya que se pierde el contenido anterior de las celdas que reciben la nueva información. Si se quiere que una celda vuelva a tener el contenido anterior, la UCP (siguiendo la lógica de la instrucción) deberá colocar su valor en las líneas de datos y ordenar otra escritura. Tiempo de acceso a memoria Idealmente, las celdas de una memoria están organizadas de tal modo que todas ellas tienen el mismo tiempo de acceso. Por este motivo, se dice que son memorias de acceso random o aleatorio. Esto quiere decir que el tiempo de acceso a cualquier dirección de memoria es constante, independientemente de su ubicación. ASCI / Introducción a la Informática / Unidad 4 9 Se define el tiempo de acceso como el tiempo que transcurre entre que se direcciona una celda de memoria, hasta que aparece en sus salidas (conectadas a las líneas de datos del bus) el contenido de la celda direccionada. Este tiempo suele indicarse (en el chip de memoria) al final de su código, luego de un guión. Chip de memoria Chips de memoria La tecnología de circuitos integrados se presta a fabricar chips cuya estructura interna sea un patrón bidimensional repetitivo. Los chips de memoria son una aplicación ideal de esta tecnología. El número de bits que se puede colocar en un chip aumenta continuamente, duplicándose. Desde los albores de las memorias de semiconductores hasta principios de los 90, la memoria se fabricaba, se compraba y se instalaba como chips individuales. Las densidades de los chips iban desde 1 Kbits hasta 1 Mbits, pero cada chip era una unidad discreta. Puesto que una computadora tiene muchos chips de memoria, se requiere una señal para seleccionar el chip que se necesita en ese momento, de modo que responda y los demás no lo hagan. Se incluye la señal CS (Chip Select) para este fin. La señal se habilita para activar el chip. Además, para diferenciar las lecturas de las escrituras, se usa para las primeras la señal WE (Write Enable), que habilita la escritura, es decir que indica que se van a escribir datos. La señal OE (Output Enable) se habilita para alimentar las señales de salida. Si no está habilitada, la salida del chip se desconecta del circuito. Los chips de memoria grandes se suelen construir como matrices n x n que se direccionan por fila (LH) y por columna (LV). Esto reduce el número de terminales requeridas, pero hace más lento el direccionamiento del chip, ya que se necesitan dos ciclos de direccionamiento, uno para las filas y otro para las columnas. Para recuperar algo de la velocidad que se pierde por este tipo de diseño, algunos chips de memoria pueden aceptar una dirección de fila seguida de una sucesión de direcciones de columna para acceder bytes consecutivos de un renglón. (LH) 11 (LV) 01 11 01 ASCI / Introducción a la Informática / Unidad 4 10 Esquema de memoria de 16 celdas de 8 bits, con 16 direcciones que van de 0000 a 1111. Acceso random o aleatorio Básicamente, en los sistemas de memoria de acceso random, los dispositivos de lectura e inscripción de datos pueden llegar directamente a cualquiera de las posiciones específicas de memoria, con independencia de la situación material que tal posición ocupe en el medio. El dispositivo va directamente a la posición requerida. En una formación bidimensional, provista de decodificadores de fila y columna, las corrientes individuales encargadas de activar las líneas de localización, fluirán a través de otros medios de almacenamiento antes de alcanzar el requerido. No obstante la combinación de señales sólo da acceso a la única posición de memoria requerida (decodificador de direcciones). A fin de evitar esperas, la UCP debe tener acceso rápido a celdas de cualquier porción de MP, por lo cual no tiene sentido tener celdas de acceso secuencial. El acceso aleatorio o random access en una memoria implica que cualquier posición puede encontrarse en igual tiempo (para ser leída o escrita). Vale decir, que el tiempo de acceso es el mismo para cualquier dirección. Tipos de memoria Las primeras computadoras fabricadas comercialmente ya tenían MP con acceso random, o sea eran Random Access Memory (RAM), y cualquier celda podía ser escrita o leída todas las veces que se quería. Además, eran memorias volátiles, ya que perdían la información almacenada cuando se cortaba el suministro eléctrico. Por esta razón, RAM se convirtió en sinónimo de memoria de lectura y escritura y además, de memoria volátil. En el presente, los chips de memoria RAM que constituyen la MP son de tecnología “dinámica”, cuya característica es que en cada celda de memoria se almacena un byte en microscópicos capacitores que necesitan ser continuamente recargados eléctricamente. La cuestión de las denominaciones se complica desde que, para una porción de la MP, a partir de los años 70 se emplean chips de memoria ROM, siglas que corresponden a Read Only Memory (Memoria de sólo lectura). Este tipo de Memoria es la que contiene el código necesario para el arranque de la computadora. La ROM es también una memoria electrónica de acceso random, en la cual la escritura requiere un tiempo muchísimo mayor que su lectura, pero es no volátil, o sea que almacena la información en forma permanente. No necesita de energía eléctrica para mantener guardado los datos. Sí para leerlos. Se puede decir, entonces que: Memoria principal es RAM + ROM ASCI / Introducción a la Informática / Unidad 4 11 Las porciones RAM y ROM tienen en común que al contenido de cualquier porción de las mismas se puede acceder en forma random, o sea en igual tiempo (salvo las diferencias antes señaladas), sin búsquedas, indicando un número que las identifica, que es su dirección. Difieren en que cada posición RAM puede ser leída y escrita cuantas veces sea, siendo su contenido volátil, mientras que se accede al contenido no volátil de una posición ROM sólo para leerla. La porción de MP que es ROM en una PC, se denomina ROM BIOS (Basic Input Output System). El programa que contiene, se ejecuta al encender la computadora y sus funciones son: ● Verificar la configuración del Hardware y su correcto funcionamiento ● Traer desde un disco de sistema a la MP (escribir en ésta) una copia de los programas del sistema operativo del computador (acción conocida como bootear el sistema). ● Almacenar programas usados permanentemente para la transferencia de datos entre periféricos y memoria (Entrada / Salida de datos). Se denomina firmware al software contenido en una memoria ROM. Memorias RAM Existen dos tipos de memoria RAM: la estática y la dinámica. La RAM estática o SRAM (Static RAM) consta de 4 o 6 transistores, que forman un circuito con memoria, conocido como “flip-flop”. Éste permanece estáticamente en un estado eléctrico (que podemos representar, por ejemplo, como 1) o en otro (como 0), mientras no se apague el computador o se cambie su estado por una orden de escritura. Son memorias muy rápidas, con un tiempo de acceso típico de unos cuantos nanosegundos, pero debido a que son varias veces más caras que una DRAM (Dinamic RAM) por su menor capacidad por chip, no se usan en la memoria principal, sino en la memoria caché (a tratar). Las RAM dinámicas o DRAM, no usan flip flop, sino que son una matriz de celdas, cada una de las cuales contiene un transistor y un capacitor microscópico, el que cargado guarda 1 y descargado, 0. Este pierde su carga cada 10 a 20 milisegundos, por lo que hay que reponerla (acción de “refresco”) para evitar que los datos se pierdan. Las DRAM tienen una densidad muy alta (muchos Bits por chip) puesto que sólo necesitan un transistor y un capacitor por Bit, en comparación con los 6 transistores por Bit de una SRAM. Por esto las memorias principales casi siempre se construyen con DRAM, sin embargo esta capacidad tiene un precio, son lentas en comparación con las SRAM (aproximadamente de 10 a 1). La combinación de una caché SRAM y una memoria principal DRAM intenta combinar las propiedades ventajosas de cada una. Los chips de memoria VRAM (Video RAM) forman parte de la memoria principal, pero están en la plaqueta de vídeo. Guardan la información que sale hacia pantalla. Estos chips tienen casi el doble de patas que los de cualquier RAM. Esto se debe a que una VRAM tiene un bus de direcciones y datos para ser escritos por la UCP, y ASCI / Introducción a la Informática / Unidad 4 12 otro bus para direcciones y datos para ser leídos por los Circuitos de la plaqueta de vídeo, que manejan el monitor. Por eso se dice que la VRAM es una memoria de "dos puertas", dado que simultáneamente que es escrita por la UCP, puede ser leída por los circuitos de la plaqueta. Memorias ROM Los primeros chips ROM, hoy denominados ROM "fabricados a medida", se encargaban a los fabricantes de chips, indicándole el contenido que debía tener cada celda. Entonces, cuando se fabricaba cada chip, se grababan los contenidos que siempre tendría. La única forma de cambiar el programa de una ROM es cambiar todo el chip. A diferencia de los anteriores, los chips PROM ("Programmable ROM") se fabrican en serie, pero el interior de cada chip está preparado para que -en una segunda etapa- quien utilice uno o miles de estos chips pueda escribir una sola vez los contenidos que tendrán sus celdas. Esto se realiza en un dispositivo electrónico que se vende para tal fin. Una vez así grabada ("programada"), una PROM no puede ser re-escrita. Las ROM de la clase RMM (Read Mostly Memory), para ser mayormente leídas, son reprogramables, o sea se pueden volver a escribir, siendo que La escritura es poco frecuente frente a las operaciones corrientes de lectura. Las pastillas EPROM ("Erasable-Programmable ROM") se caracterizan por presentar una ventanilla transparente en su cara superior, que normalmente está cubierta por una etiqueta plateada autoadhesiva. Se puede cambiar el contenido de todas las celdas, re-escribiendo el nuevo contenido que tendrá cada una en un dispositivo semejante al usado para las PROM. Previo a ello se debe "borrar" (erase) el contenido de todas las celdas. Esto se logra haciendo pasar luz U.V por la ventana durante unos 15 minutos. Una EEPROM, ("Electrically Erasable ROM") no requiere el borrado de todas las celdas con luz U.V, dado que -como en una RAM- se puede seleccionar cada dirección que se quiere re-escribir, sin sacar la pastilla del circuito donde opera. Esto puede hacerse unas 10.000 veces. Las flash ROM en una fracción de segundo se borran eléctricamente por bloques, y luego se re-escriben las celdas consecutivas de un bloque. Este tipo de ROM en el presente se usa como memorias auxiliares portátiles para PC "notebook" y como parte ROM de la memoria principal; se utilizan también como soporte de la película en cámaras digitales. ASCI / Introducción a la Informática / Unidad 4 13 En el siguiente cuadro se clasifican los tipos de memorias en tres grupos, según sus características de re-escritura: Tipo SRAM Uso típico ROM PROM EPROM EEPROM Flash ROM Características de reescritura Borrado Volátil Cada byte direccionado puede ser re-escrito en igual Lectura y tiempo en que se tarda su escritura lectura, cuantas veces se necesite Eléctrico Sí Una vez que la memoria fue escrita, no se puede reescribir Imposible Caché nivel 2 DRAM VRAM Clase Memoria principal Memoria de video equipos en vol. grandes Equipos en vol. pequeños Prototipos de dispositivos Película para cámara digital Sólo lectura Principal- Una vez que la memoria fue escrita, se puede re-escribir mente lectura (“reprogramar”) un número ilimitado o muy grande de veces, pero la escritura es Lectura y lenta comparada con el escritura tiempo de lectura de un byte No Luz UV eléctrico Verificación de integridad de datos Un aspecto importante en el diseño de la memoria es la verificación de integridad de los datos almacenados en la memoria RAM. Actualmente se emplean dos métodos para asegurar la integridad de datos: La paridad ha sido el método más común hasta la fecha. Este proceso añade un bit adicional cada 8 bits (1 byte) de datos. El ECC (Error Correction Code- Código de Corrección de Errores) es un método más completo para la verificación de integridad de datos que puede detectar y corregir errores de bits individuales. Debido al carácter competitivo del mercado, cada vez es más común que los fabricantes de computadoras personales omitan la verificación de integridad de datos. Por ejemplo, eliminan la memoria de paridad con el objeto de reducir el precio de los sistemas (esta tendencia ha sido compensada, en parte, por la mejora en la calidad de los componentes de memoria que ofrecen ciertos fabricantes, y como resultado, los errores de memoria son relativamente escasos). Bit de Paridad Supongamos que por un ruido (interferencia electromagnética) durante una operación de lectura de memoria, la UCP recibe uno de los bits invertido. ASCI / Introducción a la Informática / Unidad 4 14 Dato correcto: 0 1 0 0 0 0 0 1 BIT mal leído por ruido 0 1 0 0 0 0 1 1 Dato incorrecto: Entonces, es posible que se reciba otra combinación sin que se perciba el error. Se verificará que ampliando la capacidad de una memoria de forma que cada posición contenga un bit extra (o sea de 9 bits), puede detectarse si se ha producido un solo error por inversión. Este bit denominado “de paridad” (que se agrega a la celda al almacenar un byte), debe ser siempre de valor tal que el conjunto de 9 bits tenga un número par de unos (paridad par), o un número impar de unos (paridad impar) Al escribir una posición de memoria, un circuito calcula el valor que debe tener dicho bit (0 o 1), y al leer la misma posición el mismo circuito verifica que los 9 bits leídos tengan paridad par de unos. En caso contrario el programa en curso se interrumpe, avisando que hay un problema de paridad en memoria. Como ejemplo, usando paridad par, la combinación antes citada, 01000001, se convierte en 010000010 (en negrita el bit de paridad). Por esto, si se lee incorrectamente se leerá por ejemplo 010000110, y se detectará el error. El método basado en la paridad tiene ciertas limitaciones, dado que permite detectar si uno solo de los bits recibidos cambió de valor, que es la mayor probabilidad de errores de una lectura de memoria. Si los bits errados son dos, la paridad será la misma y no hay forma de detectar una combinación mal recibida. Afortunadamente, la posibilidad de que esto suceda es extremadamente remota. Código de Corrección de Errores El sistema de Código de Corrección de Errores se utiliza principalmente en las PC más avanzadas y en los servidores de archivos. La diferencia más importante entre el ECC y la paridad es que el ECC es capaz de detectar y corregir los errores de un bit. Con ECC, la corrección generalmente se lleva a cabo sin que el propio usuario se de cuenta de que se ha producido un error. Dependiendo del tipo de controlador de memoria utilizado por la computadora, ECC también podrá detectar los errores sumamente raros de dos, tres o cuatro bits de memoria. Sin embargo, aún cuando ECC puede detectar estos errores de múltiples bits, sólo puede corregir los errores de un sólo bit. Si se presenta el caso de un error de múltiples bits, el circuito ECC devuelve un error de paridad. Registros Anteriormente se mencionó que se puede considerar una RAM como formada por registros de un byte, aunque en general, no se suele llamar registros a las posiciones de memoria. ASCI / Introducción a la Informática / Unidad 4 15 Asimismo, los registros de cualquier UCP, (que se direccionan en lenguaje simbólico por nombres), se identifican internamente por un número que oficia de dirección dentro de la misma (a partir de cero, como una pequeña memoria). Dicho número es el que debe figurar en el código de una instrucción que hace mención a un determinado registro de la UCP. Podemos decir, entonces, que salvo la diferencia cuantitativa entre los registros de la UCP y las posiciones de memoria, los registros de la UCP constituyen una pequeña RAM, siendo que cada registro se localiza al random mediante un número, para ser leído o escrito. Es importante tener en cuenta, que el acceso a un registro de la UCP es del orden de unos pocos nanosegundos. Buffers En general, un buffer adapta dos velocidades distintas, permitiendo independencia entre un transmisor y un receptor, con el fin de que ambos puedan estar simultáneamente ocupados, sin que el más rápido pierda tiempo esperando a otro. En computación, se empezó a usar la denominación memoria buffer para zonas de memoria principal dónde se guardan datos en tránsito, desde o hacia periféricos. Por ejemplo, permanecen en una de estas zonas datos que van llegando a unas ciertas velocidades provenientes de un disco, para ser procesados luego a gran velocidad por la UCP. Mientras los datos van arribando a memoria, la UCP puede dedicarse a ejecutar otro programa. También puede designarse buffer a un registro o registros que almacenan temporariamente información en tránsito. Desde la primera generación de computadoras, los periféricos no se conectan directamente a memoria principal para entrar o recibir datos de ella, sino que reciben o envían datos a memoria a través de registros ports intermediarios, que almacenan temporariamente los datos en ellos. Dada la gran diferencia existente entre la operación y la transmisión de datos realizada por la parte central de una computadora (totalmente electrónica) y las realizadas por sus periféricos (que pueden tener movimientos mecánicos y/o humanos), se impone necesariamente la existencia de buffers (ports) entre ambos, para poder almacenar la información en curso, durante el tiempo necesario. Memoria caché La memoria caché (del francés cacher, que significa guardar o esconder) o "antememoria" de un procesador es una pequeña memoria rápida SRAM, ubicada entre la UCP y la memoria principal DRAM, que sirve para simular una memoria principal con un tiempo de acceso semejante al de la SRAM. Del conjunto de instrucciones de un programa y los datos a procesar que están en memoria principal, una caché contendrá una copia de las próximas instrucciones que probablemente ejecutará la UCP, y los datos que estas deben procesar. La idea fundamental en que se basa la memoria caché es sencilla: las palabras de memoria de mayor uso se mantienen en la caché. Cuando la UCP necesita una palabra, primero la busca en la memoria caché. Si la encuentra se produce un hit, si no miss, y sólo entonces recurrirá a la memoria principal. ASCI / Introducción a la Informática / Unidad 4 16 Así pues, el éxito o el fracaso dependen de qué fracción de las palabras están en la caché. Si una referencia a la memoria dada es la dirección A, es probable que la siguiente referencia sea una dirección cercana a A, ya que salvo las llamadas a procedimientos y las bifurcaciones las instrucciones de los programas se traen de posiciones consecutivas de la memoria. Además la mayor parte del tiempo de ejecución de un programa se invierte en realizar ciclos, en los que un número limitado de instrucciones se ejecutan una y otra vez. La observación de que las referencias a la memoria que se hacen en cualquier período corto tienden a usar una fracción de la memoria total se denomina principio de localidad y constituye la base de todos los sistemas de caché. Si una palabra se lee o escribe k veces en un intervalo corto, la computadora necesitará una referencia a la memoria lenta y k-1 referencias a la memoria rápida. Cuanto mayor sea k, mejor será el desempeño global. Un subsistema circuital denominado controlador de caché asegura que lo anterior se cumplirá, en más del 90% de los accesos (esta cifra depende del software ejecutado), o sea que la UCP sólo accederá a MP en un 10% de todos los accesos requeridos. El porcentaje anterior se logra, pues, almacenando con anticipación en el caché instrucciones y datos que la UCP solicitará próximamente. Por lo tanto, el manejo de la memoria caché está a cargo de un hardware de control, no requiriéndose software alguno. Resulta, entonces, que la memoria caché es un buffer inteligente, del cual la UCP toma información conforme a su velocidad de procesamiento, siendo que dicha información pasa de la memoria principal DRAM al caché a la velocidad con que esta puede ser leída. Por tal motivo es que típicamente se usan varios Mb de memoria principal DRAM y sólo hasta 512 Kb de SRAM para caché (esto es para PC, en algunos procesadores la memoria principal es de varios Gb y la Caché puede llegar hasta a 2Gb). Ya que además de la cuestión del costo, el tiempo requerido para determinar, en el controlador de caché, si se encuentra la información buscada aumenta con el tamaño de la caché. Por esto más allá de un cierto límite no se obtienen mejoras aumentando la capacidad de un caché. Para mejorar el tiempo de acceso a memoria, los procesadores operan con dos niveles de caché: ● Un primer nivel (level 1), constituido por el caché interno que el procesador lleva incorporado junto con su controlador de caché. A éste nivel se accede tan rápidamente como a los registros de UCP. ● Un segundo nivel (level 2) lo constituye el caché externo al procesador, conformado por los chips SRAM opcionales, que pueden insertarse en zócalos de la “mother” (Placa Madre). Cada vez que la UCP ordena acceder a la MP, por medio de las líneas de dirección, el controlador de caché determina en el “directorio del caché” si la información se encuentra en el mismo. El caché interno provee la información de si está o no en él. Si se produjo un “miss”, en aproximadamente 30 nanosegundos la proveerá el caché externo, pasando una copia de la información requerida al interno. Si la información tampoco está en el caché externo, se deberá acceder a la memoria principal, realizando una copia de la información en ambos cachés. Resulta, entonces, que el caché de segundo nivel permite una menor utilización directa de la MP por parte de la UCP, descongestionando el bus que une a ambos. Esto permite que la MP sea accedida por otros dispositivos, mientras la UCP accede a los niveles de caché para leer y escribir información. ASCI / Introducción a la Informática / Unidad 4 17 (L1) Caché (L2) El caché se encuentra lógicamente entra la UCP y la MP. Si bien se suele representar la estructura de la memoria caché en la misma forma de bytes aislados de la memoria principal, en el caché no existe una dirección por byte, sino que un bloque de bytes, llamado línea, es accedido por cada dirección del caché, para ser leídos o escritos. Al producirse un miss, el controlador ordenará que la palabra direccionada en MP se escriba en el caché, y que se lleven a cabo un número de lecturas sucesivas de MP (burst transfer) a partir de la dirección leída, que también se escribirán en el caché. Así el caché se va preparando para contener los bytes que siguen a los que no tenía cuando pidió leerlos la UCP, que son los que seguramente luego pedirá la UCP. El reemplazo de una línea de caché por otra, se decide según un algoritmo prefijado, como el LRU (least recently used), es decir que se reemplaza la línea menos recientemente usada. El controlador de caché también maneja la estrategia de escritura del caché la MP. Una forma denominada write through consiste en actualizar simultáneamente ambas. Otra, llamada write back, consiste en marcar en el caché las posiciones que la UC escribió en él, de forma que cuando el bloque o línea que las contiene es reemplazado en el caché, se escriban entonces las posiciones correspondientes de la memoria principal. ASCI / Introducción a la Informática / Unidad 4 18 Jerarquía de Memorias Las jerarquías o niveles de memoria se vienen usando (con distintas tecnologías) desde la primera generación de computadoras, a fin de lograr, a un costo razonable por byte memorizado, minimizar el tiempo de ejecución de los programas y almacenar la cantidad de información requerida. Resulta más económico emplear medios de almacenamiento de bajos costos para guardar la información que no se va a usar inmediatamente. La información se guarda en uno u otro nivel, de acuerdo al uso próximo que se hará de ella, pudiendo existir copias de ella repetidas en varios niveles. Para que una jerarquía funcione se deben organizar las instrucciones y datos de forma tal que el número de accesos disminuya sustancialmente de un nivel de memoria a otro inferior. Pirámide de jerarquía de memoria en una computadora, según el tiempo de acceso Al bajar por la jerarquía, tres parámetros clave crecen: ● Primero, el tiempo de acceso se alarga. Los registros de la UCP pueden accederse en unos cuantos nanosegundos. Las memorias caché en pocas veces más que los anteriores. Los accesos a memoria principal suelen ser de varias decenas de nanosegundos. Los tiempos de acceso a disco son de por lo menos 10 milisegundos, y el acceso a cinta o disco óptico dependen de si deben insertarse lo medios a la unidad. ● Segundo, la capacidad de almacenamiento es mayor cuanto más se baja en la jerarquía. Los registros de la UCP pueden llegar a tener 128 bytes; los cachés unos cuantos Mb; las memorias principales decenas o miles de Mb; los discos magnéticos de unos cuantos Gb a decenas de Gb. Las cintas y los discos ópticos se guardan, generalmente fuera de línea, así que su capacidad dependen del presupuesto invertido en ellos por el propietario. ● Tercero, el número de bits que se obtiene por dólar invertido aumenta al bajar por la jerarquía. ASCI / Introducción a la Informática / Unidad 4 19 Al describir la relación entre la memoria caché y la principal, se vio que durante la ejecución de un programa se accede más frecuentemente a ciertas zonas “activas” de MP, siendo que las restantes zonas de ésta son accedidas muy pocas veces. Igualmente, de todos los archivos que contiene en forma permanente un disco rígido. Sólo una porción muy pequeña se copian en MP, para ser procesados por la UCP. Entre la MP y la memoria auxiliar del disco rígido, se indica un caché de disco rígido, el cual se realiza con una DRAM, que pertenece a la electrónica de la unidad de disco. Puede mencionarse que mediante el disco rígido puede simularse una memoria principal virtual, con una capacidad ilimitada, a costa de un pequeño aumento del tiempo de acceso promedio a la memoria. Los disquetes, discos ópticos y cintas, guardan, en general copias de resguardo de archivos existentes en el disco rígido, y otros archivos que éste no pueda contener. En general, todas las instrucciones y datos de un nivel se encuentran en el inmediato inferior, y así sucesivamente hasta la jerarquía más baja. La composición de las jerarquías supone lograr soluciones de compromiso para conjugar distintas propiedades que presentan las memorias intervinientes. (Cómo se describió al tratar el caché, su inclusión respondía a un compromiso entre velocidad de acceso requerida, capacidad de almacenamiento y costo). Es decir que, para cada computador, se busca crear una jerarquía de memorias tal que para el usuario simule una memoria con una capacidad de almacenamiento auxiliar virtualmente ilimitada, y con un tiempo de acceso tan rápido hoy en día, como el primer nivel de memoria caché incorporado al procesador. Buses de la computadora Se denomina bus del sistema al conjunto de circuitos encargados de la conexión y comunicación entre la UCP y el resto de los componentes de un sistema. Para ello se utilizan varias líneas eléctricas que permiten la transmisión de los datos en paralelo. Un bus de n bits transfiere simultáneamente esa cantidad de bits entre dos unidades cualesquiera. Además de las líneas de datos, el bus consta de las líneas de control (que transmiten órdenes) y las líneas de direcciones (contienen la dirección hacia dónde van dirigidos los datos que se están transmitiendo en la línea de datos o la dirección de memoria que se quiere leer) Un bus es un camino eléctrico común entre varios dispositivos. Los buses pueden clasificarse por su función: pueden usarse dentro de la UCP para transportar datos entre sus componentes (UC y ALU), o externos a la misma, para conectarla con la memoria o los dispositivos de E/S. Cada tipo de bus tiene sus requisitos propio y sus propiedades. ASCI / Introducción a la Informática / Unidad 4 20 Si bien los diseñadores de la UCP están en libertad de usar el tipo de bus que deseen, si se quiere que tarjetas diseñadas por terceros puedan conectarse al bus del sistema deben existir reglas bien definidas que digan cómo funciona el bus, que todos los dispositivos que están conectados a él deben obedecer. Esta reglas son el protocolo del bus. Deben existir también especificaciones técnicas que permitan la correcta conexión de los componentes. Algunos de los dispositivos que se conectan a un bus y que son activos y pueden iniciar transferencias de bus, se denominan amos o maestros (master), mientras que los que son pasivos se llaman esclavos (slave). Cuando la UCP ordena a un controlador de disco que lea o escriba un bloque, la UCP está actuando como maestro y el controlador de disco como esclavo. Mientras que el controlador de disco será maestro si ordena a la memoria que acepte las palabras que está leyendo de la unidad de disco, y la memoria será esclavo. En ninguna circunstancia la memoria puede ser amo. Ejemplos de amos (controladores) y esclavos de bus Amo Esclavo Ejemplo CPU Memoria CPU Dispositivo de E/S Iniciar transferencia de datos CPU Coprocesador Delegación de la UCP al coprocesador E/S Memoria Coprocesador CPU Traer instrucciones y datos DMA (acceso directo a memoria) Obtención de operandos de la CPU por el coprocesador Como las señales que producen los dispositivos no suelen ser lo suficientemente fuertes como para impulsar un bus, los maestros de bus se conectan al mismo con un chip llamado controlador de bus, que es, en esencia un amplificador digital. Así mismo, casi todos los esclavos se conectan al bus con un receptor de bus. En el ASCI / Introducción a la Informática / Unidad 4 21 caso de dispositivos que pueden cumplir con alternativamente ambas funciones, se emplea un chip combinado llamado transceptor de bus. Estos chips suelen ser dispositivos de tres estados, para poder “desconectarse” cuando no se necesitan, o estar conectados de forma un tanto distinta, llamada colector abierto, cuyo efecto es el mismo. Los aspectos fundamentales del diseño de los buses son: ● Anchura: es el número de señales de un bus. Para llegar al máximo de rendimiento el número de líneas en el bus debe igualar a la suma de números de bits de una palabra, al número de bits de la dirección máxima y al número de líneas de control, respectivamente ● Temporización: los buses se pueden dividir en dos categorías según sea su temporización: Un bus sincrónico tiene una línea alimentada por un oscilador de cristal piezo-eléctrico que emite un pulsos que determinan el ciclo del bus. La activación de las señales de control y la transmisión de datos y direcciones se debe realizar en sincronía con esos ciclos. El bus asincrónico no tiene un reloj maestro. Los ciclos del bus pueden tener las longitud que se requiera y no tiene porqué ser la misma para todos los pares de dispositivos. ● Arbitraje: Hasta ahora hemos supuesto que sólo hay un controlador de bus, pero en realidad los chips de E/S tienen que convertirse también en controladores de bus (además de la UCP), para leer y escribir en la memoria y para causar las interrupciones. Esto requiere de algún mecanismo de arbitraje de bus para evitar el caos que produciría el intento simultáneo de dos o más dispositivos de convertirse en controladores de bus. Bibliografía ● Ginzburg, M.C. La PC por dentro, Biblioteca Técnica Superior. ● Tanenbaum, A. Organización de computadoras. Un enfoque estructurado. ● Tucker, A. Cupper, R. y otros Fundamentos de Informática. ASCI / Introducción a la Informática / Unidad 4 22

![COMPONENTES_DE_LA_CPU_OSWALDO_IBARRA[1]](http://s2.studylib.es/store/data/000896384_1-834ea5f7823f030c85a9c1dfdecaf524-300x300.png)