CC41C Introducción al Hardware Examen

Anuncio

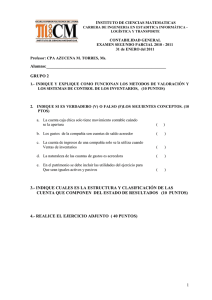

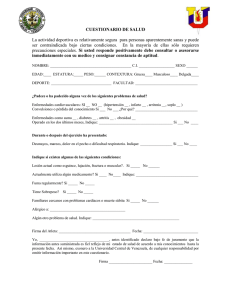

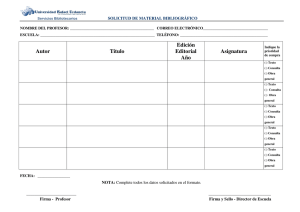

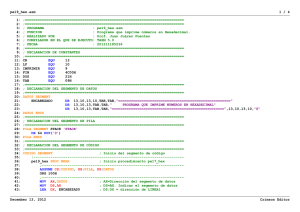

.,2%6$"*$ (+17).$ ( $ "* $ +.$ -%*),*&$ "( $ 1)$ (&$"*$D$ FGHHFF$ **2$1).$ ().".# 7'%2 $ .+$ &.+%".&$ $EF7E;$ $KLMO$ 41*$&*$+*.$.+01).$-(+17).# S7'+*7*),*$ KLMO $ 1&.)"( $ -(7($ @.&* $ *+ $ 7%&7( $ ,*-+."( $ KLM $ "."( $ *) $ +.$ '2*01),.$8#$ $!,%+%-*$71+,%'+*G(2*&3$2*0%&,2(&3$&17."(2*&3$-(7'1*2,.&$,2%&,.,*3$ *,-# $ $ E% $ )*-*&%,. $ 1) $ -%2-1%,( $ &*-1*)-%.+3al$ &R+( $ *&'*-%/%41* $ &1 $ "%.02.7. $ "*$ CC41C Introducción Hardware *&,."(&3$)($+($%7'+*7*),*# Examen - Primavera 2010 T*&1*+J.$*&,*$'2(@+*7.$@.22%*)"($-Q-+%-.7*),*$+.&$-(+17).&$"*+$,*-+."($'.2.$ Pregunta 1: Conceptos (2 puntos) "*&-1@2%2$&%$1).$,*-+.$/1*$'2*&%().".#$$B1.)"($&*$.-,%J*$+.$+Q)*.$(*3$%0)(2*$+.$ -(+17).$'(2$@.22*2 $*)$*&*$%)&,.),* $C$+*.$'2%(2%,.2%.7*),* $+.$-(+17).$-1C($ Responda brevemente las siguientes preguntas (no más de 4 líneas por respuesta) )=7*2($.'.2*-* $*) $,D7,;3$'.2. $*),2*0.2 $&1 $*&,."( $*) $EF7E;#$ $P.$ -(+17).$ (0.4 punto por repuesta) %0)(2.".$'1*"*$&*2$@.22%".$*)$+.$J1*+,.$&%01%*),*3$'1*&$*+$1&1.2%($)($'*2-%@%25$ I. Qué es Symmetric Multi Processing (SMP) y que son las ventajas y desventajas? +.$"%/*2*)-%.# II. Qué es localidad espacial y localidad temporal? III. En circuitos secuenciales, qué pasa al fin de cada ciclo (ósea justo antes del pulso de bajada del reloj)? IV. Qué es Double Data Rate SDRAM, qué parte de acceso a la memoria acelera y qué !"#$% "'($acelera? P. $ /%012. $71*&,2. $ -%-+( $ '(2 $ -%-+( $ +. $ *U*-1-%R) $ "* $ J.2%.&$ parte& no V.%)&,21--%()*& En la arquitectura por qué la instrucción SET $const32,%reg no existe? $ *)SPARC, $ 1) $ '2(-*&."(2# $ $ S)"%41* &% $ *& $ .'+%-.@+* $ ;%< $ ,%'( $ "*$ =(3C+&'/$D .241%,*-,12.3$;%%<$%)&,.),*&$*)$41*$&*$1&.$2*0%&,*2$@C'.&&%)03$;%%%<$%)&,.),*&$*)$ 41*$&*$1&.$2*)(7@2*$"*$2*0%&,2(&#$$V"*7.&3$;%J<$-(7'+*,*$*+$"%.02.7.$C$;J<$ Pregunta 2: Arquitecturas Avanzadas (2 puntos) 2*I.0.$*+$"%.02.7.$'.2.$1).$.241%,*-,12.$"*$,%'($&1'*2*&-.+.2$"*$02."($A# .#\ VMM$$$TY3$T93$TZ @#\ E!L$$$TD3$X3$T[ -#\ VMM$$$T[3$X3$T8F "#\ P]VM$^T8FOD_3$T88 *#\ VMM$$$TY3$AF3$T8A /#\ E!L$$$$T883$X3$T8W 0#\ VMM$$$T83$TA3$TW 8 A W X Y 9 Z D [ 8F H M > E H M > E H M > E H M > ` ` ` E # # # ### I. !"#$% La figura muestra ciclo $por ciclo $ &*-1*)-%. la ejecución$ "* de$ "%2*--%()*& varias instrucciones en un $ ;*)$ & )'($ P. $ &%01%*),* *& $ 1). $ "* $ 7*7(2%. procesador. Indique tipo de arquitectura, completa el diagrama e indique 8A$ I*G."*-%7.+<$+*Q".&$'(2$$1)$'2(-*&."(2$-()$1).$7*7(2%.$-.-I*$"*$$X$KL$;A • instantes en que se usa register bypassing, @C,*&<$"*$1)$02."($"*$.&(-%.,%J%"."N • instantes en que se usa renombre de registros. YHWF$$9M8D$$YHWF$$ZHWF$$9M8F$$ZHWF$$YHWF$$9M8F >+$-.-I*$'(&**$+Q)*.&$"*$89$@C,*&#$ $E1'()0.$41*$*+$-.-I*$*&,5$%)%-%.+7*),*$ J.-Q(# $ $ B(),*&,* $ ;%< $ -15+ $ *& $ +. $ '(2-%R) $ "* $ +. $ "%2*--%R) $ 41* $ &* $ 1&. $ -(7($ %$*+,%$"3$;%%< $-15+$*&$+.$'(2-%R) $"*$+.$"%2*--%R)$41*$&*$1&.$'.2.$%)"*G.2 $*+$ -.-I*3$C$;%%%<$41a$.--*&(&$.$+.$7*7(2%.$&()$.-%*2,(&$*)$*+$-.-I*$C$-15+*&$&()$ II. Se tiene un computador que posee un cache write-through de 4KB (4 * 1024 = 1000 "*&.-%*2,(&# en hex) con lineas de 16 bytes (16 = 10 en hex). La tabla muestra la historia de accesos que un programa realizó en memoria. Para cada acceso se indica la dirección en hex, tipo de acceso y si se hizo en cache o en memoria. Indique una cota inferior para los grados de asociatividad que posee este cache, explicando como lo deduce. 00/X RS/T A 00/1 01/0 10/0 1*/ 0 01/1 00/1 Pregunta 3: Circuitos (2 puntos) I. II. B 11/X C 00/X Implementa este circuito. Haga la 1*/ 0 codificación de estados, la tabla de verdad, 01/0 los mapas de Karnaugh y las formulas algebraicas. (No dibujes el circuito.) RS/T A 00/1 01/0 10/0 1*/ 0 Para el circuito resultante, complete el diagrama de tiempo abajo. (La salida en ningún caso puede ser X). El estado inicial es A, indique los estados sucesivos. B 01/1 00/1 11/X C 1*/ 0 01/0 CLK R S T ? A ? ? ? CLK R S T ? A ? ? ?