Tipos de FPLDs y tecnologías de programación.

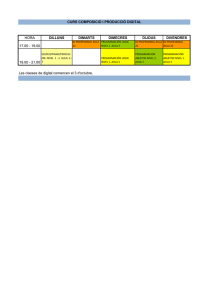

Anuncio

Electrónica Digital II M. C. Felipe Santiago Espinosa Tipos de FPLD’s Octubre / 2014 Clasificación Una clasificación básica es la siguiente: – SPLD (Simple Programmable Logic Device) PROM (Programmable Read Only Memory) PLA (Programmable Logic Array) PAL (Programmable AND-Array Logic) GAL (Generic Array Logic) CPLD (Complex Programmable Logic Device) FPGA (Field Programmable Logic Device) PROM PROM (Ejemplo) – X = AB’C’ + A’B’C + A’BC – Y = A’BC’ + AB’C – Z = AB’C’ + ABC’ + A’B’C + ABC PLA A mediados de la década de 1970 surgen los arreglos lógicos programables (PLA, Programmable Logic Array). Tienen un arreglo AND programable seguido de un arreglo OR programable. Pueden configurarse para operaciones lógicas AND y OR. realizar PLA PLA (Ejemplo) – X = AB’C’ + A’B’C + A’BC – Y = A’BC’ + AB’C – Z = AB’C’ + ABC’ + A’B’C + ABC PAL A finales de la década de 1970 surge el arreglo lógico AND programable (PAL, Programmable AND-Array Logic) Mejora los tiempos de retardo del PLA El PAL consta de una arreglo AND programable y un arreglo OR fijo PAL PAL X = AB’C’ + A’B’C Y = A’BC’ + AB’C Z = A’B’C + ABC GAL Con los dispositivos PROM, PLA y PAL solo se pueden construir circuitos combinacionales Para crear circuitos secuenciales se requiere: – Elementos de estado (Flip-Flop) – Señal de reloj – Líneas de retroalimentación Con estos requerimientos se crearon los arreglos lógicos genéricos (GAL, Generic Logic Array) Una GAL se basa en un Arreglo AND programable y macro celdas lógicas de salida GAL Combinacional ( OLMC, Output Logic Macrocell ) Secuencial CPLD Un CPLD es un dispositivo lógico programable complejo (Complex Programmable Logic Device) Son circuitos programables construidos con base en arreglos de bloques lógicos (LABs) Cada LAB contiene un conjunto de Macro celdas Con cada macro celda se puede realizar una función lógica independiente Los LABs se conectan entre si a través de un arreglo de interconexiones programable Es posible realizar sistemas con mayor complejidad Complex Programmable Logic Devices (CPLD) CPLD (Diagrama a Bloques) CPLD (Macro celda) CPLD (Bloques de Control de I/O) FPGA Un FPGA es un Arreglo de Compuertas Programable en Campo (Field Programmable Logic Device) Son dispositivos programables que están construidos con base en una matriz de bloques lógicos configurables (CLB) En cada CLB es posible desarrollar una función lógica independiente Entre los diferentes CLBs existen líneas de interconexión de diferentes tamaños que también son configurables Alrededor de la matriz se encentran bloques de entrada y salida (IOB) que también son configurables FPGA FPGA Un FPGA es un arreglo de bloques lógicos programables colocados en una infraestructura de interconexiones programable; es posible programar la funcionalidad de los bloques lógicos, las interconexiones entre bloques y las conexiones entre entradas y salidas. Un FPGA es programable a nivel hardware. proporciona las ventajas de un procesador general y un circuito especializado reconfigurarse las veces que sea necesario su funcionalidad. Así, un FPGA de propósito que puede para depurar El tamaño y velocidad de los FPGAs son equiparables a los ASICs, pero los FPGAs son más flexibles y su ciclo de diseño es más corto. Principales Fabricantes Arquitectura de la Familia Spartan-3E de Xilinx 22 IOBs Hay 3 rutas principales : • Entrada • Salida • Tres estados Bloques Lógicos Configurables Los CLBs (Configurable Logic Blocks) constituyen los principales recursos lógicos para implementar circuitos combinacionales o secuenciales síncronos. 24 Interior de un Slice 1 CLB = 4 Slices 25 Bloques RAM 26 Bloques RAM 27 Multiplicadores Empotrados 28 Multiplicadores Empotrados 29 Electrónica Digital II M. C. Felipe Santiago Espinosa Tecnologías de Programación Octubre / 2014 Tecnología de Programación El fusible es el primer elemento programable por el usuario, utilizado en los más simples PLDs. Actualmente se tienen diferentes tipos de “interruptores” programables para la configuración de dispositivos de alta densidad, como CPLDs y FPGAs. Las propiedades de estos interruptores programables, como tamaño, volatilidad, tecnología de fabricación, resistencia interna y capacitancia, determinan las principales características de una arquitectura FPLD. El Antifusible ONO Un antifusible es lo opuesto a un fusible. Es un circuito abierto hasta que se le hace circular una corriente (cerca de 5 mA). La corriente funde una capa aislante delgada para formar un enlace resistivo permanente. La serie ACT de FPGAs de Actel utiliza esta tecnología de programación, en un antifusible conocido como PLICETM. El Antifusible Metal-Metal QuickLogic usa un antifusible metal-metal llamado ViaLinkTM.. Un antifusible metal-metal permite una conexión directa a las capas metálicas y con sume menos área (se reduce la capacitancia) en contraste a los antifusibles de poly-difusión (antifusible ONO). RAM Estática (SRAM) RAM Estática (SRAM) Una celda SRAM puede utilizarse para controlar intersecciones y seleccionar diferentes opciones para el ruteo de señales. Compuerta Flotante (EPROM/EEPROM) Compuerta Flotante (EPROM/EEPROM) Sin programar es un transistor «normal», utilizado para fijar un nivel bajo en una “línea de un bit” cuando una “línea de una palabra” es puesta en alto. También puede ser utilizado para implementar lógica al estilo ANDalambrada De esta forma proporciona lógica y ruteo.