Unidad 2: Análisis y diseño - Universidad de Especialidades del

Anuncio

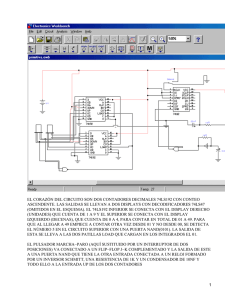

UNIVERSIDAD DE ESPECIALIDADES ESPÍRITU SANTO FACULTAD DE SISTEMAS TELECOMUNICACIONES ELECTRONICA SYLLABUS FOR DAC 11 VER 12 03 09 MATERIA: SISTEMAS DIGITALES II PROFESOR: ING. MARCOS TOBAR MORAN HORAS PRESENCIALES: 40 H AÑO: 2010 DÍAS: LUNES A JUEVES AULA: B CODIGO: CREDITOS: 3 HORAS NO PRESENCIALES: 80 H PERÍODO: INTENSIVO I HORARIO: 18:00 – 19:15 Fecha elaboración syllabus: 11/01/2010 1.- DESCRIPCIÓN El profesional de Ingeniería en Sistemas telecomunicaciones y electrónica debido al avance de la tecnología debe tener conocimientos de Hardware como son los circuitos integrados de pequeña, mediana, gran escala y elementos de memoria que se utilizan para construir sistemas digitales con lógica secuencial. Para ello debe tener una comprensión profunda de la forma en la que trabajan los sistemas digitales y ser capaz de aplicar sus conocimientos al análisis y detección de fallas de cualquier sistema digital en lo que respecta a circuitos lógicos secuenciales y sistemas que manejan un mayor numero de variables de control. El principal objetivo de la asignatura es el análisis, diseño e implementación de cualquier sistema digital, especialmente de sistemas de múltiple entrada-múltiple salida. El estudiante aprenderá a interconectar módulos de construcción (circuitos integrados de pequeña, mediana y gran escala) que funcionaran bajo la supervisión de un controlador secuencial que coordinara las diferentes acciones preestablecidas por un algoritmo de control con la finalidad de lograr un determinado trabajo. 2.- JUSTIFICACIONES Incluir temas de utilidad como análisis de circuitos secuenciales desde sus elementos mas simples hasta la implementación de circuitos de una mayor complejidad justifican el dictado de la misma con la finalidad de ampliar la madurez en el análisis y diseño de estas maquinas que harán que el estudiante este al tanto de las nuevas tecnologías en el diseño digital así como la utilización de software para garantizar su correcto funcionamiento 3.- OBJETIVOS 3.1. OBJETIVO GENERALES Proporcionar una visión global de los circuitos integrados digitales de lógica secuencial de pequeña y mediana escala, como son los elementos básicos de memoria la celda binaria flip flop así como elementos que cumplen una función especifica como los registros de desplazamiento universal, contadores y memorias con una visión somera del estado de desarrollo actual de esta tecnología para la implementación de circuitos secuenciales en forma optima . 3.2. OBJETIVOS ESPECIFICOS Conocer las características especiales (eléctricas y físicas) de los principales integrados de pequeña y mediana escala Analizar circuitos digitales elementales donde se usan la sincronización utilizando osciladores y circuitos de reloj. Poder diseñar circuitos secuenciales sencillos Conocer los elementos necesarios para polarizar en forma adecuada los elementos mencionados para lograr un funcionamiento óptimo en los circuitos. Poder resolver con el mismo grado de dificultad de los problemas resueltos en clase y de los enviados como deber. 4. COMPETENCIAS - Desarrollar una comprensión clara de los diferentes elementos básicos secuenciales para la implementación y el diseño de diferentes tipos de flip flop y utilizarlos en la implementación de conversión de flip flop cuando no se encuentren en el mercado. - Desarrollar análisis y diseño de cualquier circuito secuencial utilizando los diagramas de estado y a la vez reglas que ayuden a optimizar el diseño final del circuito - Desarrollar la implementación de circuitos digitales secuenciales mas complejos utilizando las técnicas de lenguaje RTL y los diagramas ASM que son la base para el diseño de cualquier sistema digital secuencial en forma optima 5. CONTENIDO PROGRAMÁTICO SESIONES SESIÓN 1 11/01/ 2010 SESIÓN 2 12/01/2010 COMPETENCIAS Desarrollar una comprensión clara de los diferentes elementos básicos secuenciales para la implementación y el diseño de diferentes tipos de flip flop y utilizarlos en la implementación de conversión de flip flop cuando no se encuentren en el mercado UNIDADES / CONTENIDOS Unidad 1: Fundamentos de la maquina secuencial SESIÓN 3 13/01/2010 SESIÓN 4 14/01/2010 Presentación de la asignatura. Entrega del programa y explicación de los criterios de evaluación al alumno. Presentación de textos guías y complementarios. Generalidades Conceptos de memoria. La celda binaria Tarea: Ejercicios Propuestos Los Flip Flop Tarea: Desarrollar ejercicios propuestos en clases. Revisión de los E.P. en la clase anterior.(evaluación en el pizarrón). Los circuitos de reloj Tarea: Ejercicios propuestos en clases. HORAS NO PRESENCIALES Investigar sobre memoria y celda binaria EVALUACIÓN Participación en clases Investigar sobre los Flip Flops Participación en clases Investigar sobre Circuitos de reloj Participación en clases Investigar sobre los tipos de Flip Flop Participación en clases SESIÓN 5 18/01/2010 SESIÓN 6 19/01/2010 SESIÓN 7 20/01/2010 SESIÓN 8 21/01/2010 SESIÓN 9 25/01/2010 SESIÓN 10 26/01/2010 SESIÓN 11 27/01/2010 Desarrollar análisis y diseño de cualquier circuito secuencial utilizando los diagramas de estado y a la vez reglas que ayuden a optimizar el diseño final del circuito. Los tipos de Flip Flop: El Flip Flop SET/RESET, El Flip Flor D , Desarrollo de ejercicios en clases. Tarea: Ejercicios propuestos en clases. Preparación para la lección escrita próxima clase Lección escrita en clases. Flip Flop T, Flip Flop J-K Tarea: Estudio y lectura de los temas tratados en clases. Tiempo estimado No presencial: Estudio y lectura. Conversión de Flip Flop Ejercicios. Tarea: Desarrollar E.P. en clases. Trabajo en equipo. Desarrollo de E.P. (recoger próxima clase) Unidad 2: Análisis y diseño secuencial El diagrama de estado Ejercicios y trabajos en clases Análisis de circuitos secuénciales sincrónicos. Tarea: Desarrollar EP. Lección escrita en clases. Maquinas secuenciales de estado finito Procedimiento tradicional para el diseño secuencial sincrónico Tarea: Desarrollar E.P. y entregar semana antes del examen Participación en clases Evaluación practica en clases. Investigar sobre conversión de Flip Flop Participación en clases Investigar estado de Participación en clases Investigar sobre Análisis de circuitos secuénciales sincrónicos Participación en clases Investigar sobre maquinas secuénciales de estado finito Participación en clases Investigar sobre procedimiento tradicional para el diseño secuencial sincrónico Investigar sobre reglas para reducir estado Participación en clases sobre los diagramas Participación en clases SESIÓN 12 28/01/2010 SESIÓN 13 01/02/2010 SESIÓN 14 02/02/2010 SESIÓN 15 03/02/2010 SESIÓN 16 04/02/2010 SESIÓN 17 08/02/2010 SESIÓN 18 09/02/2010 SESIÓN 19 10/02/2010 Reglas de reducción de estado. Clase Práctica. Tarea: Ejercicios propuestos Minimización del decodificador de estado siguiente Desarrollo de ejercicios Investigar sobre minimización decodificador de estado siguiente del Participación en clases Lección escrita en clases. Continuación. Ejercicios con vistas a prepararse para el examen. Tarea: Estudio para el examen del primer parcial. Participación en clases EXAMEN PRIMER PARCIAL Revisión con los estudiantes del examen. Tarea: Lectura independiente del texto , revisión de los temas tratados, continuación Contadores: Tarea: Ejercicios propuestos Diseño de contadores en modo simple Contadores multimodo. Tarea: Ejercicios propuestos. Tiempo estimado No presencial: Participación en clases Investigar sobre contadores EXAMEN PRIMER PARCIAL Participación en clases Investigar sobre contadores en modo simple Participación en clases Investigar sobre contadores en modo múltiple Participación en clases Participación en clases SESIÓN 20 11/02/2010 SESIÓN 21 15/02/2010 SESIÓN 22 16/02/2010 SESIÓN 23 17/02/2010 SESIÓN 24 18/02/2010 SESIÓN 25 22/02/2010 Desarrollar la implementación de circuitos digitales secuenciales mas complejos utilizando las técnicas de lenguaje RTL y los diagramas ASM que son la base para el diseño de cualquier sistema digital secuencial en forma optima Investigar sobre los contadores de Rizo. Participación en clases Contadores de rizo. Tarea: Realizar ejercicios propuestos de clases Investigar sobre los contadores de anillo Participación en clases 1. Recoger EP(evaluativo) Lección escrita. Contadores de anillo Investigar sobre desplazamiento de Participación en clases Registros de desplazamiento. Tarea: Realizar ejercicios propuestos de clases Investigar sobre el procesador de datos. Lenguaje RTL Participación en clases Investigar sobre el controlador sistema. Diagrama ASM del Participación en clases Investigar sobre implementación controladores. Método clásico de Participación en clases Investigar sobre implementación de controladores. Método de un Flip Flop por estado Participación en clases Unidad 3: Diseño de sistemas de múltiple entrada múltiple salida El procesador de datos Lenguaje RTL SESIÓN 26 23/02/2010 Ejercicios de los temas tratados en las últimas dos clases. Ejemplos a desarrollar en clases. Ejercicios en clases. Controlador del sistema Diagrama ASM Tarea: Desarrollar E.P., para entregar el día del examen final. Prepararse para lección escrita clase próxima. Lección escrita. Implementación del controlador. Método Clásico Tarea: Estudiar lo visto en clases registros SESIÓN 27 24/02/2010 SESIÓN 28 25/02/2010 SESIÓN 29 01/03/2010 SESIÓN 30 02/03/2010 Implementación del controlador método de un Flip Flop por estado Ejercicios en clases. Tarea: Desarrollo de E.P. Entregar día del examen final (evaluativo) Utilización de decodificadores y multiplexores en la implementación de controladores Tarea: Desarrollo de E.P. (adicionar al deber final) Estudio independiente con vistas a la lección escrita próxima clase. Lección escrita. Implementación del controlador utilizando contadores. Tarea: Desarrollo de E.P. (adicionar al deber final) Estudio independiente con vistas al examen final. Implementación del controlador utilizando registros de desplazamiento Clase práctica. Desarrollo de ejercicios varios con vistas a prepararse para el examen final. Tarea: Estudio independiente con vistas al examen final. Investigar sobre el uso de decodificadores y multiplexores en los controladores Participación en clases Investigar sobre el uso de contadores en la implementación del controlador Participación en clases Investigar sobre el uso de registros de desplazamiento en la implementación del controlador Participación en clases Participación en clases SESIÓN 31 03/03/2010 SESIÓN 32 04/03/2010 Clase práctica. Desarrollo de ejercicios varios con vistas a prepararse para el examen final. Tarea: Estudio independiente con vistas al examen final. Participación en clases EXAMEN SEGUNDO PARCIAL 6. METODOLOGÍA La resolución de problemas será compartida entre el profesor y el alumno, incluyendo sugerencias que orienten al estudiante y conlleven al intercambio de opiniones con el fin de que el alumno pueda resolver los problemas por sí solo. Se enviarán tareas por unidad las cuales serán evaluadas el día de entrega de las mismas. Las tareas y trabajos que no sean entregadas en el día indicado serán receptadas, pero penalizadas con un 10% de la nota total por cada día de clase de atraso en la entrega, teniendo como penalización máxima un 50%. Dentro de las sesiones se contemplan clases de repaso para atender los problemas suscitados con las tareas enviadas. 7. EVALUACIÓN 7.1 Criterios de Evaluación La nota de evaluación en la materia se distribuye de la siguiente manera: 50% el examen y el 50% restante corresponde a lecciones, talleres, deberes, trabajos en clases. 7.2 Indicadores de Desempeño La participación de los estudiantes en el normal desenvolvimiento de las clases tanto en preguntas y respuestas por parte del catedrático denota un desarrollo consistente en el aprendizaje, por lo que el curso será participativo y activo. La lecciones y talleres serán evaluadas con fecha de anticipación. Los deberes se presentarán en fecha asignada. 7.3 Ponderación La calificación del Primer Parcial es de la siguiente manera: Trabajos 10/10 Deberes 30/30 Lecciones 60/60 Nota de Actividades 100/100 Examen 100/100 Promedio 100/100 Lecciones 60/60 Nota de Actividades 100/100 Examen 100/100 Promedio 100/100 Las calificación del Final es de la siguiente manera: Trabajos 10/10 Deberes 30/30 8. BIBLIOGRAFÍA 8.1. BÁSICA Texto: Análisis y diseño de circuitos lógicos digitales de Víctor Troy Prentice Hall Apuntes personales ( folleto) Engineering Approach to digital design por William Fletcher Prentice Hall 8.2. COMPLEMENTARIA Sistemas digitales principios y aplicaciones por Ronald Tocci 6 edición Prentice Hall Principios de diseño lógico digital Norman baladanian y Bradley Carlson CECSA Sistemas digitales de Morris Mano 9. DATOS DEL CATEDRÁTICO NOMBRE: TITULO DE PREGRADO: TITULOS DE POSTGRADO: E-Mail: Marcos Tobar Moran Ingeniero Eléctrico especialización Electrónica maestrante del MSIG ESPOL – VI promoción, especialización e-commerce ingtobar@hotmail.com _____________________________ Ing. Antonio Cevallos Decano ______________________________ Ing. Marcos Tobar Moran Profesor