Sistemas Digitales, 2012 Certamen 3

Anuncio

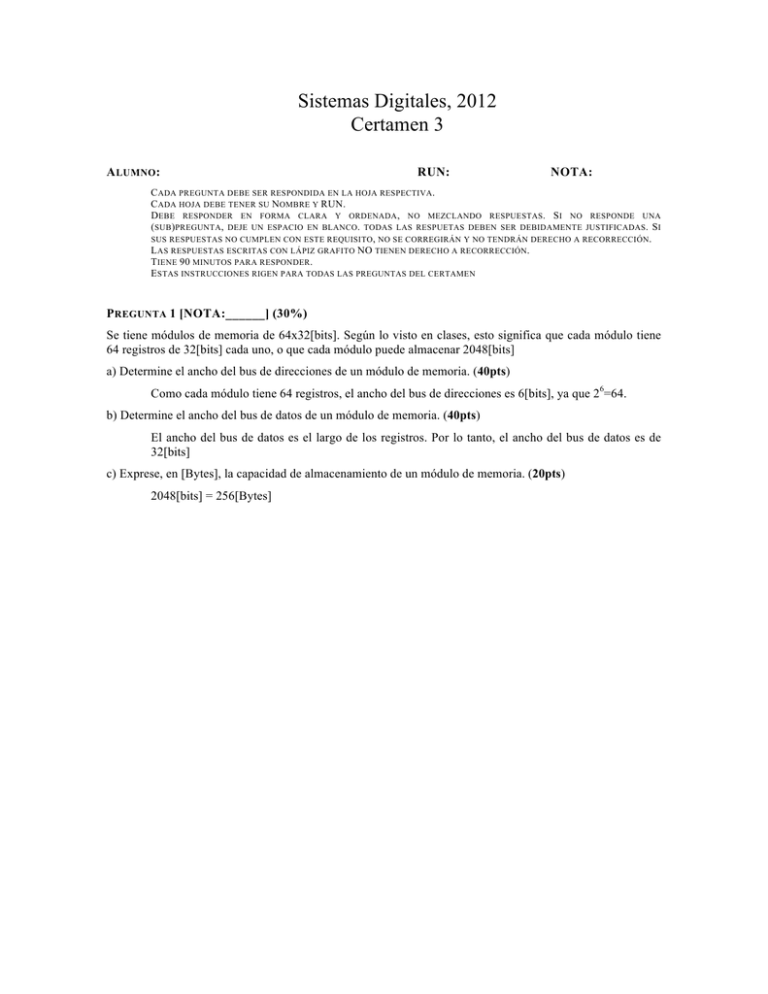

Sistemas Digitales, 2012 Certamen 3 A LUMNO : RUN: NOTA: C ADA PREGUNTA DEBE SER RESPONDIDA EN LA HOJA RESPECTIVA . C ADA HOJA DEBE TENER SU N OMBRE Y RUN. D EBE RESPONDER EN FORMA CLARA Y ORDENADA , NO MEZCLANDO RESPUESTAS . S I NO RESPONDE UNA ( SUB ) PREGUNTA , DEJE UN ESPACIO EN BLANCO . TODAS LAS RESPUETAS DEBEN SER DEBIDAMENTE JUSTIFICADAS . S I SUS RESPUESTAS NO CUMPLEN CON ESTE REQUISITO , NO SE CORREGIRÁN Y NO TENDRÁN DERECHO A RECORRECCIÓN . L AS RESPUESTAS ESCRITAS CON LÁPIZ GRAFITO NO TIENEN DERECHO A RECORRECCIÓN . T IENE 90 MINUTOS PARA RESPONDER . E STAS INSTRUCCIONES RIGEN PARA TODAS LAS PREGUNTAS DEL CERTAMEN P REGUNTA 1 [NOTA:______] (30%) Se tiene módulos de memoria de 64x32[bits]. Según lo visto en clases, esto significa que cada módulo tiene 64 registros de 32[bits] cada uno, o que cada módulo puede almacenar 2048[bits] a) Determine el ancho del bus de direcciones de un módulo de memoria. (40pts) Como cada módulo tiene 64 registros, el ancho del bus de direcciones es 6[bits], ya que 26=64. b) Determine el ancho del bus de datos de un módulo de memoria. (40pts) El ancho del bus de datos es el largo de los registros. Por lo tanto, el ancho del bus de datos es de 32[bits] c) Exprese, en [Bytes], la capacidad de almacenamiento de un módulo de memoria. (20pts) 2048[bits] = 256[Bytes] Sistemas Digitales, 2012 Certamen 3 P REGUNTA 2 [NOTA:______] (35%) Se requiere diseñar un banco de memoria de 4[KiBytes], cuya palabra de memoria sea de 32[bits]. Esto significa que desde el punto de vista de almacenamiento, este banco de memorias se comporta como un módulo de memoria de Nx32[bits], siendo N la cantidad de registros totales del banco de memoria. Se debe implementar en base a M módulos de 64x32[bits] a) Determine el valor numérico de M. (20pts) M es la cantidad de módulos. Como cada módulo almacena 256[Bytes] y se necesitan 4[KiBytes], entonces: 4 [ KiBytes ] 2 2 ! 210 [ Bytes ] M= = = 2 4 = 16 8 256[Bytes] 2 [ Bytes ] b) Determine el valor numérico de N. (20pts) N representa la cantidad de registros que tiene el banco de memoria. Hay dos formas de obtenerlos (como mínimo): Justificación 1: Como cada módulo tiene 64 registros, y se necesitan 16 módulos, entonces N = 64 !16 = 1024 Justificación 2: Como el banco de memoria es de 4[KiBytes] y cada registro es de 4[Bytes], entonces N= 4 [ KiBytes ] 2 2 ! 210 [ Bytes ] = = 210 = 1024 4[Bytes] 2 2 [ Bytes ] c) Determinar el ancho del bus de direcciones del banco de memoria. (20pts) Como hay 1024 registros, el bus de direcciones es de 10[bits], ya que 210=1024. d) Determine el ancho del bus de datos del banco de memoria. (20pts) El ancho del bus de datos del banco de memoria es el mismo que el bus de datos de cada módulo, esto es, 32[bits] Sistemas Digitales, 2012 Certamen 3 P REGUNTA 3 [NOTA:______] (35%) Se requiere diseñar un banco de memoria Nx64[bits], en base a M módulos de 64x32[bits]. Un esquema que hace posible esto se muestra en la figura 3.1. Básicamente, se unen en paralelo las salidas de dos memorias de 64x32[bits] para hacer una memoria de 64x64[bits]. CS Dir Memoria 1 S 64 x 32 CS 32 (+). 32 (-) Memoria 2 S 64 x 32 Dir 64 bus de direcciones + CS Dir Memoria 3 S 64 x 32 CS 32 (+) 32 (-) Memoria 4 S 64 x 32 Dir 64 bus de datos + CS Memoria M-1 S 64 x 32 Dir IN 32 (+) CS 32 (-) Memoria M S 64 x 32 Dir 64 OUT + Decodifi cador Figura 3.1 a) Determine la relación que existe en M (número de modulos de 64x32) y N (número de registros del banco de memoria) (40pts) Si hay M módulos de 64x32[bits], entonces el banco de memoria es de N=64•M/2 = 32M[registros] b) Si hay 16 módulos de 64x32[bits], determine el ancho del bus de direcciones. (30pts) Si hay 16 módulos, entonces el banco de memoria tiene 512 registros. Para direccionar esos registros, se necesitan 9 [bits]. c) Si hay 16 módulos de 64x32[bits , determine el ancho del bus de entrada al decodificador. (30pts) Como cada módulo de 64x32[bits] se puede direccionar con 6 [bits], y el ancho del bus de direcciones es de 9[bits], entonces el ancho de bus de entrada al deco es de 3[bits]