Uma Nova Arquitetura de FPGA para Aplicações DSP Integrando

Anuncio

Uma Nova Arquitetura de FPGA para Aplicações DSP

Integrando Capacidades de BIST

Alex Gonsales*

Marcelo Lubaszewski**

*PPGC – Instituto de Informática

UFRGS

P.O. Box 15064 – Porto Alegre, RS

91501-970 – Brazil

{alexdg,erika}@inf.ufrgs.br

Luigi Carro**

Érika Cota*

** PPGEE – Dept. Engenharia Elétrica

UFRGS

Av. Osvaldo Aranha, 103 – Porto Alegre, RS

90035-190 – Brazil

{luba,carro}@iee.ufrgs.br

O projeto de sistemas em silício (Systems-on-Chip –

SOC) trouxe aos projetistas um novo desafio em termos

de teste e verificação. Problemas relacionados ao teste

de diversos blocos em um SOC são bem conhecidos

[6,7] e algumas soluções tem sido propostas

recentemente na literatura [8,9]. A partir das abordagens

de teste propostas, está claro que o uso de técnicas de

projeto visando o teste são essenciais para um teste

efetivo. Técnicas de auto-teste embutido (Built-In Self

Test - BIST) têm sido usadas para teste interno de

blocos embutidos ou núcleos [10,11].

A utilização de BIST mantém a proteção de

propriedade intelectual de um núcleo sem perda da

qualidade do teste. Todavia, esta característica pode vir

com um custo proibitivo em termos de área, como

mostrado em [12]. Por outro lado, diferentes

controladores de BIST podem normalmente serem

extraídos a partir do núcleo sem perda da proteção da

propriedade intelectual [13].

Dentro desse contexto, este trabalho discute alguns

aspectos do projeto de uma nova arquitetura de FPGA

otimizada para aplicações DSP e BIST. Esse FPGA

possuirá células específicas, composta de estruturas que

permitam a implementação de filtros FIR de alto

desempenho bem como a implementação de funções de

teste a serem usadas pelos núcleos no sistema. As

operações de BIST serão implementadas de uma

maneira seqüencial, uma a cada vez.

Para a realização deste trabalho, primeiramente foi

realizada uma avaliação da área necessária para

implementação de BIST dedicado para memórias RAM

e ROM, bem como a implementação de Geradores de

Padrões de Teste Pseudo-aleatório. Também foi

realizada uma análise da área requerida para a

implementação dedicada de filtros FIR. Em seguida,

esses mesmos circuitos (FIR e BIST) foram

implementados no FPGA aqui proposto e num

dispositivo FLEX10k da Altera [14]. Uma comparação

da área requerida por cada implementação foi realizada,

mostrando as vantagens de utilização do BiFi-FPGA.

Para ilustrar a idéia da proposta, na figura 1 pode-se

verificar a possível redução de área do sistema devido ao

agrupamento das funções de teste e do filtro FIR na

mesma área reconfigurável.

Resumo

Este trabalho apresenta uma nova arquitetura de

FPGA (BiFi-FPGA) com o objetivo de atender as

funções de processamento digital de sinais e teste dos

sistemas em silício. Além das vantagens de

reconfigurabilidade de um FPGA, a arquitetura

proposta tem a possibilidade de reuso de hardware para

teste enquanto mantém o nível de desempenho requerido

pelas aplicações correntes. Este artigo apresenta o

modelo do FPGA proposto juntamente com resultados

experimentais preliminares que mostram claramente as

vantagens desta técnica de otimização.

1. Introdução

Os sistemas eletrônicos digitais estão sendo cada vez

mais utilizados em aplicações de telecomunicações,

telefonia celular, processamento de voz, instrumentação,

biomédica e multimídia. A maioria destas aplicações

requer algum tipo de processamento de sinal. Essa

função normalmente é executada por um bloco digital

devido as suas vantagens em relação a um bloco

analógico, tais como maior desempenho e maior grau de

automação (facilidade projeto/síntese).

A tarefa de processamento de sinais é muito cara

computacionalmente. Filtros FIR por outro lado, chegam

a representar 80% do poder de computação requerido

pela maioria das aplicações de telecomunicações [1].

Logo, os circuitos digitais que atendem esse tipo de

aplicação devem atender os requisitos de alto

desempenho [2,3]. Consequentemente, a presença de

circuitos digitais otimizados para esse tipo de tarefa nos

sistemas atuais é muito usual.

A utilização dos FPGAs disponíveis no sistema

como recurso extra para processamento de sinal tem

sido estudado recentemente. Porém, os FPGAs

tradicionais não são adequados a implementação de tais

aplicações [2-4], principalmente devido a restrições de

desempenho e área. Com isso, têm surgido diversas

propostas de FPGAs otimizados para aplicações

intensivas em partes operativas ou funções de

processamento digital de sinais (Digital Signal

Processing – DSP) [1-5].

1

Este artigo está organizado como segue: A seção 2

apresenta alguns trabalhos relacionados com arquiteturas

reconfiguráveis e teste. Na seção 3 são analisadas as

estruturas de hardware necessárias para a

implementação de filtros FIR e dos testes abordados

neste trabalho. O FPGA proposto é apresentado na seção

4 enquanto que na seção 5 são mostrados alguns

resultados experimentais. Finalmente, na seção 6 são

apresentadas as conclusões e trabalhos futuros.

FIR and BIST

BIST

SOC

SOC

RAM

ROM

FIR

CC

RAM

ROM

FPGA

CC

Figura 1 – (a) BIST dedicado e (b) BIST reconfigurável.

2. Trabalhos Anteriores

Diversas propostas de arquiteturas reconfiguráveis

para aplicações específicas podem ser encontradas na

literatura [1-5]. Muitas delas estão relacionadas com

aplicações DSP, ou seja, uma arquitetura reconfigurável

otimizada para a implementação dessa classe de

aplicações [1-3].

Essas propostas diferem basicamente pela

granularidade de seus blocos programáveis, modelo de

conexões e estratégia de reconfiguração.

Cherepacha, por exemplo, propõe em [4] (DPFPGA) um FPGA para a implementação de aplicações

intensivas em partes operativas. Esse FPGA é composto

de 3 partes: memória, controle e parte operativa. Cada

parte do DP-FPGA é otimizado para implementar uma

classe de circuito (memória, controle ou parte

operativa), porém, o trabalho foca somente a parte

operativa.

Com relação a FPGAs para implementação de BIST,

existem poucos trabalhos. Renovell propõe em [15] a

criação de uma cadeia de escaneamento (Implicit Scan

Chain) nos FPGAs clássicos. Usando esta nova

arquitetura de FPGA, qualquer circuito seqüencial

implementado nesse FPGA é implicitamente escaneado

e testado.

Em [13], Carro et al propõem o uso de uma área

dedicada do sistema para a implementação das estruturas

de teste. Esta área é um FPGA (FLEX10K da Altera)

[14] usado para implementar controladores BIST. Tal

estratégia tem por objetivo a redução da área no chip

dedicada ao teste, uma vez que o mesmo hardware pode

ser reconfigurado seqüencialmente para implementar

cada um dos procedimentos de teste necessários. Além

disso, essa área dedicada pode ser reutilizada para

implementar outra função do sistema durante o modo de

operação normal do mesmo.

Verifica-se que entre as soluções correntes, ou uma

nova arquitetura de FPGA é criada para atender somente

as otimizações funcionais (DSP) ou uma arquitetura de

FPGA clássico é utilizado para implementar diferentes

soluções de teste. Todavia, a união destes dois

importantes pontos de vista não foi proposto ainda, pelo

conhecimento dos autores.

3. Estruturas de Hardware Para DSP e

BIST

Neste primeiro modelo, foram consideradas as

técnicas de teste para memórias RAM e ROM, e os

geradores de padrões de teste pseudo-aleatórios. Para

modelar as funções DSP foram considerados

inicialmente os filtros FIR.

Esta seção mostra as estruturas de hardware

necessárias para a implementação dessas aplicações.

Somente a parte operativa é analisada, uma vez que a

parte de controle e memória não estão no escopo deste

trabalho.

Essas estruturas são primeiramente descritas como

um conjunto básico de portas lógicas e blocos básicos.

Em seguida, é feita uma estimativa da área requerida

(número de transistores MOS) para sua implementação.

A tabela 1 mostra essa estimativa, onde a área é

representada em número de transistores em função do

número de bits n do bloco.

3.1 Filtros FIR

Os recursos necessários para a implementação de

filtros FIR são: multiplicadores, somadores, e blocos de

atraso (registradores) [16].

A área ocupada por um filtro FIR canônico com T

taps, n bits de dados e um multiplicador paralelo n x n

bits pode ser estimado por:

Area_fir = T(n.Array_Multiplier + 2.n.Adder + 2.n.Reg)

= T (34n2 + 96n)

(1)

Alternativamente, se um multiplicador serial do tipo

soma-desloca for utilizado, então a área ocupada pode

ser estimada por:

Area_FIR = T(n.Serial_Mult + 2.n.Adder + 2.n.Reg)

= T (80n + 56n + 40n)

= T (176n)

(2)

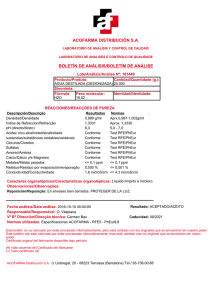

3.2 Teste de Memórias ROM

Para o teste de memórias ROM foi considerado o

algoritmo Check-Sum, o qual consiste em somar todas

as palavras da memória e comparar o resultado com um

valor pré-armazenado de uma memória sabidamente

sem defeitos. Se os dois valores forem diferentes então

um sinal de erro é ativado, indicando que a memória está

com defeito.

As seguintes estruturas são necessárias para a

implementação desse teste: um contador, um

somador/acumulador, um registrador e um comparador.

A Figura 2a mostra um exemplo de implementação

dedicada para o teste de uma memória ROM 4x16 (16

palavras de 4 bits cada). Neste exemplo, o valor do

check-sum a ser comparado é 3 (00112), necessitando os

dois inversores nas entradas da porta NOR.

Considerando d o número de linhas de dados e a o

número de linhas de endereço, a sobrecarga de área para

o circuito em questão é:

Area_rom = a(Counter) + d(Adder + Reg + NOR2)

= 48.a + 50.d

(3)

Tabela 1 – Estimativa de área para blocos básicos

Bloco

#Transistores

Counter

48.n

Adder

28.n

Array Multiplier

34.n 2

Serial Multiplier

80.n

MUX2x1

4.n

MUX4x1

12.n

Register

20.n

Shift Register

28.n

2-Input NOR (NOR2)

4.n

2-Input XOR (XOR2)

6.n

3.3 Teste Pseudo-aleatório

Várias estratégias de teste são baseadas no uso de

geradores de padrões pseudo-aleatórios, os quais podem

ser implementados por estruturas denominadas LFSR

(Linear Feed-back Shift Register) [18]. Essa mesma

estrutura pode ser utilizada tanto como um gerador de

vetores pseudo-aleatórios como um analisador de

assinaturas. A Figura 3 mostra um exemplo de LFSR de

3 bits funcionando como analisador de assinaturas.

A área ocupada por um LFSR com n bits pode ser

estimada por:

Area_lfsr = n(Reg + XOR) = 26.n

D

SET

CLR

Q

Q

D

SET

CLR

Q

Q

(5)

D

SET

CLR

Q

Q

Figura 3 – Linear Feedback Shift Register (LFSR).

4. Arquitetura do BiFi-FPGA

Para a implementação dos testes de memórias RAM,

foi considerado o algoritmo March descrito em [17].

Para o teste de uma memória RAM 4x16, a seguinte

seqüência de padrões de teste deve ser aplicado a cada

palavra da memória: 0000, 0001, 0011, 0111, 1111,

1110, 1100, 1000, 0000. Uma possível implementação

deste algoritmo é mostrada na figura 2b. A sobrecarga

de área para esta implementação é:

O BiFi-FPGA será composto de 3 partes, cada uma

otimizada para a implementação de uma classe de

circuitos (parte operativa, controle e memória) (Fig. 4).

Nesse sentido ele segue a mesma idéia proposta por

Cherepacha [4]. A diferença entre os dois trabalhos está

justamente na arquitetura da célula básica. Enquanto

aquele trabalho se detém na especificação de uma

arquitetura para a implementação de partes operativas

genéricas, este trabalho é mais específico, otimizando a

célula para a implementação de funções DSP e BIST.

Este trabalho se concentra somente no bloco parte

operativa, uma vez que a parte de controle é bem

implementada pelos FPGAs de propósito geral, tais

como Altera e Xilinx [4].

Area_ram = a(Counter) + d(Reg + ShiftReg + XOR2 +

NOR2)

=48.a +58.d

(4)

Como foi mostrado na seção 3, as seguintes

estruturas de hardware são necessárias para a

implementação das funções de DSP e BIST: somadores,

registradores, multiplicadores e portas XOR.

3.3 Teste de Memórias RAM

Normal

Address

ROM

Normal

Data

Normal

Address

Controle

RAM 4xa

Address

0

1

a

Counter

0

1

Data

a

Address

RAM

R/W

Out In

d

+

4

4

0

Counter

Shift

Register

Parte

Operativa

Figura 4 – Visão geral do BiFi-FPGA

1

Register

Error

Error

Figura 2 –Teste de memórias ROM 4x16 (a) e

RAM4x16 (b)

End

Test

Além disso, analisando-se as aplicações alvo, podese verificar que a maior parte das operações se darão

sobre dados múltiplos de 4, 8 ou 16. Consequentemente,

foi escolhida uma granularidade de 4 bits para a célula

básica.

Para a implementação da função lógica da célula,

diversas estratégias podem ser utilizadas: LUT (Look-up

Table), multiplexadores, portas lógicas, ULAs, etc.

Os FPGAs tradicionais, como Altera e Xilinx

utilizam LUTs de 4 ou 5 entradas. Uma k-LUT (LUT de

k entradas) nada mais é que uma memória com 2k bits

mais um multiplexador 2k x 1. Ela pode ser configurada

para implementar qualquer função de k entradas, o que

dá um total de (22)k possíveis funções.

No entanto, visto que nossa célula deverá

implementar somente 4 funções básicas, a escolha de

uma LUT para implementação da célula representaria

um desperdício de área. Logo, com o objetivo de

otimizações de área, projetou-se uma célula baseada em

portas lógicas (na forma de uma ULA) e

multiplexadores.

A figura 5 mostra a arquitetura da célula básica,

cujos principais componentes são: uma ULA, um

registrador, um registrador deslocador e 4

multiplexadores 2x1 de 4 bits. As entradas (inA e inB) e

as saídas (out1, out2 e out3) são de 4 bits também.

A ULA pode executar duas funções, soma e XOR bit

a bit. A operação de subtração (inA-inB) é possível

através da inversão do operando inB e configurando o

cin da ULA para receber o valor lógico 1 (um).

InA

InB

0

1

0

1

bi

0

bi-1

1

0

1

cin

oper

zout

cout

zout

cout

0

pcin

cin

zcin

SoutRMul

SinLMul

MUXout

0

1

SinL

Register

SoutR

ShiftRegLFSR

enaRegLFSR

nLdShLFSR

nLeftRight

enaReg

Out1

4

Out3

Tabela 2 – Área ocupada pela célula BiFi.

Bloco

#

#Transistores

Mux 2x1 de 1 bit

2

8

Mux 2x1 de 4 bits

4

64

ULA

1

136

Register 4-bit

1

80

ShiftRegLFSR

1

154

Latch

10

80

Flip-Flop

1

16

Inversor

5

10

NOR2

2

8

XOR2

1

6

AND2

1

6

Outros

1

6

Total

568

5. Resultados Experimentais

SinR

SoutL

4

implementação

de

somadores/acumuladores

e

contadores.

O registrador-deslocador ShiftRegLFSR pode ser

configurado como um registrador, registradordeslocador (direita ou esquerda) ou como um LFSR

configurável.

Durante

a

implementação

de

multiplicadores seriais, este registrador armazena o

operando multiplicador. O multiplicando deverá ser

fornecido pela entrada inA da célula. Esse bloco é

utilizado para a geração dos vetores durante o teste de

memórias RAM.

Além disso, esse registrador pode ser utilizado para a

implementação de técnicas de teste baseadas em scan

chain [15].

A saída não registrada (combinacional) (Out3) é

utilizada na implementação de multiplicadores paralelos.

A tabela 2 mostra o número de transistores

necessários para a implementação da célula básica.

4

Out2

= 1 bit Latch

Figura 5 – Arquitetura da Célula básica

Embora seja necessário um operador de

multiplicação, para a implementação de filtros, foi

decidido não implementar esse operador diretamente na

célula, visto que esse tipo de estrutura consome muita

área, o que iria significar um desperdício quando não se

estivesse utilizando a célula para a implementação de

filtros. Logo, foram adotadas duas estratégias utilizandose o algoritmo de Booth para a implementação de

multiplicadores:

1) Multiplicador Booth paralelo: Quatro células

implementam um multiplicador 4x4 que executa

em 1 ciclo;

2) Multiplicador Booth serial: Uma célula

implementa um multiplicador 4x4 que executa

em 4 ciclos.

O bloco register na saída Out1 é utilizado na

5.1 Mapeamento de Circuitos no BiFi-FPGA

Para validar a arquitetura proposta, um conjunto de

circuitos de benchmark foram mapeados no BiFi-FPGA.

A figura 6 mostra a implementação de BIST de uma

memória RAM4x16 (a) e uma ROM4x16 (b) utilizando

as células do BiFi-FPGA. A figura 7 mostra a

implementação de um multiplicador paralelo 4x4 bits (a)

e um filtro FIR canônico de 4 taps e 4 bits de dados (b).

5.2 Análise Comparativa de Custos

Três abordagens de projeto foram analisadas:

Implementação dedicada, implementação com FPGA

FLEX10K30 da Altera e com o BiFi-FPGA.

A tabela 3 mostra a estimativa de área ocupada por

alguns circuitos com implementação dedicada. A tabela

4 mostra os mesmos circuitos implementados no BiFiFPGA com o respectivo número de células necessárias e

área ocupada. A expressão da coluna três é calculada

pela equação 6:

Número de Transistores = 568 . Número de Células (6)

Normal

Address

ROM

Normal

Address

Accumulator

RAM

Counter

Normal

Data

Pattern

Generator

1

Counter

0

Addr

1

Tabela 3 - Implementação dedicada.

Circuito

#Transistores

1

+

0

Addr

R/W

+

+

1

Data

4

Zout

R/W

4

Out In

4

4

0

Zout

1

Zout

End Test

Control

Comparator

Control

4

Zout = Error

Comparator

4

4

Zout = Error

Figura 6 – Teste de ROM (a) e RAM (b).

MD

MR

MR0

+

+

0

0

MR1

+

0

+

0

MR2

+

0

0

48a+50d

48a+58d

80d

34d2

176d

34d2 + 96d

176d+56.log2(T)

Tabela 4 –Implementação no BiFi-FPGA.

Circuito

#Células

#Transistores

X[i]

0

0

ROM Test

RAM Test

Serial Multiplier

Array Multiplier

1 Tap FIR filter (with serial

multiplier)

1 Tap FIR filter (with array

multiplier)

*Serial FIR filter (1 serial

multiplier, T Taps)

MR3

ROM Test

RAM Test

Serial Multiplier

Array Multiplier

1 Tap Fir filter

(with serial

multiplier)

1 Tap FIR filter

(with

array

multiplier)

*Serial Fir filter (1

serial multiplier, T

Taps)

(a+2d)/4

(a+3d)/4

d/4

(d2)/4

3d/4

142a+284d

142a+426d

142d

142d2

426d

(d2+2d)/4

142d2+284d

(3d+2log2T)/4

426d+284log2T

+

+

0

4

Y[i]

Result

Figura 7 – Multiplicador Paralelo (a) e Filtro FIR (b).

Em ambas tabelas, considera-se que d (número de

linhas de dados) e a (número de linhas de endereço) são

múltiplos de 4.

A Tabela 5 mostra o número de células necessárias

para a implementação de diversos circuitos de

benchmark utilizando-se o BiFi-FPGA e dispositivos

FLEX10k30 da Altera.

Os valores da coluna BiFi foram calculados

utilizando-se as equações da Tab. 4. Para obter o

número de células necessárias no dispositivo Altera, os

mesmos circuitos foram descritos em VHDL e

sintetizados em dispositivos FLEX10k30, utilizando-se

a ferramenta MaxPlusII, que fornece o número de

células utilizadas na síntese.

Na Tabela 6 é feita uma comparação das 3

abordagens. As colunas 1 e 3 são calculadas utilizandose as equações deduzidas anteriormente (Tab. 3 e 4).

Para a estimativa da área ocupada nos dispositivos

Altera, teve-se de utilizar um artifício, visto que não é

fornecido o número de transistores nem a área ocupada

por um Logic Element dos dispositivos Altera

FLEX10K.

Analisando-se os dados fornecidos em [14], fezse uma estimativa do número de transistores necessários

para a implementação de um Logic Element (Tab 7). Foi

obtido o valor de 316 transistores, o qual foi utilizado

para se calcular os valores da coluna 3 da Tabela 7.

Tabela 5 – Número de células necessárias.

Bloco

FLEX10k

BiFi

Mult. Serial 8x8

38

2

Mult. Paralelo 8x8

64

16

ROM 8x256 BIST

20

6

RAM 8x256 BIST

31

8

RAM 8x4k BIST

35

9

RAM 16x256 BIST

53

14

RAM 16x4k BIST

57

15

LFSR (8bits)

25

2

LFSR (32bits)

97

8

Filtro Paralelo 8 bits (16

468*

320

Taps)

Filtro Serial 8 bits (16

272*

96

Taps)

* Fonte: Altera [19].

É possível verificar (Tab. 6) que em média, o BiFiFPGA ocupa 6 vezes mais área que uma implementação

dedicada. Esses valores também coincidem com aqueles

obtidos por [2]. Com relação a dispositivos FLEX10k, o

BiFi-FPGA tem um ganho de área de 50%, não se

levando em conta a conexão.

Tabela 6 – Comparação do número de transistores.

Bloco

Dedicado FLEX10k BiFi

Mult Serial 8x8

640

12008 1136

Mult Paralelo 8x8

2176

20224 9088

ROM 8x256 BIST

784

5520 3408

RAM 8x256 BIST

848

8556 4544

RAM 8x4k BIST

1040

9660 5112

RAM 16x256 BIST

1312

14628 7952

RAM 16x4k BIST

1504

15732 8520

LFSR (8 bits)

208

7900 1136

LFSR (32 bits)

832

30652 1136

Filtro Paralelo 8 bits

47104

147888 18176

(16 Taps)

0

Filtro Serial 8 bits (16

22528

85952 54528

Taps)

Tabela 7 - Estimativa para um Logic Element Altera.

Bloco

#Transistores

5 MUX2x1

20

1 Flip-Flop

24

1 LUT (4-Input)

128+60=188

(16 latchs + 1 MUX16x1)

Clear/Reset Logic

26

Cascade Chain

12

2-Input OR

6

5-bit Latch (programação)

40

Total

316

6. Conclusões e Trabalhos Futuros

Neste artigo foi apresentada uma nova arquitetura de

FPGA (BiFi-FPGA) destinado a implementação de

funções DSP e BIST. Através dos diversos circuitos de

benchmark mapeados nesse FPGA, foi possível verificar

as vantagens de sua utilização em relação a FPGAs

tradicionais (FLEX10k).

Como trabalhos futuros, estão sendo estudados os

detalhes da arquitetura de conexões, o método de

reprogramação bem como o desenvolvimento de um

software de síntese para o BiFi-FPGA.

7. Referências

[1] BELLILE, O.; DUJARDIN, E. Architecture of a

Programmable FIR Filter Co-Processor. In IEEE

International Symposium on Circuits and Systems (ISCAS),

1998. p. 433-436.

[2] KAVIANI, A.; VRANESIC, D.; BROWN, S.

Computational Field Programmable Architecture. Custom

Integrated Circuits Conference (CICC98), Santa Clara,

CA, May 1998.

[3] CHEN, C.; RABAEY, J. A Reconfigurable Multiprocessor

IC for Rapid Prototyping of Algorithmic-Specific HighSpeed DSP Data Paths. In: IEEE Journal of Solid-State

Circuits, v.27, n.12, p.1895-1904. Dec. 1992.

[4] CHEREPACHA, D. A Field-Programmable Gate Array

Architecture Optimized for Datapaths. Master Thesis of

Applied Science. Graduate Department of Electrical and

Computer Engineering. University of Toronto. Canada.

1994.

[5] WANG, Q. An Array Architecture for Reconfigurable

Datapaths. Master Thesis of Applied Science. University

of Toronto, 1993.

[6] GUPTA, R. K.; ZORIAN, Y. Introducing Core-Based

System Design. In IEEE Design & Test of Computers,

October-December, n. 4, v.13, 1997, p. 15-25.

[7] ZORIAN, Y. Test Requirements for Embedded Core-based

Systems and IEEE P1500, In International Test

Conference, September, 1997, p. 191-199.

[8] MARINISSEN, E.J, et al. Towards a Standard for

Embedded Core Test: an Example. In International Test

Conference, October, 1999, p. 616-627

[9] CHAKRABARTY, K. Design of System-on-a-Chip Test

Access Architectures Using Integer Linear Programming.

In VLSI Test Symposium, April, 2000, p. 127-134.

[10] RAVI, S.; JHA, N. K.; LAKSHMINARAYANA, G.

TAO-BIST: A Framework for Testability Analysis and

Optimization of RTL Circuits for BIST. In VLSI Test

Symposium, 1999, p. 398-406.

[11] KIEFER, G.; WUNDERLICH, H-J. Deterministic BIST

with Multiple Scan Chains. In International Test

Conference, October, 1998, p. 910-917.

[12] COTA, E.; KRUG, M.; LUBASZEWSKI, M.; CARRO,

L.; SUSIN, A.A. Implementing a Self-Testing 8051

Microprocessor In 12th Symposium on Integrated Circuits

and Systems Design (SBCCI), 1999, Natal, p. 202-205.

[13] CARRO, L.; AGOSTINI, L.; PACHECO, R.;

LUBASZEWSKI, M. Using Reconfigurability Features to

Break Down Test Costs: a Case Study. In: 1st IEEE Latin

American Test Workshop, Rio de Janeiro, 2000. p. 209214.

[14] ALTERA. The altera advantage. San Jose: Altera

Corporation, 1995. 679 p.

[15] RENOVELL, M.; et. al. IS-FPGA: A New Symmetric

FPGA Architecture with Implicit SCAN. In International

Test Conference, November 2001.

[16] PIRSCH, Peter. Architectures for Digital Signal

Processing. Chichester, England: John Wiley. 1998.

[17] TREUER, R.; AGARWAL, V. Built-in Self-Diagnosis for

Repairable Embedded RAMs. In IEEE Design & Test of

Computers, v.10, n.2, p.24-33. June 1993.

[18] ABRAMOCIVI, M.; Digital Systems Testing and

Testable Design. New York: IEEE, c1990. 652 p.

[19] ALTERA. Implementing FIR Filters in FLEX Devices.

Altera Corporation, Application Note 73. Feb. 1998.