Dise˜no, Implementación y Evaluación de un procesador multi

Anuncio

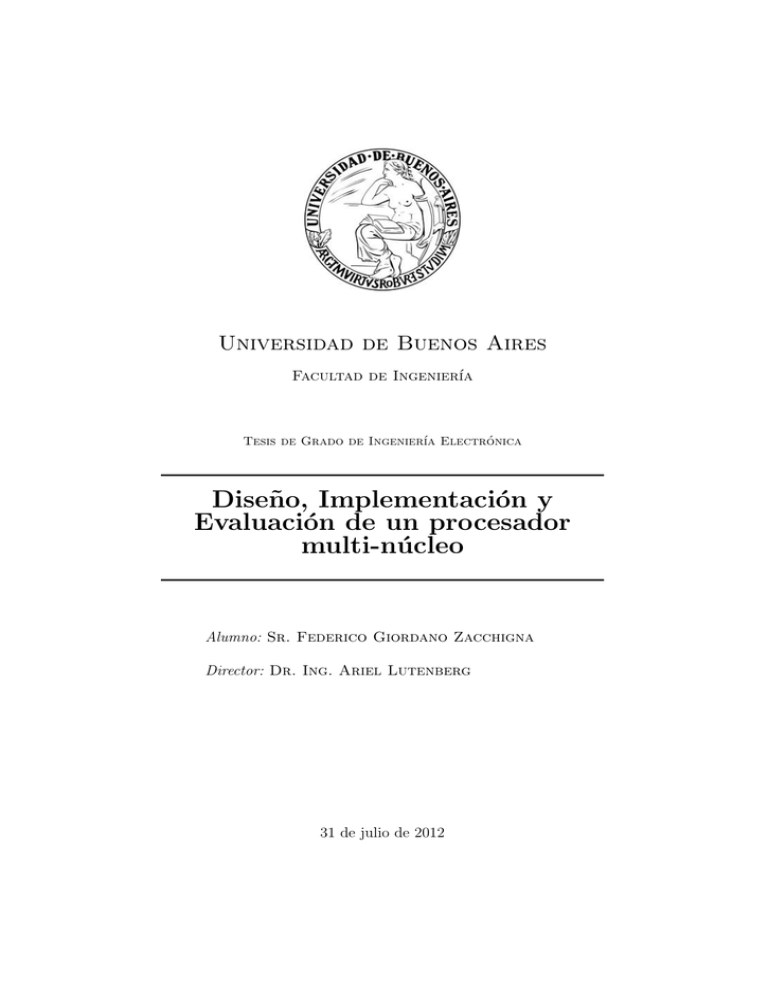

Universidad de Buenos Aires

Facultad de Ingenierı́a

Tesis de Grado de Ingenierı́a Electrónica

Diseño, Implementación y

Evaluación de un procesador

multi-núcleo

Alumno: Sr. Federico Giordano Zacchigna

Director: Dr. Ing. Ariel Lutenberg

31 de julio de 2012

i

A mi familia

ii

iii

Resumen y motivación del presente trabajo

En este trabajo se presenta una implementación de un procesador multinúcleo. El mismo esta basado en el procesador Plasma, que es un procesador de

código libre, simple que ha sido utilizado para la realización de varios proyectos

y pruebas, y que esta basado en la arquitectura de instrucciones MIPS. El

procesador ha sido objeto de estudio en varios trabajos, entre los que se cuentan

trabajos realizados por integrantes de nuestro grupo en dónde se estudia su

funcionamiento bajo efectos de radiación e interferencia electromagnética. En la

actualidad se desea continuar con esta lı́nea de investigación sobre procesadores

multi-núcleos y por eso surge la necesidad de implementar este procesador. Las

caracterı́sticas antes nombradas sobre el procesador Plasma, son ideales para

la realización de este trabajo. El sistema plasma multi-núcleo tiene distintas

aplicaciones directas, entre ellas:

Sistemas tolerantes a fallas utilizables en ambientes de alta interferencia

electromagnética y expuestos a radiación no ionizante, para aplicaciones

en sistemas de seguridad de reactores nucleares y sistemas de control y

navegación de satélites y vehı́culos espaciales. Este tema es de especial

interés hoy en dı́a para instituciones como CONAE, CNEA e INVAP.

Investigaciones cientı́ficas relacionadas con el estudio de los efectos de la

radiación y la interferencia electromagnética sobre los FPGA’s donde se

utilice una versión funcional de un softcore que sirva para realizar mediciones y sacar conclusiones sobre los efectos que estos fenómenos tienen

sobre los dispositivos.

Desarrollos de sistemas multi-núcleos parametrizables mixtos (Asymetric

Multicore Architecture) para aplicaciones de alto rendimiento, donde se

implementan micros óptimos para distintos procesos, por ejemplo, ejecución de RTOS, procesamiento de señales, GPU’s, comunicaciones, etc.

Un objetivo importante en la implementación del procesador multi-núcleo

que se realiza en este trabajo es que sea de forma tal que se puedan instanciar

un número genérico de núcleos durante el proceso de sı́ntesis, y las partes más

relevante del diseño de la arquitectura del procesador son la arquitectura de la

memoria, la memoria cache y la comunicación entre los distintos núcleos. A lo

largo del trabajo se detallan los principales factores que influyen sobre el diseño

del mismo. También se muestran las principales complicaciones que aparecen

y las soluciones a las mismas. Se muestran los detalles de su implementación

en VHDL. Se realizan pruebas del mismo en un kit Nexys2 de Digilent, basado

en una FPGA Xilinx Spartan3E-1200. Finalmente se presentan los resultados

obtenidos.

iv

v

Agradecimientos

En primer lugar, agradezco al Laboratorio de Sitemas Embebidos de la Universidad de Buenos Aires, lugar en el cual fue llevado a cabo el presente trabajo.

Agradezco a su director y mi tutor, el Dr. Ing. Ariel Lutenberg, por el apoyo

brindado. Agradezco también a Lucas Chiesa por la ayuda que me brindó al

realizar el trabajo.

Agradezco especialmente a los miembros del jurado, el Ing. Juan Manuel

Cruz, el Ing. Nicolás Alvarez, y el Ing. Fabián Vargas miembro de la Pontifı́cia

Universidade do Rio Grande do Sul (PUCRS), por ceder parte de su tiempo

para evaluar el presente trabajo.

Parte del desarrollo de este trabajo de tesis tuvo lugar en el Institut für Datentechnik und Kommunikationsnetze (IDA) de la Universidad Técnica Braunschweig. Agradezco a su director Peter Rüffer, y a mis compañeros del laboratorio Mark y Mustafa. Agradezco al DAAD y al Ministerio de Educación

de la República Argentina por brindarme esta posibilidad, al darme una beca.

Agradezco a los integrantes del programa ALE-ARG del DAAD, Agustin Rosembaum, Alejando Rodriguez, Eliseo Rocchetti, Federico Beltzer, Lucas Claramonte, Mauro Calabria, Ariel Malawka, Sofı́a Carolina Visintini. Agradezco

a todas las otras personas que formaron parte de mi vida mientras estuve en

Alemania, Jose Alejandro Diaz Vides, Ismael Holgueras de Lucas, Dani Umpierrez Corona, Mariana Almeida Ribeiro, Audrey Segura Medina, Valerio Roger

Lasso, José Rivero Rodrı́guez, Maria y Angela Cildoz Guembe. Y agradezco especialmente a aquellos con quienes logre tener una afinidad especial durante mi

estadı́a en Alemania, personas que me ayudaron mucho con su compañia y apoyo en los momentos difı́ciles, Sergio Medina, con quien compartı́ un tiempo en

Parı́s, Mariel Figueroa, Bruno Strappa, Bruno Emmanuel Rossi, Mari Antber,

Ana Rodriguez, Juan José Baena Castillo, Belen Kistner, Miguel Mamani.

Durante los primeros cinco años y medio de carrera tuve el agrado de conocer a muchas personas con quienes trabajé en MAN Ferrostaal, a todos ellos

quiero agradecerles, Leandro Feniello, Olga Hiczuk, Alicia Hiczuk, Martin Kent,

Eduardo Kenda, Daniel Morales, Sergio Acri, Walter Allaltune, Osvaldo Preiti,

Lucas De La Canal, Marta, Romina Lepore, Daniela Islas y al resto de los integrantes.

Agradezco a todos los profesores que formaron parte de mi formación académica, a aquellos de la facultad y a aquellos del mi colegio, el Instituto Hölter Schule,

pero especialmente a mis profesores de electrónica a quienes aprecio mucho, Ing.

Rubén Saclier, Ing. Norberto Muiño, Ing. Carlos Siganotto y al Ing. Charly, y

a mis profesores de alemán especialmente a Diana, Geraldine Lorenzo, Fedor

Pellmann y muy de corazón a Juana Dartsch, quien fue por lejos mi mejor

profesora.

Agradezco a las personas que forman parte de la materia Dispositivos Semiconductores, de la cual formo parte hace ya más tres años, Mariano Garcı́a

Inza, Sebastián Carbonetto, Diego Martin, Claudio Pose, Luciano César Natale,

Gabriel Sanca y en su momento Daniel Rus.

Agradezco a todos mis compañeros de la facultad de ingenierı́a entre ellos,

Fernando Chouza, Diego Martı́n, Fabricio Alcalde, Gabriel Gabian, Pablo Delgado, Enzo Lanzelotti, Fernando Berjano, Paola Pezoimburu, Federico Roasio,

Ezequiel Espósito, Claudio Pose, Andres Manikis y a todos aquellos que no

recuerde en este momento. También agradezco a aquellos que dejaron ser com-

vi

pañeros de la facultad, para pasar a ser amigos, Luciano César Natale, Germán

Acosta, Diego Vilaseca, Gustavo Dı́az, Matı́as Weber, Claudio Lupi, Manuel

Fernández, Lucas Sambuco,

Quiero agradecer a todas las personas importantes que pasaron por mi vida

durante este perı́odo, ya que no sólo estoy terminando mi carrera sino culminando una gran etapa en mi vida, y todos estas personas formaron parte de ella,

Lis Weiss, Jose Spillmann, Marcelo Razeto, Sandra Canepuccia, Santiago Razeto, Natalia y Carla Belén Rossi, Sebastián Salles, Alejandro sansalone, Glenda

Busch, Sarah Collins, Ana Belén Garcı́a, Barbara Beutel, Ignacio Unrrein, Lucas

Sakalis, Mauro Garcı́a Alena, Alejandro Mauch, Sebastián Deter, Gaston Santana, Pablo Falcioni, Martı́n Burgueño, Alejandro Sappracone, Hernán Goncalves.

Agradezco de también a mis más grandes amigos, a quienes siempre voy

a querer, quienes fueron compañeros en buenos y malos momentos, quienes

siempre estuvieron, con quienes compartir dı́as y noches de estudio, salidas e

infinidad de cosas y por eso son especiales para mi, Jesica Lazart, Mariana Ende,

Barbará y Daniela Spillmann Weiss, Agustina Cánepa, Franco Gallardi, Hernán

Pedros, Juan Sist, Patricio Helfrich, Leonardo Unger, Mauricio Koller, Fernando

Perez, Matias Schwabauer e Ignacio Razeto.

No puedo dejar de agradecer a la familia Hoffmann, a quienes personalmente

me gusta llamar ‘mi familia alemana’, a quienes quiero muchı́simo, ellos son

Michael, Martina, Ulrich y Bernhard.

Por último quiero agradecerles mucho mucho mucho a mi familia, quienes

me apoyaron durante toda mi vida e hicieron esto posible, a ellos los amo incondicionalmente y son Nélida Nazarre, Rodolfo Parrondo, Oscar Zacchigna, Ana

Marı́a D’Ambrosio, y Julia Zacchigna.

Índice general

1. Introducción

1.1. Ventajas de la paralelización . . . . . . . . . . .

1.2. Clasificación de los procesadores . . . . . . . .

1.3. Evolución de los procesadores . . . . . . . . . .

1.3.1. Inicio . . . . . . . . . . . . . . . . . . .

1.3.2. Paralelismo a nivel de instrucción . . . .

1.3.3. Limitaciones en el paralelismo a nivel de

1.3.4. Paralelismo a nivel de tarea . . . . . . .

1.4. Multi-Threading . . . . . . . . . . . . . . . . .

1.5. Multi-procesadores . . . . . . . . . . . . . . . .

1.6. Sistemas operativos y programación distribuida

1.6.1. Sistemas operativos . . . . . . . . . . .

1.6.2. Procesos e hilos . . . . . . . . . . . . . .

1.6.3. Planificación de hilos . . . . . . . . . . .

1.6.4. Programación distribuida . . . . . . . .

1.7. Consumo y frecuencia de trabajo . . . . . . . .

1.8. Conclusiones . . . . . . . . . . . . . . . . . . .

. . . . . . .

. . . . . . .

. . . . . . .

. . . . . . .

. . . . . . .

instrucción

. . . . . . .

. . . . . . .

. . . . . . .

. . . . . . .

. . . . . . .

. . . . . . .

. . . . . . .

. . . . . . .

. . . . . . .

. . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

1

1

2

3

3

3

9

9

10

12

13

13

14

14

15

16

16

2. Teorı́a y diseño

19

2.1. Procesador Plasma y arquitectura MIPS . . . . . . . . . . . . . . 19

2.2. Comunicación entre los procesadores . . . . . . . . . . . . . . . . 20

2.3. Bus de interconexión . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.4. Arquitectura de la memoria . . . . . . . . . . . . . . . . . . . . . 24

2.4.1. Principio de localidad . . . . . . . . . . . . . . . . . . . . 24

2.4.2. Jerarquı́a de la memoria . . . . . . . . . . . . . . . . . . . 24

2.4.3. Memoria Cache . . . . . . . . . . . . . . . . . . . . . . . . 25

2.4.4. Arquitectura de la memoria en procesadores multi-núcleo 30

2.4.5. Protocolos y algoritmos de coherencia de cache . . . . . . 32

2.5. Manejo de interrupciones . . . . . . . . . . . . . . . . . . . . . . 33

2.6. Operaciones atómicas . . . . . . . . . . . . . . . . . . . . . . . . 34

2.7. Caracterización a priori del procesador . . . . . . . . . . . . . . . 39

3. Implementación y resultados obtenidos

3.1. Herramientas utilizadas . . . . . . . . .

3.2. Estructura del procesador multi-núcleo .

3.3. Controlador de memoria . . . . . . . . .

3.3.1. Descripción . . . . . . . . . . . .

3.3.2. Puertos de la entidad . . . . . .

vii

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

41

41

42

42

42

43

ÍNDICE GENERAL

viii

3.4. Plasma multi-núcleo . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.1. Descripción . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.2. Puertos de la entidad . . . . . . . . . . . . . . . . . . . .

3.5. Árbitro del bus . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.1. Descripción . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.2. Puertos de la entidad . . . . . . . . . . . . . . . . . . . .

3.6. Manejador de interrupciones . . . . . . . . . . . . . . . . . . . . .

3.6.1. Descripción . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.2. Puertos de la entidad . . . . . . . . . . . . . . . . . . . .

3.7. Núcleo . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.1. Descripción . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.2. Puertos de la entidad . . . . . . . . . . . . . . . . . . . .

3.7.3. Descripción del algoritmo de coherencia de cache . . . . .

3.8. Unidad de control del núcleo . . . . . . . . . . . . . . . . . . . .

3.8.1. Descripción . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.2. Puertos de la entidad . . . . . . . . . . . . . . . . . . . .

3.9. CPU plasma . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.10. Caracterización del procesador . . . . . . . . . . . . . . . . . . .

3.10.1. Tamaño del procesador . . . . . . . . . . . . . . . . . . .

3.10.2. Desempeño en función del trabajo de las tareas . . . . . .

3.10.3. Desempeño en función de la utilización del bus . . . . . .

3.10.4. Tiempo de procesamiento en función del número de núcleos

3.10.5. Importancia de la memoria cache en procesadores multinúcleo . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

46

46

50

51

51

53

54

54

54

55

55

60

62

63

63

65

68

68

70

70

70

72

73

4. Conclusiones y trabajos futuros

75

4.1. Conclusiones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

4.2. Trabajos Futuros . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Bibliografı́a

77

A. Implementaciones de spinLocks

79

A.1. Con soporte de hardware . . . . . . . . . . . . . . . . . . . . . . . 79

A.2. Solución propuesta por Peterson . . . . . . . . . . . . . . . . . . 80

A.3. Solución propuesta por el creador del PlasmaOS . . . . . . . . . 80

Capı́tulo 1

Introducción

En este capı́tulo se hace una breve introducción a la paralelización en el

contexto de los procesadores, para luego poder clasificar a los procesadores según

este criterio. Luego se realiza descripción de la evolución de los procesadores a lo

largo de la historia. Se muestran también las limitaciones que fueron apareciendo

y los cambios en el enfoque de los diseños de los mismos.

1.1.

Ventajas de la paralelización

El concepto de paralelismo es de gran importancia para este trabajo y lo

definiremos en nuestro caso como la forma de realizar dos acciones simultáneamente. Aprovechar el paralelismo es uno de los métodos más importantes para

mejorar el rendimiento en la ejecución de cualquier tarea, en particular en procesadores. Por ejemplo, al transferir información de un disco rı́gido, la velocidad

de transferencia está dada por el ancho de banda del disco, pero si se se colocan

dos discos y los cuales se acceden simultáneamente, se logra duplicar el ancho

de banda, y ası́ mejorar el rendimiento.

A nivel de ejecución de código hay distintos tipos de paralelismos y distintas

formas de explotarlo. Un primer ejemplo del uso del paralelismo es a nivel de

sistema, para lo que se pueden utilizar múltiples discos y/o múltiples procesadores. La carga de trabajo para atender las solicitudes de los clientes puede

ser repartida entre los procesadores y discos, y como consecuencia se obtiene

un mejor rendimiento. Cuando en un sistema es posible expandir la memoria

y el número de procesadores y discos se lo llama sistema escalable, y es una

propiedad muy valorada en los servidores.

Por otro lado a nivel de procesadores individuales, sacar provecho del paralelismo a nivel de instrucción es crı́tico para mejorar la capacidad de procesamiento, se explica con profundidad en la sección 1.3.2. Una de las formas

más simples de lograr esto es a través del uso de pipelining, que fue la técnica

utilizada en los primero micros para explotar el paralelismo. La idea básica del

pipeline, que se explica con mayor detalle en la sección 1.3.2, es solapar la ejecución de las instrucciones y ası́ reducir el tiempo total de ejecución para una

1

CAPÍTULO 1. INTRODUCCIÓN

2

secuencia de instrucciones. Un factor clave que da lugar al pipelining es que no

todas las instrucciones dependen de la anterior inmediata y por ello ejecutar la

instrucción parcialmente o completamente en paralelo es posible.

1.2.

Clasificación de los procesadores

A lo largo de la historia han surgido varias clasificaciones para los sistemas

computacionales. Muchas de ellas quedaron rápidamente obsoletas con el paso

del tiempo. Sin embargo, la clasificación propuesta por Flynn en el año 1966

[1] sigue siendo válida. La misma se basa en un modelo de dos dimensiones:

Stream de datos y Stream de instrucciones. Cada una de estas dimensiones

tiene dos posibles valores: Simple o Múltiple (en paralelo). Se obtienen ası́ cuatro

combinaciones posibles:

SISD: En inglés Single Instruction Single Data. Es el caso de un procesador

simple como el plasma.

SIMD: En inglés Single Instruction Multiple Data. Es el caso de las llamadas computadoras vectoriales o aquellas llamadas VLIW o EPIC.

MISD: En inglés Multiple Instruction Single Data. Son de uso poco frecuentes, algunos computadoras que entran en esta categorı́a son aquellas

que deben ser tolerantes a fallas, en las cuales existen múltiples procesadores trabajando sobre el mismo stream de datos, y que a la vez deben de

coincidir en el resultado.

MIMD: En inglés Multiple Instruction Multiple Data. Es el caso de los

multiprocesadores que se tratan en este trabajo.

Los SIMD y MISD son sistemas diseñados para usos especı́ficos, y no serán

tratados con mucha profundidad en este trabajo. Los SISD son los más simples

de los procesadores, y no sacan provecho ni de la paralelización de los datos

ni de las instrucciones, aunque si hacen uso de técnicas como pipelininig. Las

computadoras MIMD son las más flexibles dentro de esta clasificación, es posible

ejecutar dos streams de datos e instrucciones diferentes en simultáneo, sean

o no independientes entre sı́. Es claro también que deben existir al menos la

misma cantidad de tareas (o streams de instrucciones y datos) que de núcleos de

procesamiento para poder aprovechar las ventajas de una computadora MIMD.

Esto se explica en las siguientes secciones y de allı́ se concluye que el surgimiento

de procesadores MIMD es consecuencia del:

La necesidad de aumentar el rendimiento en la ejecución de tareas.

La limitación de los procesadores SISD, y de la paralelización posible en

las instrucciones.

La posibilidad de dividir las tareas en diferentes procesos independientes,

o poco correlacionados, lo que se llama paralelización a nivel de tareas.

A lo largo de este trabajo se tratan consecuencias y problemáticas de esta

paralelización.

CAPÍTULO 1. INTRODUCCIÓN

1.3.

1.3.1.

3

Evolución de los procesadores

Inicio

Los primeros procesadores, surgidos en la decada del 60, ejecutaban secuencialmente cada una de las instrucciones del código. La ejecución de cada instrucción esperaba la finalización de la instrucción predecesora antes de comenzar. No

hacı́an uso de ningún tipo de paralelización. El método utilizado para aumentar

su rendimiento consistı́a en aumentar la frecuencia del reloj, y los diseños de

las arquitecturas se apuntaban a reducir tiempo de propagación de las señales

en el procesador (es decir, cantidad de compuertas conectadas en cascada), y

de esa manera poder aumentar la frecuencia de trabajo. Otro método que se

utilizaba para llegar a ese mismo objetivo era mejorar la tecnologı́a del proceso

de fabricación de los circuitos integrados, reduciendo cada vez más el tamaño

de los transistores y ası́ poder aumentar su velocidad de trabajo [2]. Rápidamente se alcanzaron los lı́mites máximos para las tecnologı́as de la época, y se

comenzaron a estudiar otro tipo de maneras de seguir mejorando el rendimiento, basadas en la arquitectura del procesador en vez del proceso de fabricación.

La evolución en las arquitecturas se apuntaba a mejorar los rendimientos pero

siempre teniendo en cuenta los tipos de programas que se pretendı́a correr en

los procesadores.

Para medir el rendimiento de un procesador se utilizan programas llamados benchmark. Existen distintos benchmarks para evaluar distintos aspectos de

procesador. Por ejemplo, algunos evalúan operaciones en punto fijo, otras en

punto flotante, ancho de banda de la memoria, etc. Además existen distintos

benchmarks según el contexto para el que fueron diseñados, como pueden ser

computadoras de escritorio, servidores, sistemas embebidos, etc. Tras la ejecución de un benchmark, un cierto número de instrucciones han sido procesadas, y

una cierta cantidad de ciclos de reloj y un perı́odo de tiempo determinado han

transcurrido. A partir de estos tres valores surgen dos parámetros muy utilizados para evaluar a los procesadores, el CPI (en inglés Cicles Per Instruction)

que no tiene en cuenta el tiempo de ejecución y a la vez es independiente de la

frecuencia de reloj y el IPS (en inglés Instructions Per Second ) que no tiene en

cuenta la cantidad de ciclos que le lleva finalizar la ejecución de una instrucción.

La frecuencia de trabajo del procesador es a la vez el factor que vincula estos

dos valores.

En las siguiente secciones de este capı́tulo se muestra la evolución de las arquitecturas, junto con las mejoras y las problemáticas que implican. Finalmente

se muestran las nuevas tendencias en los procesadores, donde en algunos casos

especiales dejan de ser importantes los rendimientos individualmente y pasa a

ser fundamental la relación rendimiento/consumo.

1.3.2.

Paralelismo a nivel de instrucción

El paralelismo a nivel de instrucción o ILP (en inglés Instruction Level Paralelism) se refiere a la posibilidad de superponer la ejecución de más de una

instrucción en un programa. Estas instrucciones pueden ser consecutivas o no.

Un ejemplo de dos instrucciones que pueden ejecutarse en paralelo es:

1

2

add $ 1 , $ 2 , $3

sub $ 4 , $ 2 , $3

CAPÍTULO 1. INTRODUCCIÓN

4

Donde el resultado de sumar los regitros $2 y $3, se guarda en $1 y por otro

lado la resta de esos dos mismos registros se guarda en el registro $4. Las dos

operaciones pueden ejecutarse al mismo tiempo, sin ningún problema. Distinto

es en el siguiente ejemplo:

1

2

add $ 1 , $ 2 , $3

sub $ 4 , $ 1 , $5

Donde se ve que la segunda operación no puede ser ejecutada hasta que el resultado de primer instrucción no esté disponible. A estas instrucciones se las

llama dependientes, o también se dice que existe una dependencia entre las instrucciones. Existen varios tipos de dependencias entre instrucciones, pueden ser

de datos, de control o de hardware Estas dependencias se detallan en profundidad en este trabajo. Para programas tı́picos en assembler MIPS, en bloques

de programa donde no hay saltos ni bucles(salvo por el salto para llegar a ese

bloque y el salto para volver) el porcentaje tı́pico de instrucciones paralelizables

se encuentra entre un 15 % y un 20 % [2]. Al ejecutar este tipo de bloques en

un procesador con capacidad de paralelismo no brinda una mejora significativa.

Para bloques de programa donde existen ramificaciones y bucles, este porcentaje

de instrucciones paralelizables es mucho mayor y hacer provecho de la paralelización a nivel de instrucción se vuelve una de las maneras más eficientes para

mejorar el rendimiento.

La ejecución de instrucciones en forma superpuesta implica modificaciones

en la arquitectura del procesador:

Pipelining: Cuando la lógica utilizada para la ejecución de una instrucción

no puede seguir siendo reducida, el pipelining es una técnica que surge naturalmente. Se basa en dividir la ejecución de la instrucción en etapas,

donde cada una de estas etapas tiene una cantidad mucho menor de compuertas conectadas en cadena. De este modo se logra bajar el tiempo de

propagación en cada etapa, lo cual hace posible el aumento de la frecuencia

del reloj. Estas etapas son interconectadas por registros (flip-flops), que

tienen la función de guardar los resultados de cada etapa y transferirlo a la

siguiente en cada ciclo de reloj [3]. Las cinco etapas tı́picas y los registros

utilizados para interconectarlas se muestran en la figura 1.1. Las etapas

pueden superponerse. En la figura 1.2(a) se ve un ejemplo de un pipeline

de una arquitectura RISC, donde la ejecución de la instrucción se divide

clásicamente en cinco etapas:

• IF Instruction Fetch

• ID Instruction Decode

• EX Execution

• MEM Memory Access

• WB Write Back

En este tipo de arquitecturas existe lo que se llaman stalls: son momentos donde alguna etapa del pipeline debe ser pausada por existir alguna

dependencia entre dos instrucciones consecutivas. Este tipo de arquitecturas no muestra mejoras en el CPI, de hecho en general lo empeoran,

pero al lograr un aumento en la frecuencia de reloj, se puede mejorar el

IPS. El CPI empeora debido a los Stalls que se generan en el procesador.

EX

MEM

REGISTROS

5

REGISTROS

ID

REGISTROS

IF

REGISTROS

IF

CAPÍTULO 1. INTRODUCCIÓN

WB

CLK

Figura 1.1: Pipeline de cinco etapas interconectadas con registros. En

esta figura se muestran las cinco etapas en las que se divide clásicamente una

instrucción de una arquitectura RISC, y como se interconectan mediante registros para poder reducir los tiempo de propagación en las etapas individualmente

y ası́ poder aumentar la frecuencia de trabajo.

En arquitecturas más evolucionada se utilizan técnicas como forwarding

y bypassing, que permiten evitar algunos de los stall. Cómo se producen

los stalls y las maneras que existe de evitarlos son temas ampliamente

explicados en [3]

Multiple Instruction Issue: El procesador ejecuta realmente varias instrucciones simultáneamente. Para ellos algunas partes del Hardware deben ser

multiplicada, como por ejemplo las ALU. En la figura 1.2(b), se ve como

se realiza la ejecución de las instrucciones. Se muestra la diferencia con el

ejemplo de la figura 1.2(a), donde en cada ciclo de reloj se ejecutan dos

veces cada una de las etapas del pipeline. El uso de este recurso mejora el

CPI. En el ejemplo de la figura 1.2(b) el CPI puede llegar a ser reducido

a la mitad, al ser posible completar hasta dos instrucciones por ciclo. De

esta manera se vuelve posible también alcanzar valores de CPI menores

a la unidad. En los pipelines más mas evolucionados los stalls debidos

a dependencias entre instrucciones son prácticamente eliminados, lo que

mejora notablemente el ILP.

Como se dijo este tipo de soluciones permiten la ejecución superpuesta de

instrucciones, pero a veces la superposición no es posible debido a las dependencias existentes entre las instrucciones. A veces estas dependencias dependen

sólo del orden de las instrucciones, por ejemplo en el siguiente código:

1

2

3

add $ 1 , $ 2 , $3

sub $ 4 , $ 1 , $5

sub $ 6 , $ 2 , $3

las instrucciones 1 y 2 son dependientes. Un procesador con dos issue slots 1

tiene dos ramas de ejecución de instrucciones. La rama que ejecute la segunda

instrucción, deberá ser pausada en algún momento debido a la dependencia

existente. Para evitar la pausa que se produce en la ejecución se puede modificar

el orden de las instrucciones por el siguiente:

1

2

add $ 1 , $ 2 , $3

sub $ 6 , $ 2 , $3

1 No tomamos como ejemplo un procesador que sólo posee un pipeline, porque como se dijo

antes las dependencias entre instrucciones pueden ser evitadas en esas arquitecturas.

CAPÍTULO 1. INTRODUCCIÓN

6

INSTRUCCIONES

Ciclo Ciclo Ciclo Ciclo Ciclo Ciclo Ciclo Ciclo Ciclo

1

3

4

5

6

7

8

9

2

INSTRUCCIÓN 1

INSTRUCCIÓN 2

INSTRUCCIÓN 3

INSTRUCCIÓN 4

INSTRUCCIÓN 5

IF

ID

IF

EX MEM WB

ID

EX MEM WB

IF

ID

EX MEM WB

IF

ID

EX MEM WB

IF

ID

EX MEM WB

TIEMPO

(a) Arquitectura con pipeline de cinco etapas.

INSTRUCCIONES

Ciclo Ciclo Ciclo Ciclo Ciclo Ciclo Ciclo Ciclo Ciclo

1

2

3

4

5

6

7

8

9

INSTRUCCIÓN 1

INSTRUCCIÓN 2

INSTRUCCIÓN 3

INSTRUCCIÓN 4

INSTRUCCIÓN 5

INSTRUCCIÓN 6

INSTRUCCIÓN 7

INSTRUCCIÓN 8

INSTRUCCIÓN 9

INSTRUCCIÓN 10

IF

IF

ID

ID

IF

IF

EX MEM WB

EX MEM WB

ID

EX MEM WB

ID

EX MEM WB

IF

ID

EX MEM WB

IF

ID

EX MEM WB

IF

ID

EX MEM

IF

ID

EX MEM

IF

ID

EX

IF

ID

EX

WB

WB

MEM WB

MEM WB

TIEMPO

(b) Arquitectura con pipeline de cinco etapas y dos issue.

Figura 1.2: En la figura 1.2(a) se puede apreciar como las etapas de las diferentes

instrucciones se suporponen. En la figura 1.2(b) se muestran como se superponen

las etapas e instrucciones de un procesador con el mismo pipeline de cinco etapas

y dos issue slots.

3

sub $ 4 , $ 1 , $5

esta porción de código tiene mayor ILP que la anterior.

Para aumentar el ILP de un programa se puede entonces reordenar las instrucciones. Para poder hacer un reordenamiento y ası́ hacer uso eficiente del

ILP, existen dos enfoques claramente diferenciables:

Basado en Software: Este enfoque encuentra posibles instrucciones paralelizables en forma estática, en tiempo de compilación de un programa. Es

la forma más básica de hacerlo. Esto depende del compilador, que básicamente reacomoda instrucciones de forma tal de bajar el porcentaje de

instrucciones con dependencias. Como se dijo antes en la ISA de MIPS no

se especifica la implementación, por lo que el compilador no tiene porque

saber la arquitectura del mismo, pero si puede explicitarse, de manera

que tenga en cuenta la arquitectura del microprocesador, como puede ser

si cuenta o no con unidades de multiplicación de punto fijo, unidades de

multiplicación de punto flotante, etc.

Basado en Hardware: Este enfoque encuentra posibles instrucciones paralelizables en forma dinámica, en tiempo de ejecución de un programa.

Es decir, las instrucciones no necesariamente ingresan en el orden en el

CAPÍTULO 1. INTRODUCCIÓN

7

que se encuentran en el código, sino que el procesador puede ‘ver’, la instrucción a la que apunta el contador de programa y un número dado de

instrucciones posteriores a esa. A estas instrucciones se las llama ventana de programa. De entre todas las instrucciones que se encuentran en

esa ventana del programa, el procesador elige las que son mejores para su

ejecución en paralelo.

En un caso general estos dos enfoques pueden ser explotados en forma simultánea, logrando ası́ mejores resultados en los valores de CPI e IPS.

A modo de ejemplo se presentan brevemente dos técnicas simples utilizadas

para la planificación estática:

Loop unrolling: Incrementa el número de operaciones que se ejecutan dentro de un bucle y a la vez reduce el número de iteraciones. En los bucles

es donde en general se encuentra un mayor número de instrucciones independientes. El ejemplo clásico es el de la suma de dos vectores, donde

en vez de sumar una componente, se suman dos o más de las componentes por iteración y ası́ se reduce la cantidad de veces que se ejecutan las

instrucciones del bucle. Una consecuencia de realizar esto es que el código

aumenta su tamaño ocupando mayor espacio en la memoria.

Pipeline Scheduling: Dado que hay distintos tipos de dependencias, existen

pares de instrucciones que tienen dependencias reales y otros que pueden

ser evitados. Las instrucciones pueden ser planificadas teniendo en cuenta

este factor y de esa manera evitar pausas en la ejecución. Esta técnica

depende de la arquitectura.

Existen otras técnicas de hardware que se utilizan para mejorar el rendimiento, reduciendo los stalls, mejorando la planificación dinámica, aumentando

el número de instrucciones paralelizables, prediciendo posibles saltos y especulando que instrucciones se ejecutarán. Se explican a continuación algunas

brevemente:

A continuación describimos brevemente algunas de las técnicas más conocidas para mejorar el rendimiento. Los objetivos son evitar stalls y pausas en

en los procesadores, mejorar la planificación dinámica, aumentar el número de

instrucciones paralelizables, y predecir el flujo del programa correctamente:

Forwarding and bypassing: Se utiliza en los pipelines para evitar stalls al

ejecutar instrucciones que poseen dependencias de datos. Se basa en extraer los datos antes de que terminen de atravesar el pipeline. Por ejemplo,

se extrae el resultado de una operación aritmética apenas termina la etapa

de ejecución en vez de esperar a que se escriba en un registro.

Branch prediction (local and global): Cuando en un programa hay un salto condicional (o bifurcación) las instrucciones que se deben de ejecutar

cambian según se cumpla o no la condición de salto. Esta técnica se basa

en ir cargando en el procesador las instrucciones más probables y ellas

dependen de la probabilidad de saltar o no. En un bucle lo más usual es

que al llegar al final se salta de nuevo al principio. Este salto se realiza

N veces, de las cuales N − 1 veces se salta y sólo una vez se sigue de

largo. Para todo bucle con N mayor a uno las probabilidades de salto son

mayores a las de no saltar.

CAPÍTULO 1. INTRODUCCIÓN

8

Register renaming: Se generan registros extra aparte de los definidos en

la ISA MIPS, estos registros no pueden ser accedidos por los usuarios,

en cambio sı́ internamente por el procesador y en algunos casos se logra

mejorar el rendimiento. Un ejemplo simple serı́a el siguiente:

1

2

3

add $ 1 , $ 2 , $3

sw $ 1 , 0 x10 ( $ sp )

li

$ 1 , 0 x1

Las instrucciones dos y tres tienen una dependencia, de modo que la instrucción tres no puede ser ejecutada antes que la dos, ya que se estarı́a

guardando un valor erróneo, pero el registro $1 es cargado con un valor

distinto en la tercer instrucción. Si fuese posible cambiar $1 por $4 en las

dos primeras instrucciones, entonces sı́ serı́a posible ejecutar las instrucciones dos y tres en paralelo. Esto ocurre a veces por falta de registros

en la arquitectura, que es una de las condiciones del procesador perfecto:

infinito número de registros en el procesador. A veces no se puede simplemente diseñar un procesador con mayor número de registros, ya que esta

caracterı́stica puede estar definida en la arquitectura de instrucciones (como es el caso de MIPS), pero los procesadores sı́ pueden tener un número

mayor de registros en su arquitectura e internamente utilizarlos como se

explico antes, renombrándolos para lograr mayor ILP.

Teniendo en cuenta lo dicho anteriormente se puede hacer una clasificación

de los núcleos de procesamiento a partir de la arquitectura del procesador, sin

especificar si posee un núcleo o varios de ellos. En ésta clasificación también se

identifica a categorı́a pertenece de la clasificación mostrada anteriormente en la

sección 1.2:

Procesador escalar: Los procesadores más simples, pueden estar implementados con un pipeline o no. Clasificado como SISD.

Procesador super-escalar con planificación estática: Procesadores que utilizan Multiple Instruction Issue, en general utilizan una arquitectura con

pipeline. La planificación de las instrucciones es estática, o sea que solo se

realiza a nivel de compilación. Clasificado como MIMD.

Procesadores vectoriales que son clasificados como SIMD, utilizados principalmente en aplicaciones cientı́ficas, que generalmente realizan muchas

veces la misma operación entre distintos datos, por ejemplo al hacer operaciones entre vectores de gran tamaño.

Procesador de arquitectura VLIW (en inglés Very Long Instruction Word )

o EPIC (en inglés Explicit-Parallel Instruction Computer ): Este tipo de

procesadores son diferentes a los que se han presentado en este trabajo. Las

instrucciones que ejecutan los mismos indican en forma explı́cita la operación que debe realizar cada una de las unidades funcionales del procesador.

Tienen dos ventajas frente a los procesadores de planificación dinámica:

Una alta reducción en el hardware necesario para su implementación y

que los compiladores pueden generar código de manera que se aproveche

al máximo las ventajas del paralelismo. Este tipo de procesadores son del

tipo de MIMD.

CAPÍTULO 1. INTRODUCCIÓN

9

Procesador super-escalar con planificación dinámica: Procesadores que utilizan Multiple Instruction Issue, en general utilizan una arquitectura con

pipeline. Aprovecha tanto las planificación estática lograda a nivel compilación y la planificación dinámica realizada a nivel de ejecución. La operación

que ejecuta cada unidad funcional del procesador se define luego de decidir

que instrucciones se ejecutan. Este tipo de procesadores se clasifican como

MIMD.

La mayorı́a de los núcleos de los procesadores que se utilizan hoy en dı́a son

superescalares aunque no todos tienen planificación dinámica de instrucciones,

debido a la gran complejidad que esto presenta.

1.3.3.

Limitaciones en el paralelismo a nivel de instrucción

En un procesador ideal que aprovecha completamente el ILP presente en un

programa, los lı́mites en el rendimiento son impuestos por los flujos de datos a

través de los registros o memoria.

Un procesador ideal contarı́a con infinitos registros, una ventana de programa

infinita, perfectas predicciones en el flujo de ejecución del programa, un perfecto

análisis de aliasing de memoria2 y accesos a memoria que solo necesiten un ciclo

de reloj. En un procesador real estas condiciones no se cumplen, y por eso se

alcanza el lı́mite en el rendimiento de un mono-procesador, cuando el costo de

hardware es demasiado, y la mejora que su complejización proporciona no es

significativa.

1.3.4.

Paralelismo a nivel de tarea

En ocasiones se habla de paralelismo a nivel de tarea o hilo (TLP, en inglés

Thread Level Paralelism). La definición precisa de hilos, y la de procesos también, se puede encontrar en [10]. Para explicar TLP basta con tener una pequeña

noción de lo que es un hilo o un proceso, para este caso utilizaremos el nombre

tarea independientemente de que sea un hilo o un proceso. Una tarea es una

porción de programa que cumple con un objetivo especı́fico. Hay tareas que son

independientes entre sı́ y tareas que poseen dependencias con otras. El ejemplo

clásico para dos tareas pseudo-independientes lo encontramos en un servidor al

cual acceden N usuarios y hacen N pedidos distintos. En general estas tareas

pueden ser ejecutadas todas por separado y en cualquier orden. Un corolario

de poder ejecutar las tareas por separado y en cualquier orden es que también

pueden ser ejecutadas en paralelo.

Los procesadores MIMD pueden explotar las ventajas del TLP y hay dos

enfoques para explotarla:

Los multi-procesadores: El enfoque se basa en multiplicar el número de

núcleos e interconectarlos de manera eficiente, sin que importe la arquitectura del núcleo en sı́ (ver sección 1.5). Pueden clasificarse en dos grandes

2 Es una técnica para reducir accesos a memoria durante el proceso de optimización en

tiempo de compilación. Detecta uno de los dos casos posibles, si existe o no aliasing entre

punteros, es decir punteros que apuntan a una misma posición de memoria. Una vez detectado

es posible realizar las optimizaciones necesarias, si no se puede asegurar ninguno de los dos

casos, las optimizaciones no pueden ser realizadas.

CAPÍTULO 1. INTRODUCCIÓN

10

grupos, los procesadores simétricos y los asimétricos. La principal diferencia entre los dos grupos es la forma en la que se interconectan los distintos

procesadores, como se comunican y como se distribuye la memoria, como

se ve en la sección 2.2.

Los procesadores que soportan multi-threading(MT) y simultaneous-multithreading(SMT): Es un enfoque en el que un único núcleo soporta la ejecución de más de una tarea en simultáneo, o que tiene la capacidad de

intercambiar tareas de forma muy rápida, ya que almacena contextos de

más de una tarea [2]. En la sección 1.4 se profundiza el tema.

1.4.

Multi-Threading

El concepto de MT o Multi-Threading y SMT del inglés Simultaneous MultiThreading tiene lugar sólo si existen varias tareas en ejecución, que poseen poca

dependencia entre sı́. Durante la ejecución de una tarea se puede llegar a tener

un stall que dure una cantidad significativa de ciclos de reloj, pero no tan

grande como para que convenga realizar un cambio de contexto3 . Es el caso de

una instrucción de multiplicación/división entera, o en punto flotante, que suele

tomar varios ciclos de reloj antes de entregar el resultado. La situación anterior

da lugar a lo que se llama multi-threading, lo que implica almacenar el contexto

de múltiples tareas en el núcleo, duplicando hardware necesario, tal como los

registros y el contador de programa. De esta manera un cambio de contexto

entre estas dos tareas tiene costo nulo y se vuelve provechoso cambiar de tarea

cuando existen estos stalls de corto tiempo.

Visto de otra manera, lo que se tiene son varias ventanas de programas en

tareas distintas y se toman instrucciones o bien de una o de la otra. Hay dos

tipos de multi-threading, el grueso y el fino. En el grueso, se realiza un cambio

de contexto cada vez que hay un stall que lo amerite. En el fino, se cambia de

tarea en cada ciclo.

La desventaja del grueso, es que espera a que exista un stall antes de cambiar

de tarea, con lo que se pierde un ciclo. Durante este ciclo de reloj se identifica

el stall y un ciclo posterior se procede al cambio de contexto. En el fino se

cambia de tarea en cada ciclo, lo cual no impide que puedan ocurrir stalls, pero

sı́ ocurren con menor frecuencia. Una desventaja del fino es que la latencia de

ejecución de una instrucción en una tarea aumenta: En el ejemplo de la figura

1.3, al ejecutar las tareas A y B en un MT grueso, las seis primeras instrucciones

comienzan su ejecución entre los ciclos uno y tres, mientras que si se utiliza un

MT fino, las seis primeras instrucciones recién comienzan a ejecutarse entre el

primero y el noveno ciclo.

En multi-threading se pueden tomar instrucciones únicamente de una sola

ventana de programa (o sea de una sola tarea) en cada ciclo de reloj. En cambio

en Simultaneous multi-threading, en cada ciclo de reloj pueden ser tomadas instrucciones de distintas ventanas, esto se muestra en la figura 1.3 en comparación

con el MT fino y grueso. En general existe una dependencia notablemente menor entre instrucciones de distintas tareas, de esta manera se puede sacar mayor

3 Un cambio de contexto es el proceso que realiza el sistema operativo al cambiar de una

tarea a otra, para ello debe guardar el estado de la tarea en ejecución y cargar el estado de la

tarea que será ejecutada. Se explica con mayor detalle en la sección 1.6.1.

CAPÍTULO 1. INTRODUCCIÓN

11

TAREA B

TAREA C

TAREA D

ISSUE

SLOTS

ISSUE

SLOTS

ISSUE

SLOTS

ISSUE

SLOTS

TIEMPO

TAREA A

(a) Threads.

MT FINO

SMT

ISSUE

SLOTS

ISSUE

SLOTS

ISSUE

SLOTS

TIEMPO

MT GRUESO

(b) Multi-Threading.

Figura 1.3: Como cuatro tareas usan los issue slots de un procesador superescalar en diferentes enfoques. La figura 1.3(a) muestra como cada tarea utiliza

los issue slots en un procesador superescalara estándar sin soporte para MT.

Los ejemplos de la figura 1.3(b) muestran tres opciones de MT. Se observa que

las tareas se ejecutan en conjunto. El eje horizontal representa los issue slots

disponibles en cada ciclo de reloj, en este caso cuatro. El vertical el tiempo en

ciclos de reloj. Coarse-MT cambia la tarea en ejecución al producirse un stall

(pierde un ciclo en cada cambio). Fine-MT cambia la tarea en ejecución en cada

ciclo (aumenta la latencia de ejecución entre dos instrucciones de una misma

tarea). SMT utiliza instrucciones de las cuatro tareas en cada ciclo de reloj,

haciendo mejor uso del núcleo (aumenta la latencia como en fine-MT pero en

menor meida).

CAPÍTULO 1. INTRODUCCIÓN

12

provecho de la habilidad del procesador de ejecutar instrucciones en paralelo.

La dependencia entre las instrucciones es el factor que limita la paralelización

de instrucciones y con esta técnica se logran grandes mejoras. Entonces se puede decir que el multi-threading es una técnica que aprovecha ILP y TLP en

conjunto.

Teniendo en cuenta este técnica a los procesadores super-escalares se los

puede subclasificar en:

Superscalar con multithreading grueso.

Superscalar con multithreading fino.

Superscalar con multithreading simultáneo.

Este último tipo de procesadores son usualmente los más poderosos y más

grandes en tamaño. No se utilizarán para el análisis de multi-procesadores en

este trabajo por una limitación en la capacidad de las FPGAs.

1.5.

Multi-procesadores

Sin importar si el núcleo saca provecho de ILP, TLP, MT fino o grueso o

SMT, los procesadores múlti-nucleo tienen la ventaja de aprovechar el paralelismo a nivel de tarea que se encuentra en las aplicaciones. Es decir que se

aprovecha la TLP independientemente de la arquitectura del núcleo de procesamiento, ya que se tiene más de un núcleo de procesamiento, cada uno con sus

registros, contador de programa y corriendo una tarea especı́fica, cada uno con

un contexto distinto.

Los distintos núcleos, o mejor dicho las tareas que corren en ellos, deben

comunicarse entre sı́ y además compartir otros recursos de hardware. Existen

distintas arquitecturas para lograr esto, que se tratan en el desarrollo de este

trabajo. En la figura 1.4 se contrasta un procesador mono-núcleo con uno de

múltiples núcleos, que son conectados a través de un bus simple.

El hecho de compartir la memoria trae varias complicaciones. Por ejemplo,

resulta necesario una entidad que la administre de forma correcta. Cada núcleo

se comunicará con esta entidad antes de poder realizar accesos a memoria.

En casos donde haya más de un procesador queriendo hacer uso de los recursos uno de ellos deberá ser pausado hasta que alguno de ellos finalice y la

entidad que los administra brinde acceso al siguiente núcleo. Este problema se

intensifica a medida que se aumenta el número de núcleos y que los programas

tienen mayor cantidad de instrucciones que solicitan acceso a los recursos de

hardware.

Dado que uno de los recursos más solicitado es el acceso a memoria, la implementación de una memoria cache brinda una técnica para disminuir el tráfico

que se genera. El uso de memorias cache trae otros beneficios y complicaciones

que se detallaran más adelante en la sección 2.4.3.

Por último, se deberá diseñar un controlador de interrupciones distinto al

utilizado en procesadores con un único núcleo, porque los procesadores pueden en principio ser interrumpidos por separado. La tarea de este controlador

será identificar a que procesador corresponde enviar cada solicitud de interrupción y esto se presentará en la sección 2.5.

CAPÍTULO 1. INTRODUCCIÓN

13

Figura 1.4: Procesadores de con un solo núcleo vs procesadores con varios

núcleos

1.6.

1.6.1.

Sistemas operativos y programación distribuida

Sistemas operativos

Un sistema informático consiste en uno o mas procesadores, una memoria

principal, y dispositivos de entrada/salida. Todos estos dispositivos forman un

sistema complejo. Escribir un programa que realice un buen seguimiento de

todos estos componentes, y que a su vez los utilice en forma correcta y de

una manera eficiente, es un trabajo de extrema dificultad. Por estas razones la

tendencia actual es equipar a estos sistemas con una capa de software llamada

sistema operativo, cuyo trabajo es administrar todos los dispositivos y brindar a

los programas escritos por los usuarios una interfaz simplificada con el hardware.

Los sistemas operativos se diseñan prestando especial atención al sistema

en el que van a correr, servidores, computadoras de escritorio, sistemas embebidos, etc. Se tienen en cuenta muchos factores para su diseño: flujo de datos

de entrada/salida, carga de procesamiento, simetrı́a o asimetrı́a de los distintos

núcleos de procesamiento, etc. Un factor que interesa nombrar para este trabajo

es que existen sistemas operativos de tiempo real o RTOS(en inglés Real-Time

Operating Sistems). Entre ellos se pueden diferenciar dos tipos: Hard RTOS, en

los cuales las respuestas deben ocurrir en un momento exacto y los Soft RTOS,

donde es aceptable no cumplimiento ocasional de algún plazo. Un ejemplo de los

Soft RTOS son los sistemas operativos multimedia, que reproducen audio y/o

video, mientras que uno para los hard RTOS es un sistema operativo que corre

en un sistema computacional que controla una lı́nea de producción, en donde se

interactúa con espacios fı́sicos y los movimientos deben de estar perfectamente

coordinados.

CAPÍTULO 1. INTRODUCCIÓN

1.6.2.

14

Procesos e hilos

Se llama proceso a una tarea que debe ejecutar el sistema operativo. Es una

porción de código con un fin en particular. Puede funcionar en conjunto con

otros procesos o no.

Un proceso puede ser dividido a su vez en hilos, que siguen siendo una porción

de código con un fin en particular, pero este conjunto de hilos que forman el

proceso tiene la particularidad de compartir el mismo espacio de memoria, a

veces llamado también contexto. Estos hilos trabajan entonces en un mismo

rango de memoria de programa y de datos.

Al intercambiar un proceso que se ejecuta en un núcleo, el contexto también debe cambiar, mientras que al intercambiar entre hilos, no. Un cambio de

contexto de memoria suele tener un gran costo computacional, y esta es la principal diferencia entre los hilos y procesos. Un cambio en el hilo que se ejecuta

tiene un costo computacional mucho menor al cambio de proceso. Un ejemplo

del costo de un cambio de contexto está relacionada con las memorias cache

(ver sección 2.4). Como dos procesos suelen trabajar en espacios de memoria

distintos, los datos e instrucciones deben ser cacheados nuevamente, generando

muchos misses los cuales suelen tener un costo grande de tiempo. El contexto

incluye también a los registros del procesador, ellos sı́ deben de ser almacenados

antes de cambiar de hilo o proceso.

1.6.3.

Planificación de hilos

Una de las capacidades de los OS es poder planificar las tareas en ejecución.

Hay dos protocolos populares:

Planificación Round-Robin: Reparte el tiempo de ejecución equitativamente entre todas las tareas. Primero se corre la primer tarea un perı́odo de

tiempo preestablecido, luego la segunda tarea la misma cantidad de tiempo, ası́ hasta llegar a la última y se vuelve a empezar con la primera.

Planificación preventiva: A cada tarea se le asigna una prioridad y cada

una de ellas tiene un estado: ‘lista’, ‘bloqueada’ o ‘en ejecución’. En la

figura 1.5, se ven los estados y transiciones posibles de las tareas. Cuando

se decide cambiar la tarea en ejecución se selecciona a la tarea en estado

‘lista’ que tenga mayor prioridad, esta será la tarea que pasará a estar

Figura 1.5: Estados y transiciones posibles para los hilos de un sistema operativo.

CAPÍTULO 1. INTRODUCCIÓN

15

en el estado de ejecución4 . Para sacar una tarea en ejecución existen dos

motivos: que el OS decida que ya estuvo suficiente tiempo en ejecución o

que la tarea se bloquee. Una tarea sólo puede pase al estado ‘bloqueada’

si está en estado ‘en ejecución’. Las razones para bloquear una tarea son:

• La tarea se bloquea por ‘voluntad’ propia, cuando decide que ya

realizó suficiente procesamiento libera el CPU para que otra tarea

pueda ejecutarse.

• La tarea se bloquea al querer utilizar un recurso de hardware ocupado.

El OS es entonces una pieza fundamental en todo sistema computacional

que trabaje con múltiples tareas ya que es quien planifica las distintas tareas

según prioridad y en función de los recursos disponibles, de esta manera el

usuario/programador ocuparse solamente de programar las tareas en sı́ y no en

como se debe alternar su ejecución.

1.6.4.

Programación distribuida

La programación distribuida se basa en dividir las tareas que se deben ejecutar en la mayor cantidad de subtareas independientes. Este paradigma/enfoque

de programación es impulsado por la aparición de los multi-procesadores, que

como vimos tiene la capacidad de correr tareas en paralelo y cuanto mayor sea la

independencia entre tareas mayor será el aumento en el rendimiento. Este tipo

de enfoque es el que se le está dando hoy en dı́a a la programación. El principal

problema de este estilo de programación es que no ha habido grandes avances

en este área y los compiladores no brindan el soporte suficiente para hacer este

tipo de programación en forma eficiente. El trabajo de subdividir las tareas y

lograr la menor dependencia posible queda pura y exclusivamente a cargo de los

programadores.

Si se lograra hacer aplicaciones que sean cada vez más distribuidas, la eficiencia de los procesadores aumentarı́a significativamente, simplemente incrementando el número de núcleos en un procesador. Como se explicó anteriormente,

en aplicaciones de servidores sı́ es posible distribuir eficientemente la carga de

trabajo en múltiples tareas. Los sistemas computacionales orientados a servidores suelen tener un número grande de núcleos comparados con otro tipo de

sistemas. En ese caso se habla de sistemas de multi-procesadores de gran escala.

La particularidad de estas aplicaciones es que pueden ser divididas en tareas

muy poco acopladas, es decir intercambian poca información entre sı́.

Existen otro tipo de aplicaciones más acopladas, donde el intercambio de

datos es mayor. En este tipo de tareas es donde los programadores tienen un

desafı́o mayor, que es el de dividir procesos en hilos independientes. Estas aplicaciones son comunes en sistemas de escritorio y también en sistemas embebidos.

Los procesadores multi-núcleo son los más populares en este área, y como diremos en breve las tendencias apunta a seguir aumentando en número los núcleos

de un procesador. Los programadores se ven obligados a implementar la programación distribuida en caso de querer implementar aplicaciones con un buen

4 En un procesador con un núcleo de procesamiento y sin multi-threading hay una única

tarea en estado ‘en ejecución’, para uno con dos núcleos hay dos, para los procesadores con

MT depende de la cantidad de contextos que pueda almacenar cada núcleo.

CAPÍTULO 1. INTRODUCCIÓN

16

desempeño, y éste es uno de los principales problemas de la informática hoy en

dı́a.

1.7.

Consumo y frecuencia de trabajo

El consumo de un circuito digital esta dado por [5]:

P otdisipada ∝ f × CL × V 2

Donde CL es una capacidad asociada a los transistores, V es la tensión de

alimentación y f es la frecuencia de trabajo. La limitación para aumentar la

frecuencia de trabajo se basa en la potencia que se puede disipar. Años atrás

alcanzaba con reducir el tamaño de los transistores, y de esa manera se reducı́a

la capacidad y también se bajaba la tensión de alimentación y eso permitı́a

aumentar la frecuencia. Hoy en dı́a existen grandes dificultades para seguir reduciendo el tamaño de los transistores, lo que hace que sea difı́cil aumentar la

frecuencia de trabajo sin que aumente el consumo. Entonces resulta más conveniente aumentar el número de núcleos de procesamiento y hacerlos funcionar

en conjunto.

Otra lı́nea de trabajo que existe hoy en dı́a busca bajar el consumo de los procesadores al mı́nimo. Por ello tampoco siempre se utiliza la máxima frecuencia,

dejando el rendimiento de lado y el consumo pasa a ser la principal preocupación. Los procesadores más nuevos son diseñados con la capacidad de cambiar

la frecuencia de trabajo según el uso que se le este dando al mismo. Cuando se

requiere mayor rendimiento se aumenta la frecuencia de trabajo, mientras que

cuando se quiere un ahorro de energı́a se disminuye.

Otro método que se utiliza para que el rendimiento y consumo de los procesadores sea parametrizable (controlable), es a través del aprovechamiento de

los múltiples núcleos que se tiene en un procesador multi-núcleo. Cuando se

quiere un consumo bajo, se apagan los núcleos que no son necesarios, y cuando

se quieren un rendimiento alto se los enciende. En ocasiones se prefiere tener

un número mayor de núcleos de bajo consumo en vez una menor cantidad de

núcleos de alto rendimiento.

Otro caso especial que se da es implementar procesadores con núcleos asimétricos, con distinto poder de procesamiento y consumo. Dependiendo de la necesidad se utilizan núcleos de alto, mediano o bajo consumo/rendimiento en

conjunto dentro del mismo procesador.

La utilización de todas estas técnicas en conjunto (cambio en la frecuencia de trabajo, asimetrı́a y apagado y encendido de los núcleos) dan lugar a

procesadores de alto rendimiento y muy bajo consumo al mismo tiempo.

1.8.

Conclusiones

Históricamente los enfoques apuntaban a mejorar la arquitectura del núcleo

de procesamiento: Se aumentó la frecuencia de trabajo, se mejoró la tecnologı́a

de fabricación de transistores. Luego se empezó a explotar ILP. Se desarrollo

el pipeline, luego procesadores con multiple issue slots. Posteriormente multithreading y SMT. Las tendencias de hoy en dı́a apuntan a mejorar los multiprocesadores y las técnicas de programación distribuida, lo que a la vez permite

CAPÍTULO 1. INTRODUCCIÓN

17

aumentar el número de núcleos de un procesador, y ésto último impulsa el

desarrollo en mejores técnicas de programación distribuida. Se forma un ciclo

que se realimenta, e impulsa a los procesadores multi-núcleo. Por otro lado el

diseño del núcleo en sı́ ha alcanzado niveles, en los cuales se vuelve difı́cil seguir

avanzando, multiplicar el número de núcleos en vez de rediseñarlos desde el

comienzo resulta conveniente. El consumo de los procesadores se vuelve un factor

muy importante y fomenta también el diseño enfocado a los multi-procesadores.

Y como se dijo antes utilizando este enfoque se puede lograr un bajo consumo

y un gran rendimiento, por eso esta tesis se centra en los multi-procesadores.

CAPÍTULO 1. INTRODUCCIÓN

18

Capı́tulo 2

Teorı́a y diseño

En este capı́tulo se realiza una introducción al procesador plasma junto con

la arquitectura de instrucciones que soporta. Se evalúan las distintas posibilidades para el diseño del multi-procesador. El tema principal del diseño es la

arquitectura de la memoria y la comunicación entre los procesadores. Otros temas secundarios que se tratan son las interrupciones en multi-procesadores y la

dificultad de implementar operaciones atómicas en los mismos. Se fundamentan

las decisiones tomadas, las cuales a lo largo del trabajo apuntan a lograr un

diseño lo más simple posible.

2.1.

Procesador Plasma y arquitectura MIPS

El micro-procesador plasma es un procesador diseñado en VHDL1 , sintetizable, RISC de 32 bits, ejecuta todas las instrucciones de modo usuario de la

ISA MIPS(TM) salvo las de acceso desalineado a memoria2 .

En la página http://opencores.org/project,plasma se puede descargar la última versión de este procesador. Esta implementación incorpora también algunos

periféricos. Fue probado en distintas FPGAs de Xilinx y Altera, pero sobretodo

en FPGAs Spartan-3E de Xilinx, en el kit de Digilent ”Spartan-3E Starter Kit”.

La arquitectura del procesador plasma implementa la unidad de procesamiento

en dos o tres etapas de pipeline a elección, una memoria cache opcional de 4kB.

La frecuencia de trabajo al implementarlo en FPGAs de Xilinx y Altera ha alcanzado los 25MHz y 50MHz dependiendo del modelo de FPGA. Al presente

no fue implementado a nivel de silicio, o al menos no ha sido reportado en la

bibliografı́a consultada.

1 VHDL es el acrónimo que representa la combinación de VHSIC y HDL, donde VHSIC es

el acrónimo de Very High Speed Integrated Circuit y HDL es a su vez el acrónimo de Hardware Description Language. Es un lenguaje definido por el IEEE (Institute of Electrical and

Electronics Engineers) (ANSI/IEEE 1076-1993) usado por ingenieros para describir circuitos

digitales

2 La implementación de las instrucciones de acceso desalineado a memoria no fue posible,

ya que éstas estaban patentadas cuando fue diseñado

19

CAPÍTULO 2. TEORÍA Y DISEÑO

20

MIPS (en inglés Microprocessor without Interlocked Pipeline Stages) es una

ISA (en inglés instructions set architecture) RISC (En inglés reduced instruction

set computer ). Están definidas instrucciones para procesadores de 32 y 64 bits,

y diferentes versiones del set de instrucciones: MIPS I, MIPS II, MIPS III, MIPS

IV y MIPS V.

El set de instrucciones no define en ningún momento la arquitectura del

hardware del procesador, de hecho existen muchas implementaciones distintas

de los mismos, con distintas frecuencias de trabajo, con distinto tamaño de

cache, incluso con pipelines más o menos profundos.

2.2.

Comunicación entre los procesadores

Como se dijo en el capı́tulo 1, surge la necesidad de que los núcleos de los

multi-procesadores se comuniquen entre sı́ para intercambiar datos, lo cual no

sucede en procesadores de un sólo núcleo o mono-procesadores. La comunicación

entre los diferentes procesadores se realiza en general a través de la memoria

que comparten. Existen varias formas de compartir la memoria, lo que depende

de la forma en la que esta está distribuida. Pueden utilizarse buses o una redes

de comunicación, a los cuales se conectan los procesadores y la memoria. En

la figura 2.1 muestran las dos arquitecturas clásicas para la interconexión de

multi-procesadores:

En la arquitectura de shared memory o memoria compartida se observa

que existe una única memoria principal que esta conectada directamente al bus. Todos los núcleos acceden a la memoria a través del bus de

interconexión.

En la arquitectura distributed shared memory o memoria compartida distribuida se observa que la memoria no es única, sino que esta particionada

en bloques, uno por cada procesador, y a la vez se encuentra conectada a

la red de interconexión. Esto implica que dependiendo de la posición de

memoria a la que se quiera acceder un núcleo puede necesitar hacerlo a

través del bus o no y esto difiere núcleo a núcleo.

Las arquitecturas de memoria compartida tiene la particularidad de que el

tiempo de acceso a cualquier posición es independiente del núcleo que quiera

accesarla. Esto se denomina: UMA en inglés Uniform Memory Access. En una

arquitectura de memoria compartida, los núcleos están fuertemente acoplados,

lo que significa que pueden comunicarse entre sı́ a velocidades muy altas, esta

es su principal ventaja. Por otro lado la principal desventaja que presenta, son

las colisiones que se generan en el bus, por ser un bus compartido entre todos

los núcleos. Las colisiones se generan cuando varios núcleos pretendan acceder

al bus simultáneamente. Esto no es posible, ya que mientras un núcleo tiene

acceso, el resto de ellos deben esperar. Las colisiones se incrementan junto con

el aumento de núcleos conectados al bus. Por esta razón el número de núcleos

que pueden compartir un bus, tiene un lı́mite y generalmente es inferior al de

una arquitectura de memoria compartida distribuida.

En las arquitecturas de memoria distribuida compartida los tiempos de acceso a una posición de memoria depende del núcleo que quiera accesarla. Si

el núcleo debe acceder a través del bus o red de interconexión este tiempo

CAPÍTULO 2. TEORÍA Y DISEÑO

21

(a) Arquitectura Shared Memory.

(b) Arquitectura Distributed Shared Memory.

Figura 2.1: Arquitectura Shared Memory - Los procesadores tienen todos

el mismo tiempo de acceso a cualquier posición de memoria, UMA (Uniform

Memory Access). La comunicación puede ser a través de uno o varios buses, o

también a través de un switch.Arquitectura Distributed Shared Memory Los procesadores tienen distintos tiempos de acceso a distintas zonas de memoria, dependiendo si deben acceder a través del bus o no, NUMA (Non Uniform

Memory Access). La comunicación es normalmente a través de una red de comunicación.

es mayor. A este tipo de arquitecturas se las denomina NUMA en inglés Non

Uniform Memory Access. Por otra parte en las arquitecturas de memoria compartida distribuida si el sistema computacional corre un OS, en el cual se van

reprogramando las procesos que se ejecutan en cada procesador, el planificador

de procesos del sistema operativo se vuelve mucho más complejo . Al no ser uniformes los tiempos de acceso, el rendimiento al ejecutar las tareas se ve afectado

dependiendo de que núcleo sea el que ejecute el proceso, lo cual implica que el

sistema operativo no sólo debe decidir que proceso ejecutar, sino también en

cuál de los núcleos. Esta problemática también aparece en los sistemas nombrados en los sistemas asimétricos nombrados en la introducción, donde los núcleos

de procesamiento pueden ser distintos entre sı́. Para esos sistemas también debe

utilizarse un OS complejo que conozca el tipo de procesador que correrá la tarea.

Surge entonces otra clasificación para los procesadores multi-núcleo:

SMP (en inglés Symmetric MultiProcessors): Donde los núcleos son inter-

CAPÍTULO 2. TEORÍA Y DISEÑO

22

cambiables, es decir, se consiguen los mismos resultados al ejecutar una

tarea en uno o en otro núcleo de procesamiento.

AMP (en inglés Asymmetric MultiProcessors): Se obtienen distintos resultados dependiendo de la distribución de las tareas en los distintos procesadores.

En general los SMP tienen una arquitectura de memoria UMA, donde la memoria es compartida y centralizada, y se conectan a través de un bus. Este tipo

de arquitectura se utiliza para número bajo de procesadores ya que al aumentar

el número de procesadores aumentan las colisiones en el bus. Tienen la gran

ventaja de tener un acoplamiento fuerte entre los procesadores, lo cual significa

una gran velocidad de comunicación. Por el contrario las arquitecturas AMP,

cuando la asimetrı́a es producto de la distribución de la memoria, suelen tener

una arquitectura NUMA, donde la memoria es compartida y distribuida y se interconectan a través de una red de comunicación. Los procesadores están mucho

menos acoplados entre sı́, lo cual implica una disminución en la velocidad con la

que se pueden comunicar, se utiliza para aplicaciones donde los procesadores no

deben compartir una gran cantidad de datos y cuando se necesita aumentar el

ancho de banda del sistema hacia componentes externos, o sea discos rı́gidos o

la conectividad a una red, ya que cada núcleo puede tener asociado dispositivos

de entrada/salida locales. Esta arquitectura se observa en la figura 2.1(b).

Este tipo de arquitecturas son las que se utilizan generalmente, pero todo

tipo de combinaciones puede ser válida, como por ejemplo tener una única memoria compartida pero dispositivos de entrada/salida locales a los núcleos, etc.

En el diseño del plasma multi-núcleo se adopta una arquitectura tipo SMP, en el

cual las unidades de procesamiento se conectan a través de un bus, y comparten

una memoria principal, que es accedida a través del mismo. Todos los núcleos

son iguales y están basados en el procesador plasma. Se adopta esta arquitectura

por ser simple y adecuada para las aplicaciones embebidas a las que apunta el

procesador.

2.3.

Bus de interconexión

Una vez decidida la utilización de un bus para la comunicación se debe

evaluar las distintas posibilidades para su diseño. Existen diferentes estructuras

para los buses de comunicación, entre ellas las más conocidas:

Single bus en inglés o bus simple.

Switched bus en inglés o bus switcheado.

En la figura 2.2 se pueden observar estas dos posibilidades. Si se utiliza un bus

simple(figura 2.2(a)), cuando un núcleo accede al bus tiene acceso a todos los

periféricos conectados al mismo,ya sea memoria principal, o cualquier otro periférico. Mientras un núcleo tiene el acceso, el resto de los núcleo que quieran

tomar el control del mismo deberán esperar que el núcleo en cuestión lo libere.

Por el contrario un bus switcheado(figura 2.2(b)) tiene la caracterı́stica de poder

brindar acceso a dos o más núcleos a la memoria principal o a los periféricos,

siempre y cuando no haya dos de ellos tratando de acceder a una misma entidad.

CAPÍTULO 2. TEORÍA Y DISEÑO

NÚCLEO

23

NÚCLEO

NÚCLEO

NÚCLEO

MEMORIA

PRINCIPAL

(a) Bus simple

NÚCLEO

NÚCLEO

NÚCLEO

NÚCLEO

SWITCHED

BUS

BANCO 0

BANCO 1

BANCO 0

BANCO 1

MEMORIA

PRINCIPAL

(b) Bus switcheado

Figura 2.2: Bus simple y switcheado. En un bus simple, sólo un núcleo puede

tener acceso a memoria. Si dos núcleos intentan acceder a memoria, se produce

una colisión. Por el contrario, en un bus switcheado se pueden generar accesos

en paralelo entre los núcleo y los distintos bancos de memoria (si dos núcleos

intentan acceder al mismo banco de memoria, también se produce una colisión).

El resultado es un aumento en el ancho de banda entre los núcleos y la memoria.

En la figura se muestra una de las posibles conexiones entre los núcleos y los

bancos.

En algunos casos la memoria principal se puede dividir en bloques y se implementa un controlador de memoria por cada bloque. De esta manera se puede

aumentar el ancho de banda del bus, ya que permite acceso de dos o más núcleos

(hasta un máximo que depende de la cantidad de bloques o controladores de

memoria) en simultáneo, la restricción para ello es que no quieran acceder al

mismo bloque de memoria. Este bus es considerablemente más complejo, sin embargo es una de las maneras más eficientes de aumentar el rendimiento del bus.

Al aumentar en gran cantidad los núcleos de procesamiento, el bus de conexión

se vuelve un cuello de botella, limitando el rendimiento, en estos casos puede ser

de extrema utilidad cambiar el bus a un bus switcheado y dividir la memoria

principal en bloques. Al hacer uso de esta técnica se aumenta el ancho de banda

entre la memoria y los núcleos y la arquitectura sigue siendo tipo UMA, lo cuál

no es un detalle menor.

CAPÍTULO 2. TEORÍA Y DISEÑO

24

En el plasma multi-núcleo se opta por utilizar un bus simple, ya que en

principio no es necesaria otra estructura más compleja, ya que en este trabajo se pretende implementar procesadores de número relativamente bajo de

núcleos(hasta ocho). Un bus simple tiene la ventaja de permitir mensajes de

broadcast (multidestino), más adelante en este trabajo se discute el beneficio

que brinda utilizar esta estructura al algoritmo de coherencia de cache (que se

ve en la sección 3.7.3).

Al existir muchas entidades que acceden al bus, en necesario controlar los

accesos al mismo. Para nuestro caso particular estas entidades son los distintos

núcleos. Idealmente el acceso al bus deberı́a ser repartido equitativamente entre

todos los procesadores y ninguno de ellos deberı́a tener prioridad, de esta manera

que la ejecución de una tarea sea lo más independiente posible del núcleo en el

que se ejecuta. En el plasma multi-núcleo se implementa un árbitro de bus, que

será el encargado de la tarea de controlar el acceso al bus y repartirlo lo más

equitativamente posible. Su implementación y funcionamiento se describe en la

sección 3.5.

2.4.

2.4.1.

Arquitectura de la memoria

Principio de localidad

El principio de localidad surge de observar una caracterı́stica muy usual: los

programas tienden a reutilizar datos e instrucciones que han sido usadas recientemente. Una regla empı́rica es que los programas pasan un 90 % del tiempo

de ejecución con sólo un 10 % del código [2]. De este modo, a partir del pasado

reciente se puede predecir con bastante precisión que instrucciones y datos un

programa utilizará en un futuro cercano. El principio de localidad es mucho más

fuerte cuando se refiere a instrucciones o código, y no tanto al referirse a datos.

Existen dos tipos de localidad:

Localidad temporal: Es probable acceder en un futuro cercano nuevamente

a posiciones de memoria que han sido accesados recientemente.

Localidad espacial: Posiciones de memoria situadas cercanas a otras accedidas recientemente, tienden a ser accesados en un futuro cercano también.

2.4.2.

Jerarquı́a de la memoria

Al programar siempre se desea disponer de una gran cantidad de memoria

de acceso rápido. Existen memorias rápidas, que tienen un costo es elevado, y

también existen memorias lentas, que tienen un bajo costo, y por otro lado, el

principio de localidad se basa en que el código no es accedido uniformemente,

algunas porciones son utilizadas con mayor frecuencia que otras.

Lo que se busca al jerarquizar la memoria, es utilizar la memorias rápidas

y las de bajo costo en conjunto, procurando que las posiciones de memoria

que tengan mayor probabilidad de ser accedidas se encuentren ubicadas en las

memorias más rápidas. El objetivo es brindar al usuario del sistema la ilusión de

poseer un memoria tan grande como la más económica y tan rápida como la más

cara. En la figura 2.3 se pueden ver los distintos niveles tı́picos de una memoria

jerarquizada. Para aprovechar el costo y el desempeño de los distintos tipos de

CAPÍTULO 2. TEORÍA Y DISEÑO

CPU

MEMORIA

25

Velocidad Tamaño

RÁPIDA

PEQUEÑA

Costo

Ejemplo

COSTOSA

SRAM

DRAM

MEMORIA

MEMORIA

LENTA

GRANDE ECONÓMICA

DISCO

RIGIDO

MAGNÉTICO

Figura 2.3: La esctructura básica de memoria jerarquizada. Se muestra

una memoria dividida en tres niveles, y se caracteriza cada nivel de memoria

según tamaño, costo, velocidad de acceso y una tecnologı́a posible para su fabricación. A medida que la memoria se aleja del CPU, la velocidad y el costo

bajan, mientras que el tamaño aumenta. Al utilizar una memoria jerarquizada,

el programador tiene la ilusión de estar trabajando con una memoria tan grande

como la más económica y tan rápida como la más cara.

memorias se diseñan niveles de memoria que a medida que la memoria se aleja