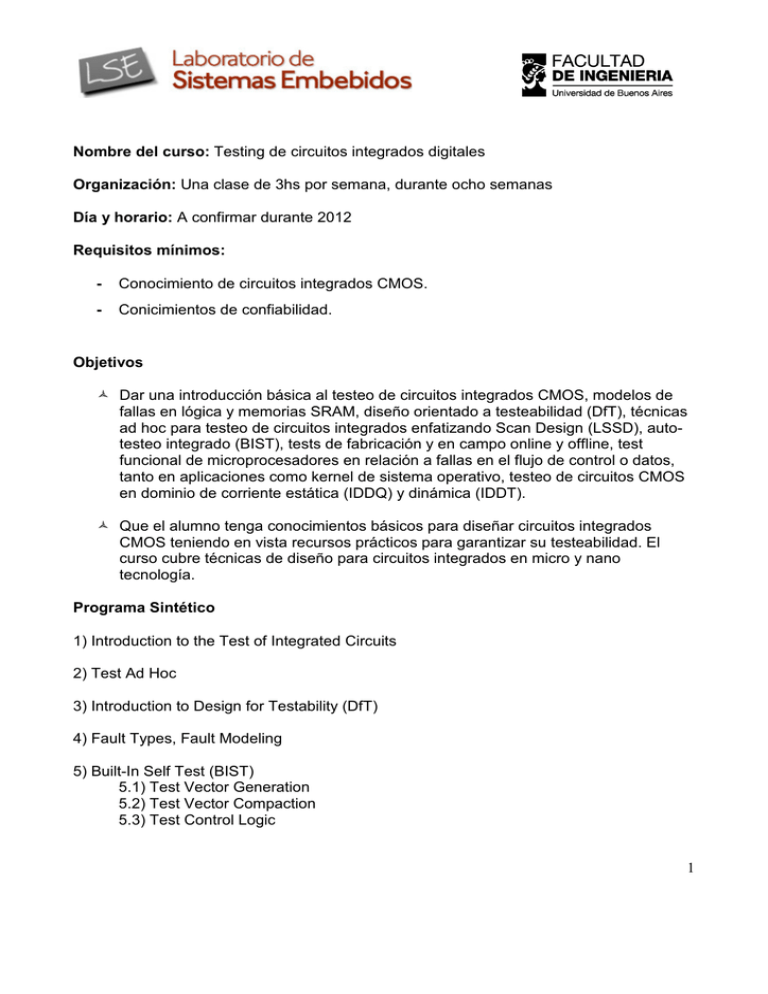

1 Nombre del curso: Testing de circuitos integrados digitales

Anuncio

Nombre del curso: Testing de circuitos integrados digitales Organización: Una clase de 3hs por semana, durante ocho semanas Día y horario: A confirmar durante 2012 Requisitos mínimos: - Conocimiento de circuitos integrados CMOS. - Conicimientos de confiabilidad. Objetivos Ó Dar una introducción básica al testeo de circuitos integrados CMOS, modelos de fallas en lógica y memorias SRAM, diseño orientado a testeabilidad (DfT), técnicas ad hoc para testeo de circuitos integrados enfatizando Scan Design (LSSD), autotesteo integrado (BIST), tests de fabricación y en campo online y offline, test funcional de microprocesadores en relación a fallas en el flujo de control o datos, tanto en aplicaciones como kernel de sistema operativo, testeo de circuitos CMOS en dominio de corriente estática (IDDQ) y dinámica (IDDT). Ó Que el alumno tenga conocimientos básicos para diseñar circuitos integrados CMOS teniendo en vista recursos prácticos para garantizar su testeabilidad. El curso cubre técnicas de diseño para circuitos integrados en micro y nano tecnología. Programa Sintético 1) Introduction to the Test of Integrated Circuits 2) Test Ad Hoc 3) Introduction to Design for Testability (DfT) 4) Fault Types, Fault Modeling 5) Built-In Self Test (BIST) 5.1) Test Vector Generation 5.2) Test Vector Compaction 5.3) Test Control Logic 5.4) Test Planning 5.5) Test Vector Generator Tool for BIST 6) Memory Test: Marching Test, Transparent Test 7) Microprocessor On-Line Test: Control-Flow Fault Detection versus Data-Flow Fault Detection 8) Parametric (Current) Test: IDDQ Test 9) Fault Injection Techniques Bibliografía: Ó "Electronic Design Automation: Synthesis, Verification and Test (Systems on Silicon)". Laung-Terng Wang, Yao-Wen Chang, Kwang-Ting (Tim) Cheng. Morgan Kaufmann, 2009. Ó Papers from the IEEE Xplore Digital Library.