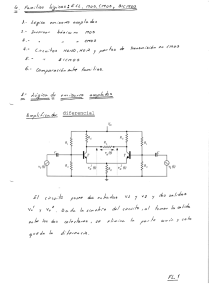

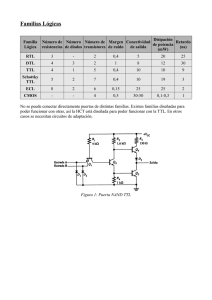

República Bolivariana de Venezuela Universidad Nacional Experimental Politécnica “Antonio José de Sucre” Vice-Rectorado “Luis Caballero Mejías” Caracas Profesor: Francisco Ledo Alumno: Valero Katherin 2014203042 INTRODUCCION: Lógica es la base de todos los argumentos racionales. Los Griegos reconocieron su papel en matemáticas y filosofía, y lo estudiaban extensivamente. Aristóteles, en el, Organon, escribió el primer tratado sistemático sobre lógica. Su trabajo en particular tuvo una gran influencia sobre la filosofía, ciencia y religión durante la edad media. En el siguiente trabajo veremos la interconexión de la interfaz de On semiconductor ECL, dispositivos con lógica de modo actual (CML) SALIDA, los TTL (TRANSISTOR LOGICA TRANSISTOR), Y los CMOS (SEMICONDUCTOR COMPLEMENTARIO DE METAL-OXIDO) se caracterizan porque la función que realizan se puede cambiar mediante la programación de las conexiones entre los elementos que los componen, lo cual se conoce como configurabilidad. ECL-CML La lógica de modo actual (CML), o lógica acoplada a la fuente (SCL), es una familia lógica digital diferencial diseñada para transmitir datos a velocidades entre 312.5 Mbit / sy 3.125 Gbit/ s a través de placas de circuito impreso estándar Orígenes: Los orígenes de CML son más difíciles de rastrear. CML tiende a ser principalmente un vendedor implementación con menos estandarización oficial. Esto hace que sus raíces sean más difíciles de rastrear. Algunos afirman que antecede a ECL con orígenes en General Electric, otros señalan que surgió de I2L, (Injection Current Logic), o CCSL (lógica de hundimiento de corriente compatible) en la década de 1980. Todavía otros afirman algunos trabajos a principios de la década de 1990 como su fuente. Muchos otros lo ven como simplemente ECL al revés. Hoy la CML se ha hecho muy popular debido a su simplicidad y velocidad especialmente para aplicaciones SerDes multigigabit. CML es una interfaz punto a punto de alta velocidad Una característica única de CML es que normalmente no requiere resistencias externas ya que la terminación se proporciona internamente tanto por el controlador como por los dispositivos receptores. Hay muchas tecnologías de señalización diferencial disponibles en la actualidad. Algunos están definidos por el estándar de la industria comités, como los grupos TIA, IEEE o JEDEC. Otros son sabores más "específicos del vendedor" y pueden tener características eléctricas únicas. Ambos tipos fueron desarrollados por diferentes razones, algunos se centran en ultra velocidad como ECL y CML, mientras que otros se enfocaron en dos o más atributos. LVDS, por ejemplo, centrado en funcionamiento a alta velocidad y bajo consumo. Esto es lo que debes saber sobre algunos de los populares de hoy. Tecnologías de interfaz diferencial de alta velocidad: Las tres tecnologías populares de interfaz de alta velocidad que se analizan son: LVDS Diferencial de bajo voltaje, opciones de señalización, ECL - Lógica acoplada del emisor y PECL / LVPECL CML - Lógica de modo actual Tres para velocidad: ECL - LVDS - CML ECL (Emisión de lógica acoplada) es el más antiguo de los tres y se remonta a principios de los años sesenta. Motorola pionero. ECL con su familia MECL (Motorola ECL). Desde entonces, ECL se ha convertido en muchas familias mejoradas. Estas incluye 10k, 100k, ECLinPS e incluso algunos sabores más recientes, como RSECL para ECL de giro reducido, que cuenta con un LVDS similar a 400 mV, salida swing. Fairchild, también un pionero de ECL, sacó el primer subnano, segundas partes de la ECL a principios de los años setenta. La familia 100k trajo la característica crítica de la tensión de alimentación y compensación de temperatura, proporcionando una salida muy estable. ECL se puede utilizar de forma única o diferencial. Dependiendo de la aplicación y los márgenes de ruido necesarios. Los controladores son salidos de emisor abierto de baja impedancia que generan un voltaje de salida típico de 700 a 800 mV. La etapa de salida se opera en la región activa, saturación se evita, por lo que se obtienen las famosas tasas de borde rápidas y equilibradas de ECL. La salida se termina típicamente con 50 ohmios a un riel de terminación que es dos voltios menos que el riel más positivo. Las piezas de ECL son comúnmente. Alimentado entre tierra y -5.2V. Debido al requisito de carril negativo y la compatibilidad con otros populares dispositivos (lógica, ASIC, mP ...), se promovió la operación ferroviaria positiva de ECL. PECL - Emisor Positivo Acoplado la lógica, también conocida en algún momento como Pseudo ECL, en realidad es solo operar los dispositivos ECL entre y positivo. Tensión y tierra, vs tierra y una tensión negativa. LVPECL - PECL de bajo voltaje es el término usado para describir PECL que se alimenta de una fuente de alimentación de 3.3V. Incluso hay otras versiones disponibles hoy que soportan. Operación desde rieles de menos de 3.3V. Esquema de terminación CML La transmisión es de punto a punto, unidireccional, y por lo general se termina en el destino con 50 Ω resistencias a V cc en ambas líneas diferenciales. CML se utiliza con frecuencia en interfaces para componentes de fibra óptica. Las señales CML también se han encontrado útiles para conexiones entre módulos. CML es la capa física utilizada en los enlaces de video DVI y HDMI , las interfaces entre un controlador de pantalla y un monitor. Además, la CML se ha utilizado ampliamente en sistemas integrados de alta velocidad, como los sistemas de telecomunicaciones, tales como: transceptores de datos en serie, sintetizadores de frecuencia Operación: El funcionamiento rápido de los circuitos de CML se debe principalmente a su menor oscilación de voltaje de salida en comparación con los circuitos estáticos de CMOS , así como a la muy rápida conmutación de corriente que tiene lugar en los transistores de par diferencial de entrada. Uno de los requisitos principales de un circuito lógico de modo actual es que el transistor de polarización de corriente debe permanecer en la región de saturación para mantener una corriente constante. Ultra baja potencia: Recientemente, CML se ha utilizado en aplicaciones de potencia ultra baja. Los estudios demuestran que si bien la corriente de fuga en los circuitos CMOS estáticos convencionales se está convirtiendo en un desafío importante para reducir la disipación de energía, un buen control del consumo de corriente CML los convierte en un muy buen candidato para un uso de energía extremadamente bajo. Llamado por debajo del umbral CML o por debajo de la fuente de lógica acoplada (STSCL), [3] [4] [5] el consumo de corriente de cada compuerta se puede reducir a unas pocas decenas de picoAmps. TTL Historia: El término "TTL" se aplica a muchas generaciones sucesivas de lógica bipolar , con mejoras graduales en la velocidad y el consumo de energía durante aproximadamente dos décadas. La familia 74Fxx más recientemente introducida todavía se vende hoy, y fue ampliamente utilizado hasta finales de los 90. 74AS / ALS Advanced Schottky se introdujo en 1985. A partir de 2008, Texas Instruments continúa suministrando los chips de uso más general en numerosas familias de tecnología obsoleta, aunque a precios más altos. Normalmente, los chips TTL integran no más de unos cientos de transistores cada uno. Las funciones dentro de un solo paquete generalmente van desde unas pocas puertas lógicas hasta un segmento de bits de microprocesador. TTL también adquirió importancia debido a que su bajo costo hace que las técnicas digitales sean económicamente prácticas para tareas previamente realizadas por métodos analógicos. El Kenbak-1 , antepasado de las primeras computadoras personales , usó TTL para su CPU en lugar de un chip microprocesador , que no estaba disponible en 1971. El Datapoint 2200 de 1970 usó componentes TTL para su CPU y fue la base para la 8008 y más tarde el conjunto de instrucciones x86. Las estaciones de trabajo 1973 de Xerox Alto y 1981 Star , que introdujeron la interfaz gráfica de usuario , utilizaron circuitos TTL integrados a nivel de unidades lógicas aritméticas(ALUs) y bitslices, respectivamente. La mayoría de las computadoras utilizaron " lógica de pegamento " compatible con TTL entre chips más grandes hasta bien entrada la década de 1990. Hasta el advenimiento de la lógica programable, la lógica bipolar discreta se usaba para crear prototipos y emular las microarquitecturas en desarrollo. Los circuitos integrados TTL (IC) se usaron ampliamente en aplicaciones tales como computadoras, controles industriales, equipos e instrumentos de prueba, electrónica de consumo y sintetizadores. A veces, los niveles lógicos compatibles con TTL no están asociados directamente con los circuitos integrados TTL, por ejemplo, se pueden usar en las entradas y salidas de los instrumentos electrónicos. (Un reloj en tiempo real construido con chips TTL alrededor de 1979) ¿Qué son los TTL? TTL (Time to Live) es una configuración para cada registro de DNS que especifica durante cuánto tiempo se supone que un resolutor debe almacenar en caché (o recordar) la consulta de DNS antes de que caduque la consulta y se deba realizar una nueva. Es una familia lógica construida a partir de transistores de unión bipolar. Su nombre significa que los transistores realizan tanto la función lógica (el primer "transistor") como la función de amplificación (el segundo "transistor"); es la misma convención de denominación utilizada en la lógica de resistencia-transistor (RTL) y la lógica de diodo-transistor (DTL). TTL son las siglas de Transistor-Transistor Logic . Es el sistema basado en la combinación de transistores de tal manera que se pueden utilizar para puertas lógicas. Los transistores tienen la capacidad de convertirse en partes de dispositivos muy complejos cuando se combinan. Un microprocesador promedio usa más de 40 millones de transistores. Sin embargo, los transistores en microprocesadores son microscópicos en comparación con los componentes discretos utilizados en la electrónica de consumo y las placas de circuitos. La puerta NOT funciona invirtiendo la entrada. La versión TTL de la compuerta NO contiene un transistor, como se muestra a continuación: Cuando la entrada, A, es alta (+ 5V), la base del transistor está saturada, lo que permite que la corriente fluya desde el colector del transistor hasta el emisor. Dado que esto es posible, la corriente no toma el camino de mayor resistencia a través de la salida (asumiendo que tiene una carga resistiva unida a ella, como un LED). Cuando la entrada es baja (0 V), la corriente no tiene más remedio que salir de la salida A invertida (la A con la línea superpuesta para indicar que está negada). Las dos resistencias en el circuito son para limitar la corriente para no destruir el transistor, y algunas veces puede que ni siquiera se requiera dependiendo del transistor. La lógica transistor-transistor (TTT) es una clase de circuitos integrados que mantienen los estados lógicos y logran la conmutación con la ayuda de transistores bipolares. Una de las características destacadas de las señales lógicas transistortransistor es la capacidad de las entradas de la compuerta a subir al "1" lógico si no se conectan. La lógica transistor-transistor es una de las razones por las que los circuitos integrados son tan ampliamente utilizados, ya que son menos costosos, más confiables y más rápidos que la lógica de resistencia-transistor y la lógica de diodo-transistor. Los beneficios del almacenamiento en caché son bastante obvios: es mucho más rápido revisar el caché de su resolutor local y luego tener que buscar un registro DNS que aún no esté en caché. Esto acelera su experiencia en Internet cuando visita un sitio al que visita con frecuencia (ya que se necesita menos tiempo para completar las búsquedas de DNS) y también ayuda a disminuir la carga en los servidores DNS de todo el mundo. ¿Qué sucede cuando cambia el registro de DNS? Aquí es donde el potencial inconveniente del almacenamiento en caché se hace evidente. Si un registro de DNS se almacena en caché, entonces no se realiza una nueva búsqueda hasta que la caché caduque. Por lo tanto, el resolvedor que tiene el registro en caché no tendrá ninguna manera de averiguar sobre el registro modificado hasta que su caché caduque. Cuando escuchas que alguien menciona que están esperando que se propague el DNS, están esperando que los registros del DNS en caché caduquen en todos los diferentes resolutores que lo buscaron anteriormente. Si tiene un TTL de 1 día en un registro, eso significa que tomaría un día completo para que cualquier cambio se propague por todo el mundo. Un dispositivo lógico transistor-transistor hace uso de transistores con múltiples emisores en puertas que tienen entradas múltiples. Existen diferentes subcategorías o familias para la lógica transistor-transistor, tales como: Lógica transistor-transistor estándar Lógica transistor-transistor rápida Schottky transistor-transistor lógica Lógica transistor-transistor de alta potencia Lógica transistor-transistor de baja potencia Schottky avanzada transistor-transistor lógica Uno de los mayores beneficios del uso de la lógica transistor-transistor es la relativa facilidad en la interconexión de diferentes circuitos y la capacidad de producir funciones lógicas complejas. Esto se debe principalmente a los buenos márgenes de ruido así como a los niveles de voltaje garantizados. La lógica transistor-transistor tiene una buena función de "ventilador en", lo que significa el número de señales de entrada que pueden ser aceptadas por una entrada. La lógica transistor-transistor es en gran medida inmune al daño de las descargas de electricidad estática, a diferencia del CMOS, y también es relativamente económica en comparación con el CMOS. Una desventaja importante de la lógica transistor-transistor es su alto consumo de corriente. Las fuertes demandas de corriente de la lógica transistor-transistor pueden llevar a un funcionamiento inadecuado debido a la conmutación de los estados de salida. Incluso con diferentes versiones de lógica transistor-transistor que consumen menos corriente, todas son todavía competitivas a CMOS. Con la llegada de CMOS, algunas aplicaciones que utilizan TTL han sido sustituidas por CMOS. Sin embargo, la lógica transistor-transistor todavía se usa en aplicaciones ya que son bastante robustas y las puertas son relativamente baratas. Tipos de registro comunes Registro A o AAAA: por lo general, una TTL de 1 hora es un buen compromiso entre permitir cambios rápidos y aprovechar el almacenamiento en caché de DNS mientras alguien visita su sitio. Si los cambios en este registro son frecuentes o deben suceder rápidamente en una emergencia, por lo general puede configurarlo en tan solo 30 segundos. Para las funciones de DNS administradas por DynECT, como Active Failover , Load Balancing y GSLB , puede configurar los TTL entre 30 segundos y 5 minutos. Para registros no críticos que rara vez, si es que tienen que cambiar, es posible que pueda salirse con la posibilidad de tener un TTL en el rango de 12 horas a 1 día. Registro CNAME : en muchos casos, un registro CNAME nunca se modificará (por ejemplo, apuntando a www.example.com al registro A de example.com). En esos escenarios, un TTL de 12 horas a 1 día es un buen compromiso, ya que los beneficios del almacenamiento en caché superan la necesidad de un tiempo de propagación más rápido. Si su registro CNAME podría cambiar (por ejemplo, si está utilizando un CDN), querrá tener un TTL más bajo. Registro MX: los registros MX rara vez cambian, si es que lo hacen, especialmente si está utilizando un proveedor de correo electrónico con un buen historial o tiene mucha redundancia cuando se autoalimenta. Por lo general, puede establecer esto en un TTL de 12 horas o 1 día. Si desea asegurar tiempos de propagación más rápidos en caso de una emergencia, un TTL de 1 a 4 horas es un buen compromiso. Registros TXT: los más utilizados para los registros SPF o DKIM. Por lo general, es seguro establecerlo en el rango de 1 hora a 12 horas ya que rara vez cambian. Al final, ten en cuenta que lo que configuraste para el TTL es con lo que te sientas más cómodo. Se trata de lograr un equilibrio razonable entre un tiempo de propagación rápido y aprovechar el almacenamiento en caché de DNS. Su amable Dyn Concierge estará encantado de ayudarle si tiene más preguntas. CMOS El semiconductor complementario de metal-óxido ( CMOS ) es una tecnología para construir circuitos integrados . La tecnología CMOS se utiliza en microprocesadores, microcontroladores , RAM estática y otros circuitos lógicos digitales. La tecnología CMOS también se utiliza para varios circuitos analógicos , como sensores de imagen ( sensor CMOS ), convertidores de datos y transceptores altamente integrados para muchos tipos de comunicación. Frank Wanlass patentó CMOS en 1963 ( patente de EE . UU. 3,356,858 ) mientras trabajaba paraFairchild Semiconductor . A CMOS también se le conoce como semiconductor de metal-óxido-simetría complementaria ( COS-MOS ). [1] Las palabras "simetría complementaria" se refieren al estilo de diseño típico con CMOS que utiliza pares complementarios y simétricos de transistores de efecto de campo (MOSFET) de tipo p y n de óxido de metal para funciones lógicas. (Inversor CMOS) Los circuitos CMOS utilizan una combinación de transistores de efecto de campo (MOSFET) de tipo pyn tipo metal-óxido-semiconductor para implementar puertas lógicas y otros circuitos digitales. Aunque la lógica CMOS se puede implementar con dispositivos de demostración, los productos comerciales de CMOS son circuitos integrados compuestos de miles de millones de transistores de ambos tipos, en una pieza rectangular de silicio de entre 10 y 400 mm2. El CMOS siempre usa todos los MOSFET en el modo de mejora (en otras palabras, un voltaje de la puerta cero apaga el transistor) (MOSFET) Construcción: Los circuitos CMOS se construyen de tal manera que todos los transistores semiconductores de óxido de metal (PMOS) de tipo P tienen que tener una entrada de la fuente de voltaje o de otro transistor PMOS. De manera similar, todos los transistores NMOS deben tener una entrada desde la tierra o desde otro transistor NMOS. La composición de un transistor PMOS crea una resistencia baja entre su fuente y los contactos de drenaje cuando se aplica un voltaje de compuerta bajo y una resistencia alta cuando se aplica un voltaje de compuerta alto. Por otro lado, la composición de un transistor NMOS crea una alta resistencia entre la fuente y el drenaje cuando se aplica una tensión de compuerta baja y una resistencia baja cuando se aplica una tensión de compuerta alta. CMOS logra la reducción de la corriente complementando cada nMOSFET con un pMOSFET y conectando ambas compuertas y ambos drenajes juntos. Un alto voltaje en las puertas causó que el nMOSFET conduzca y el pMOSFET no conduzca, mientras que un bajo voltaje en las puertas causa lo contrario. Pines de alimentación: Los pines de la fuente de alimentación para CMOS se denominan VDD y VSS, o VCC y tierra (GND), según el fabricante. VDD y VSS son remanentes de circuitos MOS convencionales y representan los suministros de drenaje y fuente. [6] Estos no se aplican directamente a CMOS, ya que ambos suministros son realmente suministros de origen. VCC y Ground son remanentes de la lógica TTL y esa nomenclatura se ha mantenido con la introducción de la línea 54C / 74C de CMOS. Lógica: Puerta NAND en la lógica CMOS: Las funciones lógicas más complejas, como las que involucran puertas AND y OR, requieren la manipulación de las rutas entre puertas para representar la lógica. Cuando una ruta se compone de dos transistores en serie, ambos transistores deben tener baja resistencia a la tensión de alimentación correspondiente, modelando un AND. Cuando una ruta consta de dos transistores en paralelo, uno o ambos transistores deben tener baja resistencia para conectar la tensión de alimentación a la salida, modelando un OR. A la derecha se muestra un diagrama de circuito de una compuerta NAND en la lógica CMOS. Si ambas entradas, A y B, son altas, entonces los dos transistores NMOS (mitad inferior del diagrama) conducirán, ninguno de los transistores PMOS (la mitad superior) conducirá, y se establecerá un camino conductor entre la salida y Vss (tierra), bajando la salida (Puerta NAND en la lógica CMOS) La integración de transistores MOS presentó inicialmente grandes dificultades, derivadas de ser un efecto superficial que es afectado por cualquier impureza o dislocación en la superficie del cristal de silicio; fue preciso desarrollar técnicas de muy alta limpieza ambiental que no estuvieron disponibles hasta mediados de los años 70. Sin embargo, una vez que se dispuso de tales técnicas, las extraordinarias ventajas de los transistores MOS (referidas a autoaislamiento, auto alineamiento, tamaño y consumo) determinaron un rápido desarrollo y difusión de los circuitos integrados digitales MOS. En una primera fase resultó más sencillo integrar transistores MOS de canal P, pero pronto fueron desplazados por los transistores NMOS cuya velocidad de conmutación es apreciablemente mayor (debido a la mayor movilidad de los electrones respecto de los huecos). La utilización de transistores MOS como «resistencias de polarización» permite configurar puertas lógicas utilizando únicamente transistores y reduce considerablemente el área de integración, al prescindir de resistencias integradas de valores relativamente altos. De esta forma, las puertas MOS suponen un nuevo avance cualitativo en la miniaturización de la electrónica digital, reducción que afecta no solamente al tamaño y a la densidad de integración, sino también, y en forma aún más significativa, al consumo. La figura siguiente muestra la evolución de las puertas NMOS en relación con el transistor que actúa como «resistencia de polarización»: En los tres inversores de la figura el transistor superior se encuentra siempre en conducción y equivale a una «resistencia de polarización». Para que dicho transistor superior conduzca se requiere una tensión entre puerta y fuente igual o superior a su tensión umbral: por ello, inicialmente (primer inversor) fueron necesarias dos tensiones de alimentación (V' > VCC + VTO); luego (segundo inversor) se utilizó una sola tensión de alimentación pero la tensión de salida para el 1 quedaba reducida a VCC - VTO. Actualmente las tecnologías NMOS emplean como polarización un transistor MOS de empobrecimiento, en cuyo proceso de integración se crea un canal mediante implantación iónica, de forma que conduce incluso en ausencia de tensión entre puerta y fuente; su tensión umbral es negativa VTO < 0, de modo que para cortar la conducción se requiere una tensión de puerta aún más negativa que destruya el canal. El análisis circuital de los tres inversores es análogo: - para Vi < VTO el transistor inferior se encuentra en corte y el superior comunica a la salida la tensión VCC: Vo = VCC = 1 (si bien en el segundo caso se produce un desplazamiento de dicha tensión: Vo = VCC - VTO ); - para Vi >> VTO el transistor inferior conduce, pero también lo hace el transistor superior: es preciso establecer una relación geométrica entre ambos para que el transistor inferior presente una resistencia mucho menor que el superior y la tensión de salida sea muy pequeña: Vo << 1 V (con lo cual Vo 0). CONCLUSION Por medio de este trabajo pudimos constatar la importancia de radica en los dispositivos lógicos, ya que desde la década de los sesenta los equipos electrónicos digitales se han construidos utilizando circuitos integrados de función lógica fija. Certificamos lo útiles que son los TTL para cualquier equipo que tenga una conexión de red, al igual que los CMOS y los ECL.CML A la vista de esto podemos llegar a la conclusión de que es imprescindible para el diseñador de cada una de estas tecnologías conocerlas a fondo, entendiendo por esto no sólo sus características funcionales sino también el porqué de las mismas. BIBLIOGRAFIA Importancia de los TTL Página web: https://www.seabrookewindows.com/DWOAowYQy/ Historia de los TTL Pagina web: https://es.scribd.com/document/64588136/HISTORIA-Y- EVOLUCION-DELOS-CIs-FAMILIAS-LOGICAS-TTL-COMOS-Y-ECLCUADROS-COMPARATIVOS-ENTRE-SUS-VALORES-DE-FUNCIONAMIENTO Dispositivos lógicos CMOS Pagina web: https://www.monografias.com/trabajos45/familias-logicaselectronica/familias-logicas-electronica2.shtml#estudio La tecnología CMOS Pagina web: http://www.set-up.es/la-tecnologia-cmos/ Dispositivos lógicos ECL-CLM Pagina web: www.ti.com/lit/wp/snla180/snla180.pdf https://ieeexplore.ieee.org/iel5/81/17405/00802823.pdf Modelo y diseño de lógica de modo actual Pagina web: https://www.springer.com/gp/book/9781402028786