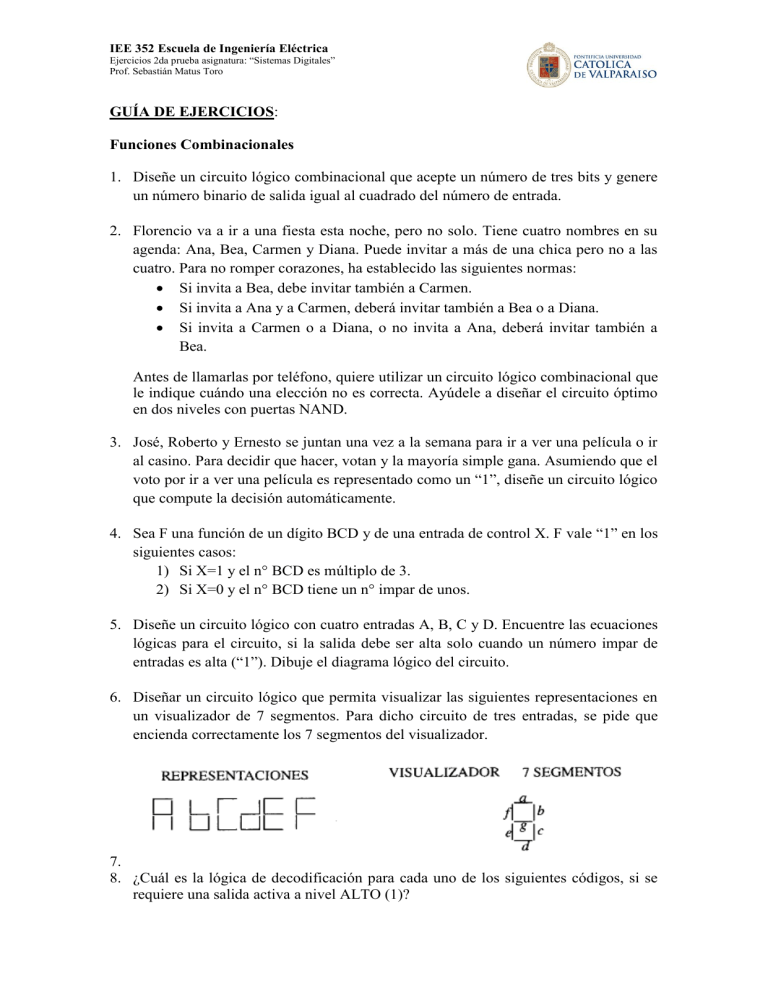

IEE 352 Escuela de Ingeniería Eléctrica Ejercicios 2da prueba asignatura: “Sistemas Digitales” Prof. Sebastián Matus Toro GUÍA DE EJERCICIOS: Funciones Combinacionales 1. Diseñe un circuito lógico combinacional que acepte un número de tres bits y genere un número binario de salida igual al cuadrado del número de entrada. 2. Florencio va a ir a una fiesta esta noche, pero no solo. Tiene cuatro nombres en su agenda: Ana, Bea, Carmen y Diana. Puede invitar a más de una chica pero no a las cuatro. Para no romper corazones, ha establecido las siguientes normas: Si invita a Bea, debe invitar también a Carmen. Si invita a Ana y a Carmen, deberá invitar también a Bea o a Diana. Si invita a Carmen o a Diana, o no invita a Ana, deberá invitar también a Bea. Antes de llamarlas por teléfono, quiere utilizar un circuito lógico combinacional que le indique cuándo una elección no es correcta. Ayúdele a diseñar el circuito óptimo en dos niveles con puertas NAND. 3. José, Roberto y Ernesto se juntan una vez a la semana para ir a ver una película o ir al casino. Para decidir que hacer, votan y la mayoría simple gana. Asumiendo que el voto por ir a ver una película es representado como un “1”, diseñe un circuito lógico que compute la decisión automáticamente. 4. Sea F una función de un dígito BCD y de una entrada de control X. F vale “1” en los siguientes casos: 1) Si X=1 y el n° BCD es múltiplo de 3. 2) Si X=0 y el n° BCD tiene un n° impar de unos. 5. Diseñe un circuito lógico con cuatro entradas A, B, C y D. Encuentre las ecuaciones lógicas para el circuito, si la salida debe ser alta solo cuando un número impar de entradas es alta (“1”). Dibuje el diagrama lógico del circuito. 6. Diseñar un circuito lógico que permita visualizar las siguientes representaciones en un visualizador de 7 segmentos. Para dicho circuito de tres entradas, se pide que encienda correctamente los 7 segmentos del visualizador. 7. 8. ¿Cuál es la lógica de decodificación para cada uno de los siguientes códigos, si se requiere una salida activa a nivel ALTO (1)? IEE 352 Escuela de Ingeniería Eléctrica Ejercicios 2da prueba asignatura: “Sistemas Digitales” Prof. Sebastián Matus Toro a. b. c. d. 1101 1000 11011 11100 e. f. g. h. 101010 111110 000101 1110110 9. Se aplican las formas de onda mostradas en la figura, a las entradas de un comparador de magnitud. Determinar la señal de salida ( A B ). 10. Implementar 𝑓(𝑎, 𝑏, 𝑐) = 𝑎𝑏 + 𝑏̅𝑐 mediante el multiplexor 4 a 1 de la figura siguiente: 11. Diseñe un decodificador 5 a 32 con sólo módulos decodificadores 3 a 8. Suponga que cada decodificador 3 a 8 tiene una entrada de habilitación activa baja ̅̅̅ 𝐸1 , y una entrada de habilitación activa alta 𝐸2 . 12. Implementar la función lógica especificada en la tabla siguiente utilizando un multiplexor/selector de datos de 8 entradas 74HC151. Comparar este método con la implementación discreta con puertas lógicas. Entradas A2 A1 A0 Salida Y IEE 352 Escuela de Ingeniería Eléctrica Ejercicios 2da prueba asignatura: “Sistemas Digitales” Prof. Sebastián Matus Toro 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 0 74HC151 13. Utilizar el mismo multiplexor 74HC151 para implementar la siguiente expresión lógica F1 ( A2 , A1, A0 ) A2 A1 A0 A2 A1 A0 A2 A1 A0 14. Implementar la función 𝑓(𝑋1 , 𝑋2 , 𝑋3 , 𝑋4 ) = ∑ 𝑚(0,1,2,3,9,13,14,15) mediante un MUX 74HC151. 15. Una llamada de teléfono puede dirigirse a cuatro secretarias. (Nunca hay más de una llamada simultáneamente). La recepcionista distribuirá las llamadas según el siguiente criterio: Si la llamada procede de empresas de alimentación o de ropa, se pasa a la secretaria número 4. Si procede de una empresa de venta de computadores, o de un banco, se pasará a la secretaria número 3. Si se trata de una llamada procedente de una empresa de viajes o del aeropuerto, deberá sonar el teléfono de la secretaria número 2. En cualquier otro caso, se enviará a la secretaria número 1. Diseñe un circuito que indique el número de la secretaria que deberá recibir la llamada, utilizando un único codificador 8:3. 16. Realice cada uno de los siguientes conjuntos de funciones con un único módulo decodificador 74154 (4 a 16 líneas con dos entradas habilitadoras de nivel bajo) y lógicas de salida. a) 𝑓1 (𝑎, 𝑏, 𝑐, 𝑑) = ∑ 𝑚(2,4,10,11,12,13) b) 𝑓2 (𝑎, 𝑏, 𝑐, 𝑑) = ∏ 𝑀(0,1,2,3,6,7,8,9,12,14,15) c) 𝑓3 (𝑎, 𝑏, 𝑐, 𝑑) = 𝑏̅𝑐 + 𝑎̅𝑏̅ 𝑑 17. Diseñe un módulo sumador completo con entradas de datos A y B, acarreo de entrada Cin, salida de suma S y de salida Cout. IEE 352 Escuela de Ingeniería Eléctrica Ejercicios 2da prueba asignatura: “Sistemas Digitales” Prof. Sebastián Matus Toro a) Utilice un decodificador 3 a 8 y compuertas NAND. b) Utilice un multiplexor de 4 entradas (2 bits de selección) y lógica de salida. 18. Diseñe un sumador con acarreo en cascada de 16 bits, utilizando sólo módulos sumadores 7483 (sumador de 4 bits, salida a 4 bits, acarreo de entrada y acarreo de salida). 19. Diseñe un módulo restador completo de 1 bit, con sólo compuertas NOR, y después construya un restador de 4 bits que sólo utilice estos módulos. 20. Con las compuertas adecuadas y un comparador 7485 (comparador de magnitud de 4 bits con salidas A>B, A=B y A<B), diseñe un circuito que compare dos números binarios de 5 bits A=(a4…a0) y B=(b4…b0), con f3=1 cuando A>B, f2=1 cuando A=B y f1=1 cuando A<B. (Sugerencia: Utilice las entradas en cascada y compuertas adicionales para comparar los dos dígitos menos significativos) 21. Si se aplican las formas de onda de entrada a la lógica de decodificación de la figura, dibujar las formas de onda de salida en función de dichas entradas. 22. Un decodificador/excitador de 7-segmentos controla el display de la figura. Si se aplican las formas de onda de entrada que se muestran, determinar la secuencia de dígitos que aparece en el display. Latches, Flip-flops y Temporizadores IEE 352 Escuela de Ingeniería Eléctrica Ejercicios 2da prueba asignatura: “Sistemas Digitales” Prof. Sebastián Matus Toro 1. Determinar las salidas Q y Q de un latch S-R con entrada de habilitación para las entradas de la figura mostrada. Dibujarlas en función de la entrada de habilitación. Suponer que, inicialmente, Q está a nivel BAJO. 2. Para un flip-flop J-K disparado por flanco positivo cuyas entradas son las que se muestran en la figura siguiente, determinar la salida Q en función del reloj. Suponer que, inicialmente, Q está a nivel BAJO. 3. En un latch D con entrada de habilitación, se observan en sus entradas las formas de onda de la figura siguiente. Dibujar el diagrama de tiempos, mostrando la forma de onda de salida que se esperaría observar en Q si el latch se encuentra inicialmente en estado RESET. 4. Determinar la salida Q en función del reloj si las señales que se encuentran en la figura se aplican a las entradas de un flip-flop J-K. Suponer que Q se encuentra inicialmente a nivel BAJO. 5. Obtenga las formas de onda de los estados internos y las salidas 𝑍1 y 𝑍2 (justifique las transiciones). Suponga que el sistema parte del estado inicial (𝑄1, 𝑄2 ) = (0, 0). IEE 352 Escuela de Ingeniería Eléctrica Ejercicios 2da prueba asignatura: “Sistemas Digitales” Prof. Sebastián Matus Toro 6. Para el circuito de la figura, dibuje la forma de onda de la salida y los estados internos para las secuencias que se muestran. Suponga que el sistema parte del estado (q1 , q2 , q3 ) (0,0,0) . IEE 352 Escuela de Ingeniería Eléctrica Ejercicios 2da prueba asignatura: “Sistemas Digitales” Prof. Sebastián Matus Toro 7. Para el circuito dibuje la señal de salida: