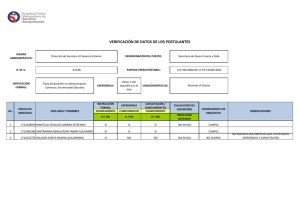

Perspectiva de Alto Nivel del Funcionamiento y de las interconexiones del computador Capítulo 3 Fecha de presentación Debemos poder contestar las preguntas, Qué aspectos de diseño son los que permite que los componentes del computador pueda realizar sus funciones básicas. Podemos describir los conceptos que permiten manejar y controlar la gestiones de proporciona las estructuras arriba señaladas. Componentes del Computador Actuales. Datos • Su diseño se basa en el diseño de creado por John von Neumann, en el Instituto de Secuencia de Resultados funciones lógicas y aritméticas Programación Hardware Estudios Avanzados de Priceton (Institute for Advances Studies Priceton) conocido como IAS. Los Tres conceptos Básicos: o Los datos y las instrucciones se almacenan en Códigos de instrucción una sola memoria de lectura-escritura. o Los contenidos de esta memoria se direccionan Señales de control indicando su posición, sin considerar el tipo de dato contenido en la misma. o La ejecución se produce siguiendo una secuencia de instrucción tras instrucción (a no ser que dicha secuencia se modifique explícitamente). Secuencia de funciones lógicas y aritméticas Datos Resultados Secuencia de funciones lógicas y aritméticas Programación Software ¿Cómo se suministran las Señales de Control? • El programa se realmente una secuencia de pasos. Para cada paso, se requiere un nuevo conjunto de CPU PC MAR señales de control. • Se asocia un código específico a cada posible MBR IR E/S AR conjunto de señales de control. Se añade al hardware de uso general una parte encargada de generar las señales de control a partir del código. • Unidad de ejecución E/S BR En vez de tener que reconfigurar el hardware para cada programa, se necesita es proporcionar una nueva secuencia de códigos, una instrucción, y una Modulo de E/S parte del hardware interpreta cada instrucción y genera las señales de control. • Elementos necesarios: o Un Intérprete de instrucciones y o Un módulo de uso general para las funciones aritméticas y lógicas. .. . Registros Bus del Sistema . . . Instrucción Instrucción 0 1 2 . . . . . . Datos Datos . . . . . . n-2 n-1 PC= Ctrl. de prog. IR= Reg. de inst. MAR= Reg. dir. mem. MBR=Reg. buff. mem. E/S AR= Reg. dir. E/S E/S BR= Reg. buff. E/S Funcionamiento del computador • El procesador se encarga de ejecutar las instrucciones especificadas en el programa. La forma más simple consta de dos etapas: Ciclo de captación • • Ciclo de ejecución El procesador lee (capta) la instrucción de memoria. Ejecuta. Esto consiste en la repetición del proceso de captación y ejecución de instrucción. El Procesamiento que requiere una instrucción se denomina ciclo de instrucción. • Ciclo de ejecución se para solo si: o La máquina se Desconecta. o Se produce algún tipo de Error Irrecuperable o Ejecuta una instrucción del programa que Detiene al computador. Ciclo de captación Ciclo de ejecución Los Ciclos de Captación y Ejecución. Inicio de Ciclo de instrucción. El CPU capta una instrucción de Memoria, utiliza el reg. PC Codop • • (Program Counter) para seguir la pista de las instrucción que 0 0 1 3 4 debe captarse a continuación e incrementa PC (prox dir. mem.) requerida.) Cuatro Tipos de Etapas que puede realizar: o Procesador – Memoria: Debe transferir datos desde CPU a MEM o viceversa. o Procesador – E/S: Debe transferir datos a o desde Medio externo y Magnitud realizarla CPU. La CPU interpreta y lleva a cabo la acción Dirección IR (“código binario” que especifica la acción que debe Formato de enteros La instrucción captada se almacena en el reg. de CPU llamado Formato de instrucción • CPU. o Procedimiento de Datos: Realiza operaciones aritmética o lógica con los datos. o Control: Especifica la cual será la siguiente acción. 15 15 Estados del Ciclo de Instrucción. Captación de instrucción Almacenamiento de operando Captación de operando Varios resultados Varios operandos Calculo de la dir. de instrucción Decodificación de la operación de la instrucción Cálculo de la dir. de operando Instrucción completada captar siguiente instrucción Operación con datos Cálculo de la dir. de operando Cadena o vector de datos Nota: Algunos estados pueden no darse y otros pueden visitarse más de una vez. Estados del Ciclo de Instrucción. • Cálculo de la dirección de la instrucción (IAC): Determina la dirección de la siguiente instrucción a ejecutar, sumando un número fijo a la dirección de la instrucción previa, dependiendo del tamaño de la instrucción (dir. de la instrucción) y el tamaño de la palabra de la memoria. • Captación de instrucción (if): La CPU lee la instrucción desde su posición en memoria. • Decodificación de la operación indicada en la instrucción (IOD): Analiza la instrucción para determinar e tipo de operación a realizar y el (los) operando(s) a utilizar. • Cálculo de la dirección del operando (OAC): Si la instrucción implica una referencia a un operando en memoria o disponible mediante E/S, determina la dirección del operando. • Captación de operando (OF): Capta el operando desde memoria o se lee desde el dispositivo de E/S. • Operación con los datos (DO): Ciclo de Instrucción Operación con los datos • DO, data operation Alamacenamiento de operando • OS, operand store Interrupciones Programa Temporización E/S Fallo de hardware • Generadas por alguna condición que se produce como resultado de la ejecución de una instrucción. • Generadas por un temporizador interno al procesador, OS. • Generadas por un controlador de E/S, indicando la finalización sin problema o avisando cierta condiciones de error. • Generadas por un fallo tal como la falta de potencia de alimentación o un error de paridad en la memoria. Las Interrupciones y el ciclo de instrucción Permite al procesador realizar otras instr. mientras una operación E/S está en curso. Mientras el disp. Externo está ocupado acept. datos de mem. este proceso es concurrente con la ejec. de instr. de usuario Las llamadas al Prog. E/S están constituidas solo por el cód. de preparación y la orden de E/S Cuando el disp. ext. Pasa a estar preparado para actuar, envía una señal de petición de interrupción Funcionamieto de las E/S • Puede intercambiar datos directamente con el Prog. de usuario Gestor de interrupción X procesador. • El procesador puede iniciar una lectura o escritura en memoria, especificando la dirección de un aposición de ella. • El procesador puede leer o escribir datos de (o en) un módulo de E/S determinado. En algunos ocasiones se permiten intercambios de E/S directamente a memoria, cediendo el procesador la autoridad para leer de o escribir en memoria a un módulo de E/S esto recibe el nombre de Acceso directo a memoria DMA (Direct Memory Access). Gestor de interrupción Y Leer Estructura de Interconexión • Dirección El conjunto de líneas que conectan los diversos módulos se denomina estructura de interconexión. Su diseño dependerá de los intercambios que deban producirse entre los módulos. • Escribir Los tipos de intercambios que se necesita indicando las Datos Leer Escribir formas de las entradas y las salidas por módulos: • Memoria: constituido por N palabras de la misma longitud, a esta se le asigna una única dirección numérica (0,1,…, n-1); se puede leer de o escribirse a la memoria utilizando las señales de control Read (leer) y Write Dirección Datos inter. MEM N Palabras 0 . . . N-1 Datos Módulo de E/S Datos inter. M Puertos Señales de interrup. Datos exter. Datos exter. (escribir) y la posición de memoria se especifica mediante una dirección. • Módulo de E/S: es similar a la memoria, hay dos tipos Instrucciones de operaciones, leer y escribir, y puede controlar más de un dispositivo externo. A los cuales nos referimos a ellos como puertos (port), asignadoles direcciones (0,1, …,M-1) accedidas a través de Señales de Interrupción. Datos Señales de interrup. Dirección CPU Señales de control Datos Estructura de Interconexión • Procesador: el procesador lee instrucciones y datos, escribe datos una vez los ha procesado, y utiliza señales para contralar el funcionamiento del sistema. Así también puede recibir señales de interrupción. • Tipos de Transferencias: o Memoria a procesador: el procesador lee una instrucción o un dato desde la memoria. o Procesador a memoria: el procesador escribe un dato en la memoria. o E/S a procesador: el procesador lee datos de un dispositivo de E/S a través de un módulo de E/S. o Procesador a E/S: el procesador envía datos al dispositivo de E/S. o Memoria a E/S y viceversa: para ambos casos, un módulo de E/S puede intercambiar datos directamente con la memoria, sin que tengan que pasar a través del procesador, utilizando el acceso directo a memoria (DMA). Interconexión con Buses • Es un camino de comunicación entre dos o más dispositivos y se caracteriza por ser un medio de transmisión compartido, conectado a varios dispositivos; cualquier señal transmitida por uno de esos dispositivos está disponible para que los otros dispositivos conectados al bus puedan acceder a ella. • No se permite la transmisión simultaneas de dos dispositivos, esto puede causar un solapamiento o distorsión de la señal. • El bus esta constituido por varios caminos de comunicación, o líneas. Cada una capaz de transmitir señales binarias, en un intervalo de tiempo; se puede transmitir una secuencia de dígitos binarios a través de una única línea. • Se pueden utilizar varias líneas de bus para transmitir dígitos binarios simultáneamente (en paralelo). • Existen varios tipos de buses que proporcionan comunicación entre sus componentes a distintos niveles dentro de la jerarquía del sistema. • El bus que conecta los componentes principales del computador se denomina bus del sistema (system bus) ESTRUCTURA DEL BUS CPU E/S MEMORIA Bus E/S MEMORIA