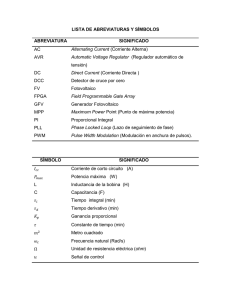

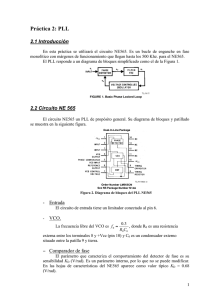

Elementos de sistemas de telecomunicaciones MEMORIA DE LA PRÁCTICA DEL PLL [Escriba el subtítulo del documento] Cristian Sánchez Cobo 2015 OBJETIVOS El objetivo principal de la práctica es haber entendido el funcionamiento de los PLL para aplicarlo en la misma y sus aplicaciones como osciladores PLL, ya sean como: generación de osciladores locales en recepción, sintetizadores de frecuencia, generadores de portadoras para emisión con modulación de ángulo o no, recuperación de impulsos de reloj en transmisiones digitales, demoduladores de señales moduladas en ángulo, recepción de señales satelitales de satélites no geoestacionarios etc. Definicion Los lazos de seguimiento de fase, bucles de enganche de fase, o PLL (del inglés phase-locked loop) son dispositivos muy populares en electrónica desde la década de 1960. Se trata de un sistema en el que la frecuencia y la fase son realimentados. Principio de Funcionamiento El VCO (Voltage Controlled Oscilator) oscila libremente a una frecuencia, determinada por una red RC o LC, llamada frecuencia de corrida libre Ff (free frequency). Esta frecuencia es comparada con la frecuencia Fs de una señal de referencia en el detector de fase (que se comporta como un mezclador cuando excede su rango lineal), el cual entrega la mezcla de ambas Fs-Fo o Fo-Fs dependiendo cual es mayor. Los productos de alta frecuencia tal como Fs+Fo, 2Fs, 2Fo, etc. son eliminados por el filtro pasabajos F(s). Si la frecuencia de la señal Ve (Fs-Fo o Fo-Fs) es lo suficientemente baja para que el filtro pasabajos no la atenúe ni la desfase en exceso, Vd controlará el VCO, tendiendo a reducir la diferencia de frecuencias hasta que se igualen. Una vez que se sincronizan Vo y Vs, esto es Fo = Fs, el detector de fase entrega una tensión Ve, con una componente continua estable necesaria para que el VCO iguale la frecuencia de la señal de referencia. En este caso se establece una diferencia de fase θd para producir la tensión Ve. Estados de funcionamiento Estado de Corrida Libre: Esta condición ocurre cuando no hay señal de entrada o hay una señal de entrada a la cual el lazo no tiene posibilidades de enganchar. En esta condición, generalmente Vd = 0 o Vd ≈ VDD /2, cuando el chip es alimentado con una fuente de tensión VDD no partida. Estado Fijo: Es el que corresponde cuando el lazo está enganchado en fase. Fo = Fs salvo una diferencia finita de fase θd. Cuando un lazo está enganchado por cada ciclo de la señal de entrada, hay uno y solo un ciclo de la señal de salida. Si el comparador de fase no excede su rango lineal se asegura el cumplimiento de esta condición. Estado de Captura: Es el estado previo al fijo, es cuando el VCO está cambiando de frecuencia, intentando enganchar la frecuencia de la señal de referencia. Rangos de Funcionamiento Es conveniente definir los rangos de funcionamiento a partir de las variaciones de Vd cuando se varía la frecuencia de la señal de referencia. Hold in o rango de bloqueo: Parte del PLL enganchado. Es el margen de frecuencias para las que el PLL puede seguir a la entrada para variaciones muy lentas de ésta. Pull out: Es el margen de frecuencias para las que ante un salto brusco de la frecuencia de entrada el PLL no se desengancha. Lock in: Parte del PLL desenganchado. Es el margen de frecuencias en el que el PLL puede engancharse en menos de un periodo de la frecuencia de la señal de salida. Pull in o rango de captura: Es el margen de frecuencia para los que el PLL puede, con un tiempo mayor al periodo de la salida, llegar a engancharse. Materiales Todas las herramientas necesarias están distribuidas por software con un programa simulador de circuitos electrónicos como es el caso de Multisim debido a la falta de pruebas (datos guardados y fotos) de la práctica en placa. - Lo primero, un circuito con el oscilador 4046 integrado donde podemos encontrar: el oscilador 4046, cable, condensadores de distintos valores (1nF, 1nF, 1nF, 10nF, 100nF, 10uF), resistencias de distintos valores (3,3 K omnios y otra de 471 omnios) las debidas tomas a tierra. - Demás herramientas de la práctica: osciloscopio, generador de funciones, Montaje del circuito con el 4046 Preparamos el circuito con el 4046 conectandolo al generador de funciones y al oscilador para observar las señales recibidas , como observamos en la imagen el generador de funciones esta conectado al oscilador por el patillaje 14 de entrada logicamente y el osciloscopio a las patillas 2 y 9 (salida) para obtener las dos señales busquadas. E introducimos a modo que se vea por el osciloscopio una señal cuadrada de 4 voltios pico a pico a través del generador de funciones por lo que saldrá una segunda señal creada por el PLL intentando reproducir en fase la señal introducida al circuito. Rango de funcionamiento Ahora procederemos a medir ¨Lock in¨ que como ya hemos expuesto antes desenganchamos parte del PLL. Ajustando su frecuencia de 450KHz y volviéndolo a conectar para observar si el PLL bloquea la señal de entrada y así obtener el margen de frecuencias en el que el PLL puede engancharse en menos de un periodo de la frecuencia de la señal de salida. Repetimos este proceso a 250 kHz hasta que haya leído 2,5 MHz. De este resultado nos puede calcular y anotar la captura de este PLL.