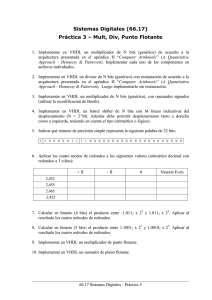

Plan de estudios Electiva I - Diseño Digital Secuencial

Anuncio

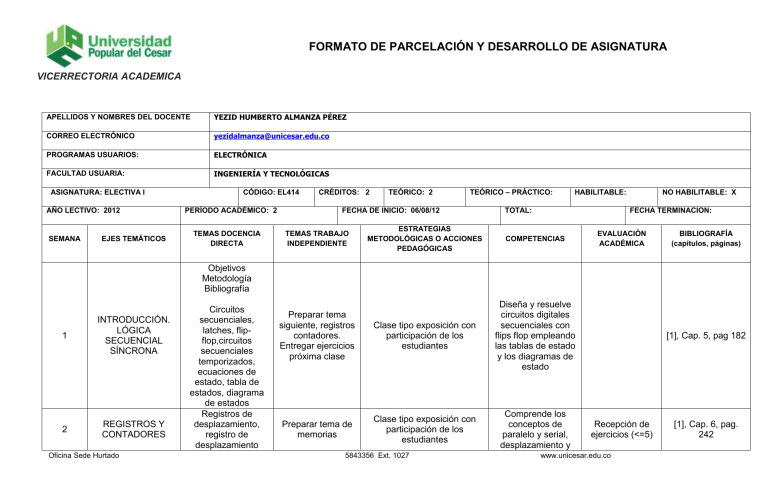

FORMATO DE PARCELACIÓN Y DESARROLLO DE ASIGNATURA VICERRECTORIA ACADEMICA APELLIDOS Y NOMBRES DEL DOCENTE YEZID HUMBERTO ALMANZA PÉREZ CORREO ELECTRÓNICO yezidalmanza@unicesar.edu.co PROGRAMAS USUARIOS: ELECTRÓNICA FACULTAD USUARIA: INGENIERÍA Y TECNOLÓGICAS ASIGNATURA: ELECTIVA I AÑO LECTIVO: 2012 SEMANA EJES TEMÁTICOS CÓDIGO: EL414 PERÍODO ACADÉMICO: 2 TEMAS DOCENCIA DIRECTA CRÉDITOS: 2 TEÓRICO: 2 TEÓRICO – PRÁCTICO: FECHA DE INICIO: 06/08/12 HABILITABLE: TOTAL: FECHA TERMINACION: ESTRATEGIAS METODOLÓGICAS O ACCIONES PEDAGÓGICAS COMPETENCIAS Preparar tema siguiente, registros contadores. Entregar ejercicios próxima clase Clase tipo exposición con participación de los estudiantes Diseña y resuelve circuitos digitales secuenciales con flips flop empleando las tablas de estado y los diagramas de estado Preparar tema de memorias Clase tipo exposición con participación de los estudiantes Comprende los conceptos de paralelo y serial, desplazamiento y TEMAS TRABAJO INDEPENDIENTE NO HABILITABLE: X EVALUACIÓN ACADÉMICA BIBLIOGRAFÍA (capítulos, páginas) Objetivos Metodología Bibliografía 1 2 INTRODUCCIÓN. LÓGICA SECUENCIAL SÍNCRONA REGISTROS Y CONTADORES Oficina Sede Hurtado Circuitos secuenciales, latches, flipflop,circuitos secuenciales temporizados, ecuaciones de estado, tabla de estados, diagrama de estados Registros de desplazamiento, registro de desplazamiento 5843356 Ext. 1027 [1], Cap. 5, pag 182 Recepción de ejercicios (<=5) www.unicesar.edu.co [1], Cap. 6, pag. 242 universal, contadores Presentación del software ISE 3 MEMORIAS 4 Diseño a nivel de transferencia de registros 5 Máquinas de estado finito (FSM) 6 Parcial Oficina Sede Hurtado Terminología de la memoria, operaciones generales de la memoria, conexiones entre CPU y la memoria Notación RTL, Máquinas de estado algorítmico (ASM), Multiplicador binario secuencial, Lógica de control, Diseño con multiplexores, Diseño libre de carreras, Diseño libre de latches Modelo Mealy y modelo Moore, Ejemplo rotación. Utiliza los registros de desplazamiento para resolver problemas lógicos Comprende las operaciones básicas en una memoria, Diferencia los tipos de ella, Conoce como interconectarla con otro dispositivo sea para ampliar la capacidad del sistema o para ampliar el bus Consultar tipos de memoria con los que cuenta la tarjeta Nexys 2 y sus características. Realizar ejercicios de uso de memoria Clase tipo exposición con participación de los estudiantes Realizar ejercicios de ASM Clase tipo exposición con participación de los estudiantes Analiza y abstrae un problema y lo expresa como ASM Recepción de ejercicios (<=5) Realizar ejercicios de FSM Clase tipo exposición con participación de los estudiantes Analiza y abstrae un problema y lo expresa como FSM Recepción de ejercicios de ASM (<=5) Propuesta de proyecto Evaluación escrita 5843356 Ext. 1027 Se responderán preguntas individuales y en grupo Recepción de ejercicios de FSM (<=5) www.unicesar.edu.co [2], Cap. 11, pag. 621 [1], Cap. 8, pag 334 [3], Cap. 5, pag. 107 Metodología de diseño en VHDL 7 Introducción al lenguaje VHDL Elementos sintácticos de VHDL 8 Oficina Sede Hurtado Conceptos de herramientas CADEDA, Diseño Bottom-Up, Diseño Top-Down, Ventajas del diseño TopDown, Ingeniería concurrente El lenguaje VHDL, VHDL describe estructura y comportamiento, Ejemplo básico de descripción VHDL, Presentación del proyecto final Operadores y expresiones, Tipos de datos, Tipos escalares, Tipos compuestos, Subtipos de datos, Atributos, Declaración de constantes, variables y señales, Declaración de entidad y arquitectura, Desarrollo de ejercicios en [4], Cap 1, pag. 1 Ejercicios básicos con la tarjeta Nexys 2 Clase tipo exposición con participación de los estudiantes Planea, Diseña y programa en VHDL para resolver un problema [5], Cap. 3 pag 21 Elaborar el primer avance del proyecto Clase tipo exposición con participación de los estudiantes 5843356 Ext. 1027 Organiza, planea su proyecto Recepción de programas en VHDL (<=5) www.unicesar.edu.co [5], Cap 4, pag 27 programación VHDL Ejecución concurrente Descripción serie comportamental abstracta 9 Subprogramas, paquetes y bibliotecas 10 VHDL para simulación Oficina Sede Hurtado Ejecución concurrente y ejecución serie, descripción comportamental RTL, Estructuras de la ejecución serie Diferencias entre variable y señal, estructuras de la ejecución serie Subprogramas, Declaración de procedimientos y funciones, Llamadas a subprogramas, Sobrecarga de operadores, Bibliotecas, paquetes y unidades, Paquetes: PACKAGE y PACKAGE BODY, Configuración: CONFIGURATION, Desarrollo de ejercicios en programación VHDL Los retrasos y la simulación, Retrasos inerciales y transportados, Descripción de un [5], Cap 5, pag 39 [6] Cap 9 pag 232 [5], Cap 45, pag 45 [6], Cap 3, pag 42 Realiza avances del proyecto Clase tipo exposición con participación de los estudiantes Respeta los tiempos de entrega, crea y resuelve situaciones presentadas durante la elaboración del proyecto Entrega del primer avance del proyecto Revisión y discusión de los avances del proyecto 5843356 Ext. 1027 [5], Cap 7, pag 57 [5], Cap 8, pag 67 www.unicesar.edu.co banco de pruebas, Notificación de sucesos, Procesos pasivos, Desarrollo de ejercicios en programación VHDL 11 Entrega avance del proyecto 12 VHDL para síntesis 13 Buses y resolución de señales 14 Utilización del lenguaje VHDL 15 Oficina Sede Hurtado Revisión y discusión de los avances del proyecto Restricciones en la descripción, Construcciones básicas, Descripción de lógica combinacional, Descripción de lógica secuencial, Desarrollo de ejercicios en programación VHDL Buses y resolución de señales, descripción de máquinas de estado Errores mas comunes usando VHDL, ejemplos para simulación y síntesis Continúa con la elaboración de su proyecto Revisión y discusión de los avances del proyecto Continúa con la elaboración de su proyecto Revisión y discusión de los avances del proyecto Continúa con la elaboración de su proyecto Revisión y discusión de los avances del proyecto [5], Cap 9, pag 75 Revisión completa del proyecto Exposición del proyecto final 5843356 Ext. 1027 www.unicesar.edu.co 16 Bibliografía [1] M. Morris Mano y M. D. Ciletti, Digital Design, Fourth ed., Pearson, Prentice Hall. [2] R. J. Tocci y N. S. Widmer, Sistemas Digitales Principios y aplicaciones, Sexta ed., Pearson Educacioón, 1996. [3] P. P. Chu, FPGA Prototyping by examples. Xilinx spartan-3 version, Hoboken, New Jersey: Wiley-Interscience, 2008. [4] P. J. Ashenden y J. Lewis, The designer's guide to vhdl, Third ed., Morgan Kaufmann Publisher, 2008. [5] D. L. Perry, Vhd: programming by example, Fourth ed., McGraw-Hill, 2002. [6] F. Pardo Carpio, «VHDL Lenguaje para descripción y modelado de circuitos,» Universidad de Valencia, 1997. OBSERVACIONES ______________________________________________________________________________________________________________________________________ ______________________________________________________________________________________________________________________________________ ______________________________________________________________________________________________________________________________________ ________________________________ FIRMA DEL DOCENTE Oficina Sede Hurtado _______________________________________ FIRMA DIRECTOR DE DEPARTAMENTO 5843356 Ext. 1027 www.unicesar.edu.co