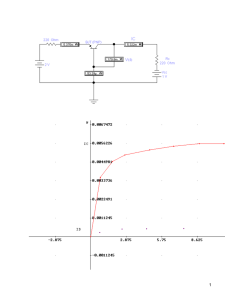

UNIVERSIDAD NACIONAL DE INGENIERÍA FACULTAD DE INGENIERÍA ELÉCTRICA Y ELECTRÓNICA ESCUELA PROFESIONAL DE INGENIERÍA ELECTRÓNICA ------------------------------------------------------------------------------------------ CURSO: LABORATORIO DE SISTEMAS MICROELECTRÓNICOS INTEGRADOS LABORATORIO Nº 1 (CICLO 2022-1) “LAYOUT DE TRANSISTORES MOS” INFORME: Preparar el informe en WORD y en PDF sin comprimir, adjuntar los archivos *.MSK y *.CIR de los diseños. Enviar por e-mail a los correos (ralarcon@uni.edu.pe, ramatutti@gmail.com). Poner en el asunto: Laboratorio N°…… SISTEMAS MICROELECTRONICOS En el programa microwind y de forma manual, hacer el “layout” (diseño físico) de los transistores, tal que las dimensiones estén en el intervalo: L= [2 micras hasta 4 micras], W= [4 micras hasta 8 micras]. Verifique que el microwind este en la tecnología de 0.25 micras. Para el transistor MOS tipo N y el transistor MOS tipo P. Responda en detalle lo siguiente: A) TRANSISTOR N-MOS 1) Revisar el modelo teórico de spice shichman hodges (nivel 1), identifique el tipo de transistor, los terminales del transistor n-mos (drain, source, gate, bulk) en su layout del transistor, muestre las ecuaciones del transistor en la zonas de corte, lineal, saturación. Interprete el layout realizado por Ud. 2) Muestre la pantalla de características estáticas, comportamiento dinámico, vista de corte, vista 3D, identifique y muestre en el layout con líneas punteadas los parámetros de dimensiones del layout L y W. Elegir la frecuencia adecuada para la simulación. 3) Muestre la descripción *.cir (spice) del layout, describa el significado de cada línea de la descripción, identifique y verifique las dimensiones L y W de transistor, muestre en el layout con líneas punteadas la ubicación de las capacidades parasitas y su valor. FIEE-UNI Página 1 de 2 EE-411 Escuela Profesional de Ingeniería Electrónica 4) Proponga un procedimiento, teórico y en simulación, para hallar la “resistencia de conducción” del transistor (revise y defina esta resistencia). - Considere el modelo de shichman hodges y asuma los parámetros típicos de acuerdo a su layout. Compare los valores de resistencia obtenidos e interprete la causa de la posible diferencia. B) TRANSISTOR P-MOS Igual que en la parte A, resuelva lo pedido en los puntos 1,2,3,4, en base al layout del transistor p-mos realizado por Ud. IMPORTANTE: DURACIÓN: 01 SEMANA. El informe es INDIVIDUAL, esta prohibido copiar. El informe debe ser ordenado y claro, incluir una CARÁTULA con los datos del alumno. El informe debe enviarse ANTICIPADAMENTE (el día anterior) para proceder a su revisión. La revisión se realiza al inicio de clases y es OBLIGATORIA la presencia del alumno. El alumno SUSTENTA en clases las preguntas que ha implementado. Mostrar en detalle el procedimiento de diseño y simulación. No se revisa en caso contrario. FIEE-UNI Página 2 de 2