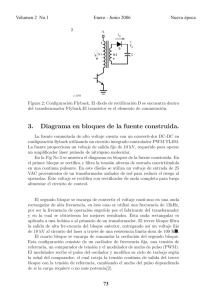

Electrónica: Teoría de Circuitos y Dispositivos Electrónicos

Anuncio