TP4 - Cartelera

Anuncio

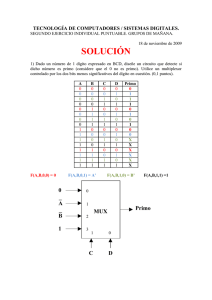

ARQUITECTURA I – 2010 Trabajo Práctico Nº 4 Lógica digital Operaciones lógicas y circuitos combinacionales 1. Realizar las siguientes operaciones lógicas: a. 10101100 AND 11000101 b. 10101100 OR 11000101 c. 10101100 XOR 11000101 d. NOT 10101100 e. 10101011 NAND 11000101 f. 10101011 NOR 11000101 g. 10101011 NXOR 11000101 2. Dado un byte X = x7x6x5x4x3x2x1x0 (indeterminado), ¿qué resultado se obtiene al aplicar las siguientes operaciones? (En el resultado, denote con !! al inverso del bit xn). a. X OR 10101010 b. X OR 11111000 c. X AND 10000000 d. X AND 10001111 e. X XOR 10101010 f. X XOR 00001111 3. Dado un byte X = x7x6x5x4x3x2x1x0 (indeterminado), ¿qué operación y qué máscara debería utilizar para lograr cada uno de los siguientes resultados? a. Poner en 1 los bits 0, 2 y 6 b. Poner en 0 los bits 4 y 7 c. Invertir (cambiar 0 por 1 y viceversa) los bits 1, 3 y 4 d. Cambiar los bits de X de modo que el bit 3 quede en 1, el bit 6 en 0, y el bit 2 invierta su valor original. En todos los casos, los bits no nombrados deben mantener su valor original. Considere cada inciso independientemente (no son operaciones secuenciales, siempre parte del mismo byte original). 4. Construya la tabla de verdad de las siguiente funciones lógicas representadas en forma de circuitos: a) b) c) UNNOBA – Arquitectura I – Trabajo Práctico 4 1 Diseño de circuitos combinacionales 5. Dada las siguientes funciones lógicas, definidas mediante su tabla de verdad, halle las siguientes expresiones: a. SOP (suma de productos) b. POS (producto de sumas) ABC F1 ABCD F2 000 001 010 011 100 101 110 111 1 0 1 0 1 0 1 1 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 1 0 1 0 0 0 0 0 1 1 1 1 0 1 1 1 6. Partiendo del siguiente mapa de Karnaugh, obtener las expresiones: a. suma de minitérminos (SOP canónica) b. producto de maxitérminos (POS canónica) c. SOP mínima d. POS mínima BC 00 A 0 1 1 1 01 11 10 1 1 1 7. Dadas las siguientes funciones booleanas, minimícelas utilizando mapas de Karnaugh: a. !! = !! + ! ! + !! b. !! = ! + ! ! + ! (! + !) c. !! = !" + !" + ! ! ! d. !! = ! ! + ! ! + ! + ! 8. Halle la expresión SOP mínima para las funciones F1 y F2 del ejercicio 7. 9. La función mayoría de 3 bits F(A, B, C) se define como: F = 1 si hay más 1s que 0s en las entradas y F = 0 en caso contrario. Implemente la función mayoría utilizando: a. un multiplexor de 8 entradas de datos. b. un multiplexor de 4 entradas de datos. (Sugerencia: analice de qué valores depende la salida F agrupándolos de a dos). c. una PLA. d. SOP mínima (utilice un mapa de Karnaugh). 10. Un sumador completo es un circuito que tiene tres entradas A y B (los bits a sumar) y Cin (el carry de la suma anterior), y tiene dos salidas S (la suma de A y B) y Cout (el carry producido en la suma). a. Escriba la tabla de verdad del sumador completo. b. Implemente el circuito utilizando una matriz lógica programable (PLA). UNNOBA – Arquitectura I – Trabajo Práctico 4 2