Memoria - Erika Vilches

Anuncio

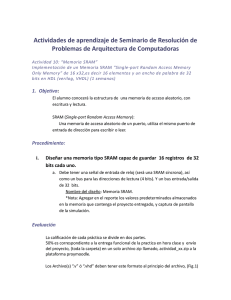

Memoria M. en C. Erika Vilches Parte 4 Arreglo de Memoria Semiconductora Básico • Celda → Elemento de almacenamiento en una memoria que puede retener ya sea un 1 o un 0 • Las memorias se componen de arreglos de celdas. • Ejemplo: 64 celdas → • Se puede organizar de distintas maneras basándose en las unidades de datos. • Figura a) memoria de 8 bytes. Figura b) memoria de 16 nibbles. Figura c) memoria de 64 bits. • Una memoria se identifica por → número de palabras que puede almacenar x el tamaño de la palabra. • En las PC, la RAM se organiza en bytes. Direcciones de Memoria y Capacidad • Dirección → Ubicación de una unidad de datos en un arreglo de memoria. • Capacidad → número total de unidades de datos que se pueden almacenar. • Data bus → Conjunto de líneas que se utiliza para hacer operaciones de lectura/escritura en la memoria. • Para el caso de memorias organizadas en bytes, el data bus tiene por lo menos 8 lineas de manera que los 8 bits de una dirección se transfieran en paralelo. • Address bus → Conjunto de líneas que nos permite poner un código binario que representa una dirección para realizar una lectura/escritura. • El número de líneas del address bus depende de la capacidad de la memoria. • Ejemplo: Un código de direcciones de 32 bits puede seleccionar 4,294,967,296 direcciones (2^32), expresado como 4G. Operación de Escritura Operación de Lectura Participaciones • ¿Cuál es la unidad de memoria mas pequeña que se puede almacenar en una memoria? • ¿Cuál es la capacidad en bits de una memoria que puede almacenar 256 bytes de datos? • • • ¿Qué es una operación de escritura? • Describa la diferencia entre una RAM y una ROM. ¿Qué es una operación de lectura? ¿Cómo de localiza en memoria una unidad de datos determinada? RAM La familia RAM • • • Dos categorías de RAM son: • • RAM estática → SRAM RAM dinámica → DRAM La SRAM utiliza latches como elementos de almacenamiento y por lo tanto puede almacenar datos indefinidamente mientras se aplique una alimentación continua. La DRAM utiliza capacitores como elementos de almacenamiento y no puede retener información por mucho tiempo si los capacitores no se recargan mediante un proceso que se conoce como refreshing. • Tanto la DRAM como la SRAM pierden la información almacenada cuando la alimentación se elimina y por lo tanto son memorias volátiles. • • Velocidad de lectura → SRAMs > DRAMs • Tipos básicos de SRAM • DRAMs pueden almacenar mucha mas información que las SRAMs en un tamaño físico determinado y costo (la celda DRAM es mucho mas simple y se pueden meter mas celdas en un area de chip dada). • • SRAM asíncrona → ASRAM SRAM de ráfaga síncrona → SB SRAM Tipos básicos de DRAM • • • • DRAM de modo página rápido → FPM DRAM DRAM con salida de datos extendida → EDO DRAM EDO DRAM en ráfaga → BEDO DRAM DRAM síncrona → SDRAM RAMs Estáticas (SRAMs) • Celda de memoria → Todas las SRAMs se caracterizan por celdas de memoria de latch. • Mientras tenga alimentación continua puede retener indefinidamente un estado de 1 o 0. Se quita la alimentación, se pierde el bit almacenado. Celda de memoria SRAM de latch → • Las celdas de memoria en una SRAM se organizan en renglones y columnas. • Todas las celdas de un renglón comparten la misma linea de row select. • Cada grupo de lineas data in y data out va a cada celda en una columna dada y están conectadas a una sola linea de datos que sirve como input y como output. • Escribir una unidad de datos → (nibble en este caso) en un renglón de celdas, la linea de row select se lleva a estado activo y se ponen 4 bits de datos en las lineas de I/O, después la línea de escritura se lleva al estado activo lo que causa que se almacene cada bit en una celda. Arreglo SRAM básico de n x 4 • Para leer una unidad de datos, la linea de lectura se lleva a su estado activo lo que causa que los 4 bits de datos almacenados en la fila seleccionada aparezcan en las lineas de I/O. Organización Básica de la SRAM Asíncrona ASRAM • SRAM Asíncrona → su operación no esta sincronizada con el reloj del sistema. Diagrama lógico para una SRAM Asíncrona de 32k x 8 → • En modo lectura, los 8 bits de datos que estan almacenados en la dirección seleccionada, aparecen en las lineas de salida de datos. • En modo escritura, los 8 bits de datos que se aplican a las lineas de entrada de datos, se almacenan en la dirección seleccionada. • Las lineas de entrada y salida de datos comparten la misma línea, durante la lectura actúan como lineas de salida (O0 a O7) y durante la escritura actúan como lineas de entrada (I0 a I7) SRAM de ráfaga síncrona SB SRAM • La SRAM síncrona se sincroniza con el reloj del sistema. • En una computadora, la SRAM síncrona opera con la misma señal de reloj que opera el microprocesador, con lo que se consigue una operación mas rápida. • Caché → Una de las mayores aplicaciones de las SRAMs