Memorias RAM Posición 0 1 2 2n-2 2n

Anuncio

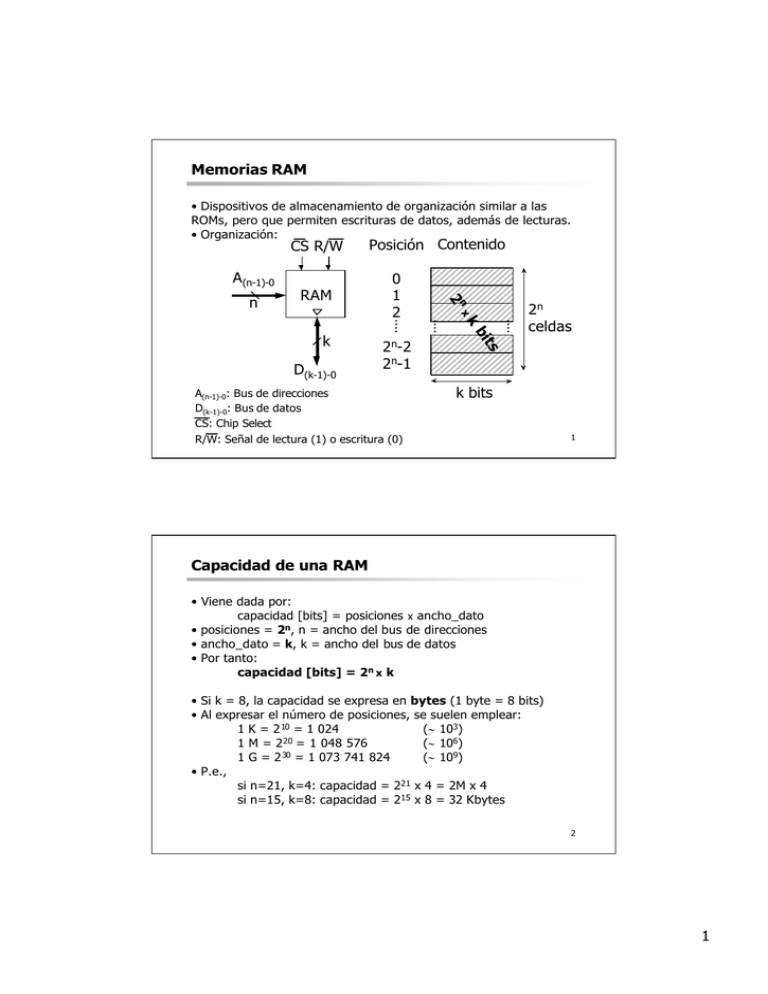

Memorias RAM • Dispositivos de almacenamiento de organización similar a las ROMs, pero que permiten escrituras de datos, además de lecturas. • Organización: CS R/W A(n-1)-0 bi 2n celdas ts A(n-1)-0: Bus de direcciones D(k-1)-0: Bus de datos CS: Chip Select R/W: Señal de lectura (1) o escritura (0) k D(k-1)-0 2n-2 2n-1 n x k 0 1 2 2 n RAM Posición Contenido k bits 1 Capacidad de una RAM • Viene dada por: capacidad [bits] = posiciones x ancho_dato • posiciones = 2n, n = ancho del bus de direcciones • ancho_dato = k, k = ancho del bus de datos • Por tanto: capacidad [bits] = 2n x k • Si k = 8, la capacidad se expresa en bytes (1 byte = 8 bits) • Al expresar el número de posiciones, se suelen emplear: 1 K = 2 10 = 1 024 (∼ 103) 20 1 M = 2 = 1 048 576 (∼ 106) 30 1 G = 2 = 1 073 741 824 (∼ 109) • P.e., si n=21, k=4: capacidad = 221 x 4 = 2M x 4 si n=15, k=8: capacidad = 215 x 8 = 32 Kbytes 2 1 Estructura interna: ejemplo 32K x 8 Celda A14 DEC Filas A7 D7 CS CS OE Write Enable (Escritura) OE Output Enable (Lectura) Matriz 256x128x8 bits D0 E/S Columnas & DEC Columnas A6 WE Chip Select WE A0 & 3 Lecturas y escrituras en una RAM • Ciclo de lectura: Dirección Dirección válida CS OE Datos (salida) Dato válido • Ciclo de escritura: Dirección Dirección válida CS WE Datos (entrada) Dato válido Captura 4 2 SRAM y DRAM • SRAM (RAM Estática): sus celdas están implementadas con biestables. – Al quitar la alimentación, se pierde el contenido. – Son rápidas. – Su capacidad de integración no es muy elevada, por lo que no se consiguen grandes capacidades. – Uso típico: sistemas empotrados, caché en procesador. • DRAM (RAM Dinámica): sus celdas están implementadas con condensadores, que almacenan 1 bit durante un cierto tiempo. – Necesitan ser refrescadas periódicamente. – Al quitar la alimentación, se pierde el contenido. – No son tan rápidas como las SRAM. – Su capacidad de integración es muy elevada, se consiguen memorias de altas capacidades. – Uso típico: memoria principal en PCs. 5 RAMs especiales: FIFO y LIFO • FIFO (First In First Out): actúa como una cola B k k R k W B R A k R A k W Control Control n W Control W k Control A R B k k A • Capacidad = profundidad_cola x ancho_dato = n x k 6 3 RAMs especiales: FIFO y LIFO (2) • LIFO (Last In First Out): actúa como una pila B k k Control R k W B R A k k W Control W n k k W Control k B Control A R A R A • Capacidad = profundidad_pila x ancho_dato = n x k 7 4