mapeo de memoria

Anuncio

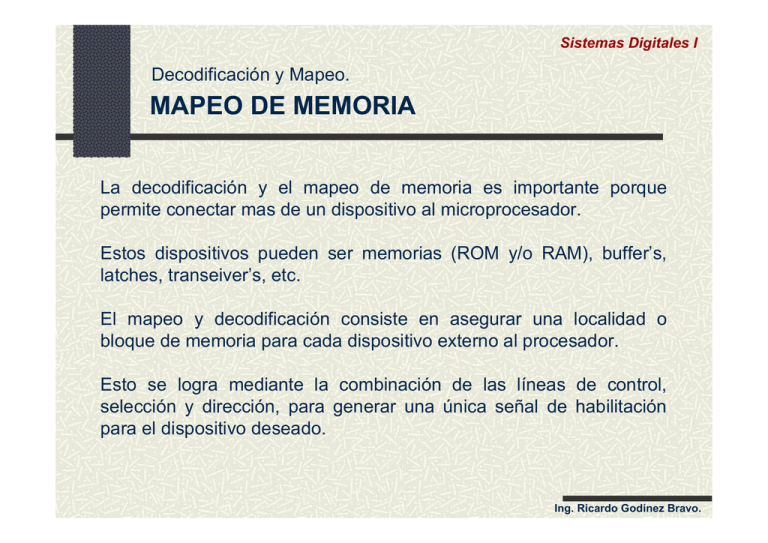

Sistemas Digitales I Decodificación y Mapeo. MAPEO DE MEMORIA La decodificación y el mapeo de memoria es importante porque permite conectar mas de un dispositivo al microprocesador. Estos dispositivos pueden ser memorias (ROM y/o RAM), buffer’s, latches, transeiver’s, etc. El mapeo y decodificación consiste en asegurar una localidad o bloque de memoria para cada dispositivo externo al procesador. Esto se logra mediante la combinación de las líneas de control, selección y dirección, para generar una única señal de habilitación para el dispositivo deseado. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Decodificación y Mapeo. MAPEO DE MEMORIA Puesto que la mayoría de los dispositivos usan lógica negativa para habilitarlos, una técnica básica de decodificación es usando compuertas NAND. La combinación de entradas a estas compuertas generan una salida en bajo (0 lógico) siempre que todas sus entradas estén en alto (1 lógico). Esta señal en bajo habilita un dispositivo en la dirección formada por la combinación de las señales de entrada. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Decodificación y Mapeo. MAPEO DE MEMORIA Supongamos un conjunto de 16 líneas de dirección cuyas 8 líneas más significativas son usadas para decodificar y mapear un dispositivo como sigue: De acuerdo al diarama anterior se tiene un bloque de 6A00H – 6AFFH: A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 0110 1010 XXXX XXXX 0110 1010 0000 0000 0110 1010 1111 1111 Ing. Ricardo Godínez Bravo. Sistemas Digitales I Decodificación y Mapeo. DECODIFICACIÓN DE MEMORIA C.I. 74LS138 (Decodificador 3 x 8) Este dispositivo selecciona una de entre ocho salidas posibles (Y0 hasta Y7) en nivel bajo de acuerdo a la combinación de tres señales de selección (A, B y C). Este dispositivo puede habilitar 8 dispositivos externos (memorias) en bloques cuyo tamaño dependen de las lineas de direcciones más significatvas que sean conectadas a las líneas se selección. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Decodificación y Mapeo. DECODIFICACIÓN DE MEMORIA C.I. 74LS138 (Decodificador 3 x 8) Las entradas de selección del decodificador pueden ampliar o reducir el tamaño de los bloques mapeados. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Decodificación y Mapeo. DECODIFICACIÓN DE MEMORIA C.I. 74LS138 (Decodificador 3 x 8) Las entradas de selección del decodificador pueden ampliar o reducir el tamaño de los bloques mapeados. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Decodificación y Mapeo. DECODIFICACIÓN DE MEMORIA C.I. 74LS138 (Decodificador 3 x 8) Supongamos un procesador 8086 con 20 líneas de direcciones (A0 – A19) conectadas a un decodificador 74LS138 como se muestra: salida Ini bloque Fin bloque Y0 F0000H F1FFFH Y1 F2000H F3FFFH Y2 F4000H F5FFFH Y3 F6000H F7FFFH Y4 F8000H F9FFFH Y5 FA000H FBFFFH Y6 FC000H FDFFFH Y7 FE000H FFFFFH Ing. Ricardo Godínez Bravo. Sistemas Digitales I Decodificación y Mapeo. INTERFACE DE MEMORIA CON EL µP8086 Las señales en el procesador 8086 para poder interfazar memoria son: Bus de datos de 16 bits (H y L), M/IO’, BHE’, A0, RD’ y WR’. Las señales BHE’ y A0 se usan para seleccionas uno o ambos bancos de memoria. BHE’ A0 Función 0 0 Ambos bancos activos de 16 bits de datos (D15 – D0) 0 1 Banco alto activo de 8 bits de datos (D15 – D8) 1 0 Banco bajo activo de 8 bits de datos (D7 – D0) 1 1 Ambos bancos deshabilitados Ing. Ricardo Godínez Bravo. Sistemas Digitales I Decodificación y Mapeo. INTERFACE DE MEMORIA CON EL µP8086 Dado que la memoria del 8086 esta dividida en dos bancos fisicamente, la manera de seleccionar algún banco es generar una señal estroboscópica para escritura separada para cada banco. No se generan señales de lectura para cada banco ya que el 8086 sólo lee el banco que necesita (alto ó bajo). Si se presentan 16 bits en el bus de datos al realizar una lectura, el procesador sólo toma la información que necesita. Para generar señales estroboscópicas de escritura se usan compuertas OR para combinar A0 con WR’ para seleccionar el banco bajo y BHE’ y WR’ para banco alto. Ing. Ricardo Godínez Bravo.