Amplificador Operacional de Transconductancia Completamente

Anuncio

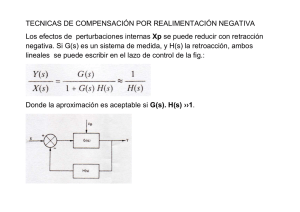

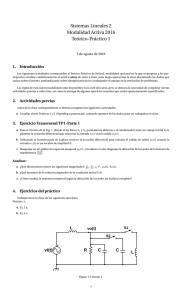

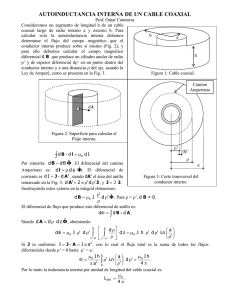

Amplificador Operacional de Transconductancia Completamente Diferencial con 1.2 V de Alimentación y Amplio Rango de Operación J. M. Carrillo, G. Torelli, M. A. Domínguez, R. Pérez-Aloe, J. M. Valverde y J. F. Duque-Carrillo Resumen—Se presenta en esta contribución el diseño de un amplificador operacional de transconductancia (OTA) completamente diferencial adecuado para la operación con bajo voltaje de alimentación. La etapa de entrada del amplificador utiliza transistores MOS conducidos mediante el substrato, cuya transconductancia efectiva se incrementa mediante un lazo de realimentación parcialmente positivo. La componente de DC del voltaje diferencial de salida es controlada mediante una red de realimentación del modo común apropiada para la operación con bajo voltaje. El elemento de transconductancia resultante se ha incluido en la implementación de un filtro paso-baja completamente diferencial de segundo orden OTA-C capaz de operar con 1.2 V de alimentación. Se proporcionan resultados simulados, obtenidos en tecnología CMOS estándar de 0.35-m. Palabras Clave—Amplificador operacional de transconductancia, bajo voltaje, filtro continuo en el tiempo OTA-C, transistor MOS conducido mediante el substrato I. INTRODUCCIÓN E L diseño actual de circuitos integrados se caracteriza por la continua bajada del voltaje de alimentación. Este hecho origina la necesidad de que los circuitos analógicos presenten un amplio rango de operación, de modo que se obtenga una relación señal-ruido aceptable [1]–[3]. Este requisito hace que las etapas de entrada convencionales, basadas en un par diferencial, no sean adecuadas para la operación con bajo voltaje, debido a la limitación de los pares de canal n y p a operar cerca de la alimentación negativa y positiva, respectivamente. La solución tradicional para obtener una etapa de entrada con amplio rango de voltaje de modo común de entrada consiste en conectar en paralelo un par diferencial de canal n y uno de canal p [1]. El principio de operación se basa en tener al menos uno de los pares activo para cualquier nivel de la señal de entrada desde la alimentación negativa (VSS o masa) hasta la positiva (VDD). Sin embargo, esta aproximación no es apropiada para la operación con voltajes de alimentación extremadamente bajos, VDD ~ VGS + VDSat (con el significado habitual de los símbolos), ya que existe una región en el medio del rango de voltaje de entrada donde ninguno de los pares de entrada puede ser encendido. Por otro lado, el uso de una etapa compuesta presenta inconvenientes tales como el aumento de la complejidad del circuito, con el consecuente aumento del consumo de potencia y de área de silicio, y su reducida linealidad, debido a la inherente distorsión de cruce [4]. Una alternativa interesante para incrementar el rango de voltaje de entrada de modo común de un par diferencial consiste en aplicar la señal de entrada al terminal substrato de los transistores MOS de entrada y formar el canal de estos dispositivos mediante la aplicación en su puerta de un voltaje de polarización adecuado [5, 6]. En este caso, el voltaje de entrada de modo común se extiende, ya que ahora no es necesario destinar una parte del voltaje de entrada a encender los dispositivos de entrada. Una desventaja de esta solución para algunas aplicaciones consiste en que la transconductancia del substrato (gmb) es más pequeña que la transconductancia de la puerta (gm) en un factor que oscila entre 4 y 5 en tecnologías CMOS estándar. Sin embargo, este inconveniente puede ser solucionado aumentado la transconductancia efectiva de entrada con la ayuda de técnicas de diseño apropiadas [6]. El uso de transistores MOS conducidos mediante el substrato permite obtener un amplio rango de operación sin riesgo de latch-up, siempre que el valor de la corriente a través del terminal substrato se mantenga en un nivel bajo y el layout del circuito sea cuidadosamente trazado [5]. Además, la corriente de entrada que fluye a través de la unión pn fuente-substrato de los transistores de entrada se puede mantener en un nivel muy bajo, incluso cuando dicha unión es polarizada en directa, siempre que el voltaje en el terminal puerta sea ajustado convenientemente [7]. Se presenta un amplificador operacional de transconductancia (OTA) completamente diferencial con transistores MOS de entrada conducidos mediante el substrato con realce de la transconductancia efectiva [6]. El bloque resultante se ha utilizado en la implementación de un filtro de tiempo continuo OTA-C capaz de operar con un reducido voltaje de alimentación. II.OTA DE BAJO VOLTAJE COMPLETAMENTE DIFERENCIAL Trabajo financiado por la Dirección General de Universidades del Ministerio de Educación y Ciencia mediante la beca de movilidad PR2007-0509 y por la Junta de Extremadura y el FEDER a través del proyecto de investigación PRI09A080 y de las ayudas a grupos de investigación GR10128. J. M. Carrillo, M. A. Domínguez, R. Pérez-Aloe, J. M. Valverde y J. F. Duque-Carrillo: Dpto. Ing. Eléctrica, Electrónica y Automática, Universidad de Extremadura, 06006 Badajoz, España (teléfono: +34 924 289594; correoe: jmcarcal@unex.es). G. Torelli: Dipartimento di Elettronica, Università di Pavia, 27100 Pavia, Italia (correo-e: guido.torelli@unipv.it). La Fig. 1 ilustra el esquemático de un OTA completamente diferencial, cuya etapa de entrada incluye transistores MOS conducidos mediante el substrato. Los dispositivos MLP representados en color gris no se tienen en cuenta por el momento. Se ha elegido una implementación PMOS ya que se ha considerado una tecnología de pozo tipo n. Las señales de entrada (Vi, Vi) se aplican a los VDD VDD Vcm IB IBM Vi Vi A M10R MU MLNC MLN MLP IBMR Vo MI M1R MLNC MLN MLP IBR IBMR VAGND Vo1 Vcm MI IBR M10CR B Vo MD Vcm IBM MU M2R Vo2 M3R M7CR M4R M8CR A MD M9R B M7R M5R M8R M6R Figura 1. OTA completamente diferencial con etapa de entrada con transistores MOS conducidos mediante el substrato. Figura 2. Red de control del modo común para el OTA completamente diferencial de la Fig. 1. terminales substrato de los transistores MI, mientras que sus puertas son conectadas a masa para formar el canal. Los transistores MLN, conectados como diodo y polarizados mediante una corriente IBM, son utilizados junto con los dispositivos MD para reflejar la corriente que circula a través de los transistores de entrada hacia la rama de salida. En dichas condiciones, la transconductancia efectiva de la etapa de entrada es igual a la transconductancia del substrato de los transistores MI, gmb,MI. Los transistores MLP en la Fig. 1 se utilizan para implementar un lazo de realimentación parcialmente positivo [8]. Su efecto es disminuir la conductancia en los nudos A y B y proporcionar una transconductancia de entrada efectiva igual a parcialmente positivo, limitando éste la máxima frecuencia de operación del circuito. La posición de este polo secundario puede ser expresada como: g m ,eff g mb , MI 1 1 g mb ,MI g m , MLP 1 1 g m , MLN (1) donde gm,MI y gmb,MI son las transconductancias de la puerta y el substrato, respectivamente, de los transistores MI, gm,MLN y gm,MLP son las transconductancias de puerta de los transistores MLN y MLP y = gm,MLP/gm,MLN. Obviamente, gm,MLP debe ser menor que gm,MLN para impedir que el lazo de realimentación total se haga positivo. El término 1/(1– ) puede ser definido como el factor realce de transconductancia (RT), y puede ser ajustado al valor deseado, siempre mayor que la unidad. En particular, el factor RT depende de la relación gm,MLP/gm,MLN y, por tanto, se ajusta adecuadamente seleccionando la relación de aspecto W/L de los transistores MLN y MLP. Si se desea un factor RT igual a 5, cantidad que representa aproximadamente el valor de la relación gm/gmb en la tecnología considerada, gm,MLP debe ser ajustado igual a (4/5)∙gm,MLN. Cuando los transistores de la carga activa operan saturados en la región de inversión fuerte, esta condición es equivalente a hacer (W/L)MLP = 4/5∙(W/L)MLN: en efecto, el cociente entre las corrientes de polarización que circulan a través de MLP y MLN también es proporcional al cociente (W/L)MLP/(W/L)MLN. El valor de esta relación se puede alcanzar con gran precisión en tecnología CMOS. El realce de transconductancia ilustrado causa un aumento de la ganancia en DC y del GBW. Sin embargo, existe un polo secundario, asociado al nudo donde se decrece la conductancia con la ayuda del lazo de realimentación p a b g m , MLN g m , MLP C p ,a b donde Cp,a–b representa la capacidad parásita en los nudos A y B. La localización de este polo depende de las capacidades parásitas y, por tanto, su posición puede ser situada a alta frecuencia si los tamaños de los transistores conectados al mismo son minimizados. El tamaño mínimo de cada dispositivo está limitado por el máximo valor del voltaje drenador-fuente, VDSat, necesario para asegurar su operación en la región de saturación. III. CIRCUITO DE REALIMENTACIÓN DEL MODO COMÚN La componente de modo común del voltaje de salida (Vo, del OTA completamente diferencial de la Fig. 1 ha de ser ajustado a un nivel adecuado. Habitualmente se elige el voltaje intermedio entre VDD y VSS (o masa), ya que de este modo se consigue maximizar la amplitud de la señal de salida. La salida del OTA de la Fig. 1 es controlada mediante el circuito de realimentación del modo común ilustrado en la Fig. 2. La red se basa en un detector de modo común implementado mediante dos pares diferenciales conectados en paralelo [9]. Los pares en la red de realimentación del modo común incluyen transistores de entrada MOS conducidos mediante el substrato, con el propósito de no limitar la excursión de la señal de salida del OTA. La componente de modo común de la señal de salida es comparada con el nivel de modo común deseado a la salida, generalmente VAGND o masa analógica, y la corriente generada da lugar a una señal de voltaje, Vcm, que es utilizada en el amplificador completamente diferencial para cerrar un lazo de realimentación negativa. Los transistores M5R y M6R, en color gris, se incluyen para implementar un lazo de realimentación parcialmente positivo, el cual tiene dos objetivos principales. Por un lado, el valor de la ganancia de lazo de modo común (LGCM) y el producto ganancia-ancho de banda de modo común (LGBWCM) son incrementados, de modo que son comparables a los valores correspondientes a aquellos de la señal de modo diferencial (LGDM y LGBWDM). Por otro lado, e incluso más importante, Vo) VDD G m2 G m1 Vi M11 Vo IB Vcm IBM C2 C1 M12 IB IBM Vi2 Vi1 Vo1 M1 M2 Vi4 Vi3 M3 M8C M7C (a) Vi Vi1 Vi2 Vi3 Vi4 2C1 Vo2 Gm1 Vo1 M9 Vi1 Vi2 Vi3 Vi4 Vo2 Gm2 Vo1 2C1 2C2 (b) la presencia de estos dos dispositivos hace que las estructuras del amplificador completamente diferencial y de la red de detección del modo común sean muy similares. De este modo, la precisión del mecanismo de realimentación que gobierna el control del modo común de salida es incrementada, conduciendo a un valor para el modo común de salida muy similar al idealmente deseado. IV. FILTRO PASO-BAJA OTA-C DE SEGUNDO ORDEN El OTA presentado posee un amplio rango de entrada en modo común, gracias al uso de transistores MOS de entrada conducidos mediante el substrato. Por ello, este bloque es adecuado para ser utilizado en una estructura en la que los amplificadores estén conectados en configuración de realimentación no inversora. Para determinar las prestaciones del OTA propuesto se ha diseñado un filtro paso-baja OTA-C de segundo orden, basado en la estructura mostrada en la Fig. 3(a). El filtro está compuesto por dos transconductores (Gm1 y Gm2) y dos condensadores (C1 y C2), realizando la siguiente función de transferencia: G m1G m 2 C1C 2 G G G s 2 m 2 s m1 m 2 C2 C1C 2 (3) De (3), la ganancia en DC (K), la frecuencia de corte ( o), y el factor de calidad (Q) del filtro se deducen fácilmente como: K 1 o Gm1Gm 2 C1C 2 Q Gm1 G m 2 C 2 C1 M6 M8 M10 Vo Figura 3. Diagrama de bloques del filtro paso baja OTA-C de segundo orden: (a) salida única y (b) salida completamente diferencial. V ( s) H (s) o Vi ( s ) M7 M5 Figura 4. OTA completamente diferencial utilizado en la implemencación del filtro OTA-C. 2C2 Vo2 M4 (4a) (4b) (4c) El filtro OTA-C de la Fig. 3(a) utiliza un reducido número de componentes y, por tanto, la ganancia a baja frecuencia K es fija. Además, para Gm1 = Gm2 = Gm el circuito posee un factor de calidad también fijo, que viene dado por un cociente de condensadores, y una frecuencia de corte ajustable o, que se puede programar por medio de la corriente de polarización IB de los OTAs. A partir del diagrama conceptual de la Fig. 3(a) se puede determinar la versión completamente diferencial del filtro, ilustrada en la Fig. 3(b), la cual permite mejorar las prestaciones del sistema. Como se puede observar, se utilizan dos condensadores idénticos conectados a masa, en vez de usar un único condensador flotante conectado entre los terminales de salida de cada OTA. El objetivo de esta elección es estabilizar, simultáneamente, mediante dichos condensadores la respuesta en frecuencia del lazo de realimentación del modo común. Como se ilustra en la Fig. 3(b), los OTAs poseen cuatro terminales de entrada y dos terminales de salida, de modo que se pueda implementar la estructura con la realimentación no inversora requerida. La implementación de un OTA completamente diferencial con cuatro terminales de entrada y dos de salida se ilustra en la Fig. 4. Como se puede observar, este bloque básico está basado en un amplificador diferencial de diferencias de una etapa [10]. El uso de transistores conducidos mediante el substrato permite incrementar el rango de entrada de modo común, mientras que la transconductancia efectiva de entrada del OTA es realzada mediante el uso de la técnica basada en un lazo de realimentación parcialmente positivo, descrita en la Sección II. La componente de modo común del voltaje de salida del OTA completamente diferencial es controlada por el lazo de realimentación del modo común descrito en la Sección III e ilustrado en la Fig. 2. V. RESULTADOS SIMULADOS El filtro de la Fig. 3(b), incluyendo el OTA completamente diferencial de la Fig. 4 y el circuito de control de modo común de la Fig. 2, fue diseñado en tecnología CMOS estándar de 0.35-m, para operar con un voltaje de alimentación de 1.2 V. Las corrientes de polarización IB, IBM, IBR e IBMR, fueron ajustadas a 30 A, 6 A, 30 A y 6 A, respectivamente. El valor nominal del factor RT en la etapa de entrada de los OTAs fue ajustado a 4. Este realce fue obtenido ajustando los tamaños de los transistores MLN y MLP a 10/1.4 m/m y 7.5/1.4 m/m, respectivamente. Como resultado, el valor simulado de la transconductancia efectiva de los dos OTAs fue Gm1 = Gm2 = TABLA I. PRESTACIONES SIMULADAS DEL FILTRO PASO-BAJA OTA-C (TECNOLOGÍA: 0.35-m CMOS, VDD = 1.2 V) magnitude (dB) 0 Parámetro fo Q Ruido total referido a la entrada (1 Hz – 4 MHz) Vin para –40dB-THD @ fi = 1 kHz Rango dinámico (–40dB-THD) Consumo de potencia en DC -20 -40 -60 2 10 IB = 300 nA: fo = 60 kHz IB = 950 nA: fo = 185 kHz IB = 3 A: fo = 562 kHz IB = 9.5 A: fo = 1.65 MHz IB = 30 A: fo = 4 MHz 10 3 10 4 10 5 6 7 10 10 8 10 frequency (Hz) Figura 5. Programabilidad simulada de la frecuencia de corte (fo) del filtro paso-baja OTA-C de segundo orden para Q = 1/√2. -40 amplitud de la señal sinusoidal de entrada. En particular, se aplicaron señales de 1 kHz y 100 kHz a los terminales de entrada del filtro. Como se puede observar, se obtuvo una alta linealidad para valores grandes de la amplitud de la señal de entrada, gracias al amplio rango de operación del OTA diseñado. Finalmente, la Tabla I proporciona un resumen de las prestaciones simuladas del filtro paso-baja OTA-C completamente diferencial de segundo orden. -50 THD (dB) VI. CONCLUSIÓN -60 fin = 1 kHz fin = 100 kHz -70 0.0 Valor 4 MHz 1/√2 222.8 Vrms 1.8 Vpp 69.1 dB 657 W 0.5 1.0 1.5 2.0 Vin(Vpp) Figura 6. THD simulada del filtro OTA-C para una señal sinusoidal de entrada con frecuencias 1-kHz y 100-kHz frente a su amplitud (fo = 4 MHz). El uso de transistores MOS conducidos mediante el substrato constituye una solución eficiente para implementar una etapa de entrada con amplio rango de operación. Su transconductancia puede ser incrementada mediante el uso de un lazo de realimentación parcialmente positivo. El uso conjunto de estas dos técnicas ha permitido diseñar un amplificador diferencial de diferencias completamente diferencial. Dicho amplificador, capaz de operar con una alimentación de 1.2 V, constituye el principal bloque básico de un filtro paso baja OTA-C que ha sido realizado en tecnología CMOS estándar de 0.35-m. REFERENCIAS Gm = 295 A/V. Los valores de los condensadores elegidos fueron 2C1 = 40 pF y 2C2 = 20 pF. Esta elección proporcionó valores teóricos para fo y Q, de 3.32 MHz y 1/√2, respectivamente. Los valores simulados de LGDM y LGBWDM del OTA de la Fig. 4 fueron 44.2 dB y 4.38 MHz, respectivamente, con un margen de fase de 75.7º cuando se conectaron condensadores de carga de 20 pF a sus terminales de salida. Los valores simulados de LGCM y LGBWCM fueron 44.3 dB y 4.53 MHz con un margen de fase de 73.2º para el mismo valor de los condensadores de carga. La Fig. 5 muestra la respuesta en frecuencia simulada del filtro paso baja OTA-C completamente diferencial de segundo orden de la Fig. 3(b). El valor de fo para IB = 30 A fue 4 MHz. El desacuerdo respecto al valor teórico indicado anteriormente se debe al hecho de que el factor de calidad simulado es mayor que el teórico, causando un pequeño pico en la respuesta de la magnitud, en la región de frecuencia cercana a fo. La programabilidad de la frecuencia de corte del filtro se obtuvo barriendo el valor de Gm1 y Gm2, es decir, modificando el nivel de la corriente de polarización de los pares diferenciales, IB. Como Gm1 = Gm2, el factor de calidad Q, dado por (4c), depende solamente de un cociente de condensadores y es, por tanto, mantenido constante. La distorsión simulada de filtro OTA-C se ilustra en la Fig. 6, donde la THD es representada como función de la [1] J.H. Huijsing and D. Linebarger, “Low-voltage operational amplifier with rail-to-rail input and output ranges,” IEEE J. Solid-State Circuits, vol. 20, pp. 1144-1150, December 1985. [2] J.M. Carrillo, J.F. Duque-Carrillo, G. Torelli, and J.L. Ausín, “Constant-gm constant-slew-rate high-bandwidth low-voltage rail-torail CMOS input stage for VLSI cell libraries,” IEEE J. Solid-State Circuits, vol. 38, pp. 1364-1372, August 2003. [3] T. Song, J. Hu, X. Li, and S. Yan, “A constant-gm constant-slew-rate rail-to-rail input stage with static feedback and dynamic current steering for VLSI cell libraries,” IEEE Trans. Circuits Syst. II, vol. 54, pp. 76-80, January 2007. [4] T.A.F. Duisters and E.C. Dijkmans, “A –90-dB THD rail-to-rail input opamp using a new local charge pump in CMOS,” IEEE J. SolidState Circuits, vol. 33, pp. 947-955, July 1998. [5] B.J. Blalock, P.E. Allen, and G.A. Rincon-Mora, “Designing 1-V op amps using standard digital CMOS technology,” IEEE Trans. Circuits Syst. II, vol. 45, pp. 769-780, July 1998. [6] J.M. Carrillo, G. Torelli, R. Pérez-Aloe, and J.F. Duque-Carrillo, “1V rail-to-rail CMOS opamp with improved bulk-driven input stage,” IEEE J. Solid-State Circuits, vol. 42, pp. 508-517, March 2007. [7] J.M. Carrillo, G. Torelli, M.A. Domínguez, and J.F. Duque-Carrillo, “On the input common-mode voltage range of CMOS bulk-driven input stages,” Int. J. Circuit Theory and Applications (in press), 2011. [8] D.J. Allstot, “A precision variable-supply CMOS comparator,” IEEE J. Solid-State Circuits, vol. SC-17, pp. 1080-1087, December 1982. [9] J.F. Duque-Carrillo, “Control of the common-mode component in CMOS continuous-time fully differential signal processing,” Analog Integr. Circ. Sig. Proc., vol. 4, pp. 131-140, September 1993. [10] J.F. Duque-Carrillo, G. Torelli, R. Pérez-Aloe, J.M. Valverde, and F. Maloberti, “Fully differential basic building blocks based on fully differential difference amplifiers with unity-gain difference feedback,” IEEE T. Circuits and Systems I, vol. 42, pp. 190-192, March 1995.