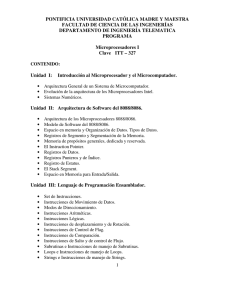

ESTRUCTURA DE MICROPROCESADORES

Anuncio

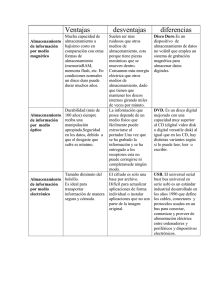

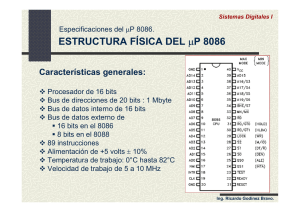

ESTRUCTURA DE MICROPROCESADORES Interfaz de memoria con 8086/8088 Profesor Ing. Johan Carvajal Godínez JCG-2010 Agenda de la Clase 1. Proceso de acceso a memoria 2. Demultiplexión de buses 3. Diseño de decodificadores de selección de chips y de señales de control 4. Tipos de memoria utilizados para sistemas basados en microprocesador 5. Esquema de acceso en 8/16 bits 6. Casos de estudio 2 JCG-2009 Proceso de acceso a memoria (1) •Los pines son TTL compatibles •Pin 33 en alto para seleccionar modo mínimo •Durante el primer periodo de reloj de los ciclos de lectura/escritura pines 3835 funcionan como líneas de dirección •S4/S3 indican cual segmento de memoria debe accederse •00=ES •01=SS •10=CS •11=DS JCG-2009 Proceso de acceso a memoria (2) •Pin 36, Pin 35 se utilizan para •A18 y A19 en el primer periodo del ciclo de memoria •00 en primer ciclo si se trata de acceder un I/0 •Durante los otros ciclos de acceso a memoria •S5 interrupt enable flag •S6bus use flag •AD0/AD15 se ponen en alta impedancia durante un interrupt ack o hold ack •Pin 34 en primer ciclo de una instrucción habilita demultiplexación del bus de datos y direcciones JCG-2009 Valores de inicialización del 8086/8088 • DS, SS, ES, IP, Flags =0000H • CS=FFFFH • La cola de instrucciones de BIU se limpia • En una computadora CS:IP ejecuta un salto a programa en BIOS JCG-2009 Modo míínimo Todas las señales de memoria y I/O se generan el el uPC JCG-2009 Configuración de memoria [modo mínimo] JCG-2009 Ciclo de escritura simplificado JCG-2009 Ciclo de lectura simplificado JCG-2009 Descripción del ciclo • T1: se pone la dirección en bus de direcciones • T2: se quita la dirección y se parapara para leer o escribir • T3: Se escribe o lee bus de datos • T4: se pone la señalización de finalización del ciclo de acceso JCG-2009 Demultiplexación de los buses • Se deben separar las señales multiplexadas a lo interno del microprocesador para crear: –Bus de datos • D0-D15 –Bus de direcciones • A0-A19 –Bus de control • IOR, IOWR • MEMR MEMW JCG-2009 Diseño de ¨decos¨ decos¨ de selección de memoria • Se considera la ubicación de segmento – Se debe calcular el rango de variación lógico – Se debe considerar el número de chips requerido para implementar el bloque de memoria – Se genera una lógica de selección de chip según el bloque que se quiera escribir/leer – A partir de este DECO se generan los estrobos de CS! JCG-2009 Señales de control de escritura lectura • Se deben separar la señales de escritura/lectura de memoria y I/O – Canales independientes – Otros dispositivos pueden tomar control de dichas señales – Entradas: • M/IO! • RD! • WR! – Salidas: • IOR!, IOW! • MEMR!, MEMW! JCG-2009 Mapeo de memoria JCG-2009 EJEMPLO JCG-2009 Señales de control con memoria JCG-2009 Organización de la memoria 8086 (16 bits) 8088 (8 bits) JCG-2009 8088 8088 byte transfer 8088 word transfer JCG-2009 8086 Transferencia del byte impar Transferencia del byte par Transferencia de una palabra JCG-2009 Address Bus Latches and Buffers JCG-2009 Circuito de enclavamiento de dirección JCG-2009 Tipos de memoria utilizados JCG-2009 ROM JCG-2009 PROM JCG-2009 Para tomar en cuenta JCG-2009 SRAM JCG-2009 DRAM JCG-2009 Caso de estudio JCG-2009 Bibliografía Brey, B. Los microprocesadores intel: Arquitectura, programación e interfaces. Tercera Edición. Prentice Hall. 1995 “Intel 8086 microprocessor family” www.cpu-world.com/CPUs/8086/ JCG-2009