Lab 01 - Tecnologias Logicas 2K9 - Universidad Nacional de San Luis

Anuncio

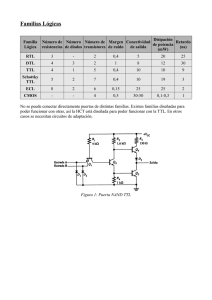

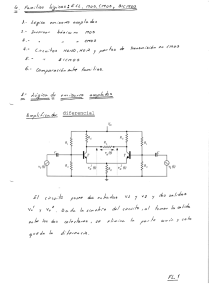

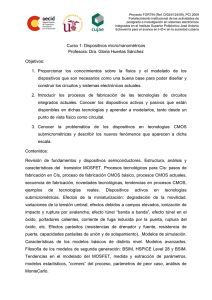

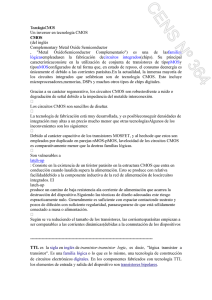

Universidad Nacional de San Luis Facultad de Ciencias Físico Matemáticas y Naturales Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica LABORATORIO DE INTERFACES PRÁCTICO Nº 1 Tecnologías Lógicas e Interfaces Índice: 1. 2. 3. 4. 5. 6. 7. Objetivos. Material de Referencia Listado de Materiales. Listado de Instrumental. Desarrollo de la Práctica. Diseño de una interface de potencia. Anexo I - Componentes utilizados. Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica TRABAJO PRÁCTICO Nº 1 Tecnologías Lógicas e Interfaces 1. Objetivos § § § Estudiar las características eléctricas de las distintas familias lógicas. Realizar circuitos de interfaz entre familias lógicas. Excitar cargas de potencia desde dispositivos lógicos. 2. Material de Referencia § § Apuntes de la Cátedra. Hojas de datos de los componentes usados. 3. Listado de Materiales 1 CI 74LS07 1 ULN2803 1 R 470 5% 1 R 3K3 5% 1 CI 74LS00 1 BC 337 1 R 22K 5% 2 R 4K7 5% 1 CI 7400 1 4N35 1 R 47K 5% 1 R 330 5% 1 CI CD4011 1 Diodo 1N4148 1 R 5K6 5% 1 LED Rojo 1 CI CD4049 1 Rele 12V 2 R 220 5% 4. Listado de Instrumental 1 Multimetro digital 1 Fuente de alimentación variable 1 Entrenador Microcontroladores LAB - MC 5. Desarrollo de la Práctica 5.1 Introducción El término “Interface” se usa en electrónica digital para hacer referencia a la interconexión eficiente de dos dispositivos, circuitos o sistemas que no son compatibles, es decir, que poseen características eléctricas diferentes. Las interfaces que realizaremos en este laboratorio nos permitirán que dispositivos de diferentes familias puedan comunicarse entre si y con dispositivos del mundo real. Laboratorio N° 1 Prof. Roberto Martín Murdocca Pág. 2 de 18 Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica Familias Lógicas de Circuitos Integrados Una “familia lógica” es un grupo de dispositivos lógicos integrados (compuertas, decodificadores, contadores, multiplexores, etc.) que comparten una tecnología de fabricación común, son eléctricamente compatibles entre sí, es decir, tienen estandarizadas sus características de entrada y salida. Por ello, la conexión entre dispositivos lógicos de una misma familia es directa no siendo necesario etapas de acoplamiento o adaptación. Características de las familias lógicas Las prestaciones que ofrece una familia lógica están dadas por la velocidad, el consumo de potencia, tensión de alimentación, niveles de tensión y corriente en la entrada y en la salida, inmunidad al ruido, etc. Veremos los términos usados para caracterizar familias lógicas. Características de entrada y salida Son los valores de tensiones y corrientes que adoptan a la salida o que necesitan a la entrada los dispositivos lógicos para los niveles bajo (‘0’ lógico) y alto (‘1’ lógico). Tensiones de entrada y salida VILmáx Tensión de entrada en nivel bajo máxima. VILmin. Tensión de entrada en nivel bajo mínima. VIHmáx Tensión de entrada en nivel alto máxima. VIHmin. Tensión de entrada en nivel alto mínima. VOLmáx Tensión de salida en nivel bajo máxima. VOLmin. Tensión de salida en nivel bajo mínima. VOHmáx Tensión de salida en nivel alto máxima. VOHmin. Tensión de salida en nivel alto mínima. Si colocamos a la entrada de un dispositivo lógico una tensión comprendida entre VILmin y VILmáx el dispositivo interpretará que lo que hay es un ‘0’ lógico. Si la tensión se halla entre VIHmin y VIHmáx, entonces interpretará un ‘1’ lógico. Pero si la tensión de entrada se halla entre VILmáx y VIHmin, el dispositivo puede entender que hay un ‘0’ o ‘1’ lógico, por lo cual esta región se debe evitar. Corrientes de entrada y salida Igual que en el caso de las tensiones, en los dispositivos lógicos existen ciertos rangos de corriente, tanto en la entrada como en la salida. Corrientes de entrada IILmáx: es la corriente de entrada máxima en bajo. IIHmáx: es la corriente de entrada máxima en alto. Laboratorio N° 1 Prof. Roberto Martín Murdocca Pág. 3 de 18 Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica Corrientes de salida. IOLmáx: es la corriente de salida en bajo máxima y nos indica la capacidad que posee la puerta para absorber corriente. IOHmáx: es la corriente de salida en alto máxima y nos indica la capacidad que posee la puerta para suministrar corriente. Inmunidad al ruido El ruido es toda perturbación no deseada que si se presenta en una entrada de una compuerta puede producir un cambio no deseado en la salida. Algunas fuentes de ruido son el accionamiento de interruptores, motores, conexión de cargas inductivas, etc. La inmunidad al ruido mide la sensibilidad de un dispositivo digital al ruido electromagnético ambiental. Debemos tener presente este parámetro al diseñar sistemas que deban operar en ambientes hostiles como industrias, máquinas, automóviles, etc. Fan-In / Fan-out. El Fan-out indica el número máximo de compuertas lógicas que puede ser conectada a la salida de otra compuerta sin afectar la tensión de salida. El Fan-in representa la carga que presenta una compuerta a otra, esto es, la corriente que le saca a otra compuerta. El fan-out se expresa como un número que indica cuantos dispositivos de la misma familia pueden conectarse a una salida. Disipación de potencia. Debemos tener en cuenta este parámetro cuando vamos a realizar un diseño. Es importante minimizar el consumo de potencia, ya que esto afecta al diseño de la fuente de alimentación (costo y tamaño), además de producir calor en el sistema. Retardo de propagación El retardo de propagación (tP) es el tiempo que tarda una señal en propagarse desde la entrada hacia la salida, es decir, es el tiempo usado para que un cambio en la entrada produzca un cambio en la salida. El retardo de propagación limita la frecuencia de trabajo. A mayor retardo de propagación, menor frecuencia de trabajo. Familias TTL Su nombre viene de las iniciales Transistor Transistor Logic (Lógica Transistor Transistor) Se especifican mediante una referencia de la forma AA74XXYY, donde AA es un código de fabricante (SN, MM, DM, TC, etc.), XX indica la subfamilia (S, LS, AS, ALS, etc.) e YY indica la función del dispositivo. Por ejemplo el circuito integrado 74LS00 contiene 4 puertas NAND de 2 entradas de tecnología TTL Schottky de bajo consumo de potencia. Todos los dispositivos TTL usan como elemento de conmutación transistores bipolares. Laboratorio N° 1 Prof. Roberto Martín Murdocca Pág. 4 de 18 Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica Tensión de alimentación Lo dispositivos TTL trabajan con tensiones de 5V ±5%, por lo que pueden operar sin problemas en el rango de 4,75V a 5,25V. Alta velocidad de operación La familia TTL puede trabajar a frecuencias de 18 a 20MHz y en algunos casos hasta 80MHz. La velocidad de operación se expresa por lo general en términos del retardo de propagación del dispositivo. Alta disipación de potencia Esta es una desventaja de esta familia y esta asociada con la alta velocidad de trabajo. Por lo general cuanto más veloz sea un dispositivo, más potencia consume y viceversa. Casi todos los dispositivos TTL disipan, típicamente, de 1 a 25 mW por compuerta. Niveles lógicos de entrada y salida La lógica TTL reconoce cualquier tensión entre 0 y 0,8V como un cero lógico (‘0’) o bajo y cualquier tensión entre 2V y 5V como uno lógico (‘1’) o alto. La tensión positiva máxima aplicable a una entrada TTL es de +5,5V y el máximo negativo de -0,5V. Si nos excedemos de estos valores los dispositivos TTL se dañan. Inmunidad al ruido La inmunidad al ruido de cada estado lógico en la familia TTL estándar es de 0,4V. Familias CMOS La familia CMOS (MOS complementaria) es muy popular en la actualidad en el diseño de sistemas digitales debido a su muy bajo consumo de potencia, elevada capacidad de integración, buena inmunidad al ruido y su bajo consumo. Características de la familia CMOS La familia CMOS es junto con la TTL una de las más populares. Los circuitos integrados fabricados en tecnología CMOS se pueden clasificar en categorías o subfamilias: CMOS CMOS CMOS CMOS estándar. equivalente a TTL (C). de alta velocidad (HC). compatible con TTL (HCT). La familia CMOS estándar. La familia CMOS estándar comprende los dispositivos que se designan como 40xx (por ejemplo 4011, 4093, etc.) y 45xx (4511, 4518, etc.). Existen dos series en los dispositivos CMOS denominadas “A” y “B”. Los dispositivos de la serie “B” incorporan circuitos internos de protección para reducir el daño por descargas electrostáticas y poseen frecuencias de operación más altas, menores tiempos de propagación y mayor capacidad de salida (Fan-Out) que los de la serie “A”. Laboratorio N° 1 Prof. Roberto Martín Murdocca Pág. 5 de 18 Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica Disipación de potencia Es la ventaja más sobresaliente de esta familia. Una compuerta CMOS típica consume aprox.10 nW (nano watios). Esto es una ventaja muy grande en equipos portátiles. Velocidad Los dispositivos CMOS son más lentos que los TTL pero lo suficientemente rápidos para la mayoría de las aplicaciones. Pueden trabajar a frecuencias de hasta 10MHz y posen tiempos de propagación del orden de 10 a 50nS por compuerta. Tensión de alimentación Los dispositivos CMOS poseen un amplio rango de operación que va desde 3 a 18V. La tensión de alimentación se designa con VDD. Algunos sistemas digitales usan dispositivos CMOS y TTL en conjunto. En estos casos se utiliza una tensión de alimentación única de +5V. En el caso de que las tensiones de alimentación sean distintas, debemos utilizar una “interfaces” para hacer compatibles los niveles lógicos. Niveles lógicos Los dispositivos CMOS reconocen como ‘0’ lógico en sus entradas a niveles de tensión de 0 a 0.3 VDD, y reconocen un ‘1’ lógico tensiones entre 0.7 VDD y VDD. Por ejemplo si se alimenta un dispositivo CMOS con 10V, entonces interpretará una tensión entre 0 y 3V como ‘0’ lógico y una tensión entre 7 y 10V como ‘1’ lógico. VIL(máx) VIH(min) VOL(máx) VOH(min) 0,3 x VDD. 0,7 x VDD. 0. VDD. Inmunidad al ruido Esta es una característica muy sobresaliente de esta familia. Los dispositivos CMOS son esencialmente inmunes al ruido electromagnético externo. Fan-out Si no se requiere un funcionamiento de alta velocidad, se pueden conectar hasta 50 puertas a una misma salida. Retardo de propagación Los dispositivos CMOS estándar (serie 4000) son mucho más lentos que los TTL. Pero las subfamilias recientes han ido solucionando este hecho, por ejemplo los dispositivos 74ACXX y 74ACTXX poseen retardos de aproximadamente 7 ns mientras que los nuevos miembros LVT, ALVC, ALVT tienen retardos de 2.5 ns. Laboratorio N° 1 Prof. Roberto Martín Murdocca Pág. 6 de 18 Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica Interfaces entre familias lógicas Es importante conocer como hacen las distintas familias lógicas para comunicarse con cada una de las otras, dado que hay situaciones donde se deben utilizar más de una familia lógica. En la tabla 1 se ven las principales características de las familias lógicas. FAM VMN VMX 7400 74L 74S 74LS 74ALS 4000B 74C 74HC 74HC V 4.75 4.75 4.75 4.75 4.5 3 3 3 4.75 V 5.25 5.25 5.25 5.25 5.5 18 15 6 5.25 VIH VIL VOH VOL V V 2.0 0.8 2.0 0.8 2.0 0.8 2.0 0.8 2.0 0.8 2/3V V/3 3.5 1.5 3.5 1.5 2.0 0.8 V 2.4 2.4 2.7 2.7 2.5 Vcc 4.5 4.95 4.3 V 0.4 0.4 0.5 0.4 0.4 0.01 0.5 0.05 0.3 IIL IIH IOL IOH TPHL TPLH FMX PD mA uA mA mA 1.6 40 16 0.4 0.18 10 3.6 0.2 2.0 50 20 1 0.4 20 8 0.4 0.2 20 10 0.4 1uA 1 0.4 1.6 5nA 5nA 0.4 0.36 1uA 1 4 10 - nS 8 30 5 8 5 320 90 15 - nS 13 60 5 8 4 420 90 15 - MHz 35 3 125 45 32 2.5 2.0 25 - mW 10 1 19 2 1 * * * - Tabla 1. Características de las principales familias CMOS y TTL. 5.2 Interfaces entre familias Lógicas Muchas veces es necesario interconectar dispositivos de diferentes familias lógicas con el objeto de aprovechar las ventajas que ofrece cada tecnología. Para que la interconexión sea eficiente es necesario conocer las características de entrada y salida de cada familia lógica. 5.2.1 Interfaces de Dispositivos TTL a CMOS Una entrada CMOS es fácil de manejar desde una salida TTL cuando ambos operan a partir de una misma fuente de 5V. Las corrientes de salida TTL son más que suficientes para manejar una entrada CMOS, solo debemos adaptar los niveles de tensión. Veremos a continuación algunos circuitos para interconectar una entrada CMOS a una salida TTL. 5.2.2 De las hojas de datos correspondientes extraiga las características de los siguientes dispositivos y complete la tabla. Colocar las unidades correspondientes. VCC VOH VOL VIH VIL IOL IOH IIL IIH 74LS00 CD4011 74LS07 HEF4049 7400 Laboratorio N° 1 Prof. Roberto Martín Murdocca Pág. 7 de 18 Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica 5.2.3 Armar la siguiente interface en el LAB - MC, excitar la entrada (ENT) con niveles “alto” y “bajo”, medir las tensiones en los puntos indicados (TP, Test Points) y anotarlos en la tabla adjunta. Al realizar las mediciones comparar con los valores teóricos esperados. 74LS00 1 CD4011B 3 3 Los puntos indicados con TP son puntos de medida. 2 TP3 7 TP2 1 1 7 2 TP1 SAL 1 1 ENT 14 14 +5V R1 4K7 Figura A FIGURA A Tensión Medida ENT = ‘1’ ENT = ‘0’ TP1 TP2 TP3 5.2.4 ¿En este circuito por que se puede excitar una entrada CMOS desde una salida TTL si tenemos incompatibilidad en los niveles lógicos? Explique que función cumple la resistencia R1? .......................................................................... .......................................................................... .......................................................................... 5.2.5 Armar la siguiente interface en el LAB - MC, excitar las entradas con niveles “alto” y “bajo”, medir las tensiones en los puntos indicados y anotarlos en la tabla adjunta. +5V +9V 74LS00 74LS07 14 ENT CD4011B 4K7 3 1 14 14 1 2 1 2 SAL 3 2 TP4 1 7 TP3 1 TP2 1 TP1 1 7 7 Observar la conexión de la resistencia de pull-up del 74LS07. Figura B Laboratorio N° 1 Prof. Roberto Martín Murdocca Pág. 8 de 18 Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica FIGURA B Tensión Medida ENT = ‘1 ENT = ‘0’ TP1 TP2 TP3 TP4 5.2.6 ¿Si la entrada del 74LS07 y la alimentación poseen niveles TTL, por que se puede excitar la entrada CMOS con este dispositivo? .......................................................................... .......................................................................... 5.2.7 ¿En este circuito podemos omitir la resistencia R1? Justifique. .......................................................................... .......................................................................... 5.2.8 ¿Se puede reemplazar el 74LS07 por un 74LS04? Justifique. .......................................................................... .......................................................................... 5.2.9 Armar la siguiente interface en el LAB - MC, excitar las entradas con niveles “alto” y “bajo”, medir las tensiones en los puntos indicados y anotarlos en la tabla adjunta. +9V 5K6 74LS00 14 14 +5V 1 ENT 3 2 CD4011B 1 47K SAL 3 TP3 1 7 BC337 1 TP1 1 7 2 TP2 Figura C Tensión Medida FIGURA C ENT = ‘1 ENT = ‘0’ TP1 TP2 TP3 Laboratorio N° 1 Prof. Roberto Martín Murdocca Pág. 9 de 18 Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica 5.2.10 En este circuito explique la función que cumple el transistor BC337. .......................................................................... .......................................................................... 5.2.11 ¿Que característica importante presenta esta interface a nivel lógico? .......................................................................... .......................................................................... 5.2.12 Interfaces de dispositivos CMOS a TTL Una salida CMOS puede excitar una entrada 74LSxx o 74Lxx si ambos dispositivos operan a partir de una fuente de 5V. En el estado bajo, una entrada LS puede retornar hasta 400uA. Este es el valor máximo de corriente que puede drenar una salida CMOS en ese estado. 5.2.13 Armar la interface CMOS -TTL siguiente en el LAB - MC, excitar las entradas con nivel alto y bajo, medir las tensiones en los puntos indicados y anotarlos en la tabla adjunta. +9V CD4049A 1 ENT 14 CD4011B 1 14 +5V 74LS00 1 3 3 2 SAL 3 2 2 TP4 1 7 1 8 TP2 1 TP1 1 7 TP3 Figura A Tensión Medida FIGURA A ENT = ‘1’ ENT = ‘0’ TP1 TP2 TP3 TP4 5.2. 14 ¿En este circuito, se puede alimentar el CD4049 con 9V en lugar de 5V? ¿Por que? .......................................................................... .......................................................................... Laboratorio N° 1 Prof. Roberto Martín Murdocca Pág. 10 de 18 Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica 5.2.15 Armar la siguiente interface en el LAB - MC, excitar las entradas con niveles alto bajo, medir las tensiones en los puntos indicados y anotarlos en la tabla adjunta. Figura B Tensión Medida FIGURA B ENT=’1’ ENT=’0’ TP1 TP2 TP3 5.3. Interfaces E/S TTL y CMOS con dispositivos externos 5.3.1 Interface con LED’s Los LED se fabrican en distintos colores como rojo, ámbar, amarillo, verde, azul e infrarrojo. Existen LEDs especiales como los bicolores, los de alto brillo, los "flashing leds” (incluyen en su encapsulado un C.I) y los de luz blanca usados en linternas. La cantidad de luz emitida por un LED es proporcional a la corriente que circula por el mismo. Esta corriente nunca debe superar el valor máximo especificado por el fabricante. Para evitar superar esta máxima corriente se coloca una resistencia limitadora (RL) en serie con el mismo. Laboratorio N° 1 Prof. Roberto Martín Murdocca Pág. 11 de 18 Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica Circuitos Activos Cuando se utiliza un transistor como medio de excitación, como en la figura 2, el LED enciende cuando el transistor está en “alto” (conduciendo), y el valor de RL se calcula según la siguiente expresión: Excitación de un LED con transistor. Operación con Corriente Alterna (AC) Los LEDs deben alimentarse exclusivamente por voltaje directo DC. Si por algún motivo se prevé que el voltaje inverso podría exceder VR (voltaje inverso) máximo del componente, entonces se debe colocar una protección en el circuito. Esto se puede lograr de dos formas muy sencillas: en la figura 3a vemos que se coloca un diodo de uso general 1N914 en anti paralelo (paralelo inverso). Otra manera es como en la figura 3b colocando un segundo LED en la misma configuración. Si no existe circulación de corriente ninguno de los LED se enciende; si la corriente fluye en una u otra dirección se encenderá uno de los diodos, y el otro no. Los diodos LED de dos colores funcionan bajo este principio. Protección del LED contra voltajes inversos. Operación en Régimen de Pulso Podemos obtener una salida luminosa considerablemente mayor con un LED ordinario si lo alimentamos con pulsos de corriente elevados. Para que el dispositivo no se queme es necesario que los picos sean de breve duración y con un bajo ciclo de servicio. Si por ejemplo, la potencia total radiada por un LED alimentado de forma continua con una IF de 100 mA es de 2 mW, este LED irradia una potencia de 50 mW si se lo excita con una corriente de 6A en pulsos de 1μs, con un ciclo de servicio del 0.1%. Esta técnica además de ofrecer una mayor visibilidad permite ahorrar energía en equipo alimentados por baterías. Laboratorio N° 1 Prof. Roberto Martín Murdocca Pág. 12 de 18 Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica 5.4 Un driver muy utilizado: EL ULN2803 Veremos un dispositivo driver que permite realizar una gran cantidad de interfaces debido a su versatilidad. Este dispositivo es ampliamente utilizado para excitar lámparas, motores de C.C, motores paso a paso, reles, resistencias, etc. El ULN 2803 es un arreglo de transistores darlington con emisores comunes y diodos de supresión integrados para cargas inductivas. Cada transistor darlington puede manejar una corriente de pico de 650mA y 500mA en modo continuo. Las salidas pueden conectarse en paralelo para aumentar la capacidad de corriente de salida. Este dispositivo viene en un encapsulado DIP de 18 pines. Características principales § § § § § § 8 transistores darlington. Corriente de salida de 500mA. Voltaje de salida hasta 50V. Diodos de supresión internos. Las salidas pueden conectarse en paralelo. Pines de entrada en lado opuesto a la salida para facilitar diseño de PCB. 5.5 Interface con Relés Un rele es un dispositivo que usa el campo magnético creado alrededor de una bobina excitada por una corriente para abrir o cerrar uno o más contactos. Está constituido por un núcleo bobinado y uno o varios contactos, algunos normalmente cerrados (NC), otros normalmente abiertos (NA). Cuando se aplica tensión a la bobina, circula por ella una corriente que origina un campo magnético, este campo magnético hace que el núcleo de la bobina mueva los contactos y cambie la posición de los mismos. Es así que los contactos que antes estaban abiertos se cierran, y los que estaban cerrados se abren. Al suspender la corriente, los contactos regresan a su posición original (normal). Existen reles con uno o varios juegos de contactos. En la figura 4 vemos la estructura de un rele con un contacto simple inversor y en la figura 5 los símbolos utilizados. Laboratorio N° 1 Prof. Roberto Martín Murdocca Pág. 13 de 18 Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica Estructura de un rele. Símbolos. Características eléctricas de los reles Los reles se distinguen por sus características eléctricas, las cuales son: Tensión nominal de excitación de la bobina, expresada en volts. Corriente de accionamiento de la bobina, dada en mA. Corriente máxima soportada por los contactos. Tensión máxima soportada por los contactos. § § § § Como característica adicional podemos mencionara la resistencia de la bobina expresa en ohms. Esta relacionada obviamente con la tensión y la corriente de la bobina. Los reles se hallan disponibles para muchas tensiones de funcionamiento: 5, 6, 12, 24, 48, 60V, 110V, 220V, etc., de CC o CA. Por ejemplo: el rele G6A-234P de la empresa Omrom, posee una tensión de excitación de la bobina de 12VDC y los contactos soportan 6A - 250VAC. 5.5.1 Armar el siguiente circuito en el entrenador LAB-MC, medir la resistencia de la bobina del rele y calcular a corriente que circulará por el mismo. 5.5.2 Excitar la entrada de la compuerta y medir las corrientes indicadas en la tabla adjunta. 5.5.3 Identifique los terminales NC y NA del rele. 5V 12V Medición 14 5 1N4148 74LS00 4 1 LO 3 1 2 3 2 22K 7 RELE 12V BC337 Figura 6 RBOBINA I RELE(Med) I RELE (Cal) 5.5.4 ¿Qué función cumple el transistor en este circuito? ............................................................... ............................................................... ¿Cuál es la función del diodo en este circuito? ¿Qué podría suceder si se omite el mismo? ............................................................... ............................................................... Laboratorio N° 1 Prof. Roberto Martín Murdocca Pág. 14 de 18 Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica 5.5.5 ¿Cuál es la tensión y corriente máxima soportado por los contactos del rele? ............................................................... ............................................................... 5.5.6 Realice el esquema de un circuito para excitar el rele a través del ULN2803. 5.6 Interface con optoacopladores Los optoacopladores, también conocidos como optoaisladores, combinan en un mismo encapsulado un foto diodo (LED emisor) con un elemento de control sensible a la luz (foto-transistor, foto-TRIAC, etc.). El objetivo de esto es aislar físicamente la entrada de la salida, ya que no existe conexión eléctrica entre ellas. Se usan principalmente para controlar una etapa de alta tensión en un circuito con otra de baja tensión, por ejemplo una PC, un microcontrolador, un circuito digital, etc. Los opto-acopladores se usan también en electromedicina para aislar los electrodos aplicados al cuerpo humano, del circuito amplificador alimentado por la línea de 220V AC. En la figura 7 vemos uno de los opto-acopladores más utilizado, el 4N35. Figura 7. Opto-acoplador 4N35 y su respectivo encapsulado. Los opto-acopladores puede reemplazar a los a relés electromecánicos ya que tienen una mayor velocidad de conmutación y además no presentan rebotes. Tensión de aislamiento Esta característica se refiere al aislamiento de tensión entre entrada y salida. Esto depende de un separador físico entre emisor y receptor. Este material resiste tensiones del orden de miles de volts y posee una resistencia de aislamiento de alrededor de 1012 ohms. Por ej: el 4N25 posee una tensión de aislamiento de 2500V, y el 4N38 de 7500V. Laboratorio N° 1 Prof. Roberto Martín Murdocca Pág. 15 de 18 Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica Tipos de opto-acopladores Tenemos varios tipos de opto-acopladores cuya diferencia es el dispositivo que poseen a la salida. Algunos son: Salida fototransistor: poseen un transistor a la salida. Se usa en aplicaiones de baja tensión donde se necesite separar etapas de un circuito. Salida fototransistor darlington: poseen un transistor darlington a la salida. Se usa en aplicaciones donde se necesita mayor corriente a la salida, por ej: para manejar reles. Salida optotirristor (opto-SCR): posee un tiristor a la salida. Se usa en aplicaciones donde se deba separar la tensión de control de la de la red. Salida Triac: del mismo modo que el anterior se usa para aislar la etapa de control de la red. Salida Diac: especialmente indicados para disparar Triacs. Distintos tipos de opto-acopladores 1 6 1 6 5 5 4 2 2 Salida Transistor 4 Salida Darlington Entrada 3 diodos 1 + 5 4 6 2 Salida Smith Trigger Salida SCR Salida Diac - Triac 5.6.1 Obtenga las características de los siguientes opto acopladores: VF VR IF VCEO IC CTR VISO RISO TON TOFF 4N25 4N26 4N35 4N37 5.6.2 En el circuito de la figura siguiente calcular la corriente que circulara por la etapa de entrada (LED) y la corriente por la etapa de salida (transistor). 5.6.4 El circuito siguiente permite acoplar lógica TTL a un sistema alimentado con 12V (por ejemplo CMOS). Excitar la entrada de la compuerta ‘1’ lógico, luego con ‘0’ lógico y medir las tensiones de salida (SAL) del opto acoplador. Laboratorio N° 1 Prof. Roberto Martín Murdocca Pág. 16 de 18 Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica 14 5V 5V 7400 Tensión Medida 4K7 1 1 LO 12V 6 FIGURA A ENT =’1’ ENT = ‘0’ 470 3 V SAL 5 2 4 Salida 7 2 4N35 5.6.5 Que modificación debe realizar para conectar a la salida del opto acoplador una entrada CMOS alimentada con 9V. ............................................................... ............................................................... 6. Diseño de una interface de potencia Diseña una interface para controlar un rele de 12V en forma opto aislada. La entrada debe ser compatible con niveles TTL LS. Al aplicar un ‘1’ lógico se debe accionar el rele. Cuando la entrada esta en ‘0’ lógico debe permanecer inactivo. El circuito debe estar opto aislado. El relé controlará una carga que consiste de una resistencia calefactora de 220V AC – 4A. Se debe indicar con un LED la activación del RELE. El informe debe incluir todos los cálculos realizados, referencias de componentes, lista de materiales, valores de los resistores estándar (serie E-12). Características Niveles de entrada Corrientes de entrada Protección Salida Compatibles con TTL Compatibles con TTL LS Opto aislamiento. Rele 220V AC – 4A. Debe presentar un informe con el proyecto, donde figure el circuito, detalles del funcionamiento, cálculos de los componentes pasivos utilizados, y de nombre de los del grupo. Fecha límite entrega delintegrantes informe: 17/09/09 Fecha limite de entrega del informe: Laboratorio N° 1 17/09/09 Prof. Roberto Martín Murdocca Pág. 17 de 18 Ingeniería Electrónica con orientación en Sistemas Digitales Técnico Universitario en Microprocesadores Profesorado en Tecnología Electrónica 7. Anexo I. Componentes utilizados. HEF 4049: HEX Inverting Buffer. Posee 6 buffers inversores con alta capacidad de corriente capas de manejar cargas TTL. El voltaje de entrada puede superar al de alimentación. Convierte lógicas de hasta 15V a lógica TTL. 74LS00/7400: Quad 2-Input NAND Gates. Este dispositivo independientes. contiene 4 puertas NAND SN74LS07: HEX BUFFERS/DRIVERS WITH OPEN-COLLECTOR HIGH-VOLTAGE OUTPUTS Este dispositivo posee 6 buffers con salidas de colector abierto de alto voltaje. Puede manejar tensiones de salida de hasta 30V con una capacidad de corriente máxima de 40mA.. HEF 4011: Cuádruple compuertas NAND. Este dispositivo pose 4 compuertas NAND de 2 entradas. La alimentación es de 3 a 18V. BC337 Transistor NPN de uso general. Posee una corriente de colector máxima de 500mA y una tensión colector emisor máxima de 45V. ULN2803: Eight Darlington Arrays. Posee 8 transistores darlington de alta corriente y alta tensión. Cada transistor puede manejar es de 500mA. La tensión máxima de colector es de 50V. 4N35: GENERAL PURPOSE 6-PIN PHOTOTRANSISTOR OPTOCOUPLERS. Consiste de un LED emisor de arseniuro de Galio que excita un foto transistor de silicio en un encapsulado DIP de 6 pin. Laboratorio N° 1 Prof. Roberto Martín Murdocca Pág. 18 de 18