Boletin problemas Tecnologia memorias _03

Anuncio

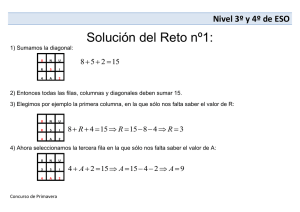

ARQUITECTURA DE COMPUTADORES. 2º INGENIERIA INFORMATICA. BOLETIN PROBLEMAS (Tecnología de los sistemas de memoria). Curso 03/04. 1) ¿Cuáles son las tres misiones más importantes de un controlador de memoria DRAM? 2) Se tiene el siguiente código que codifica una cadena de caracteres mediante la codificación del Cesar (a cada letra X se le suma un número para transformarla en la letra número X + 5 del abecedario): … char cadena[10000]; ... for ( i = 0; i < 10000; i++) cadena[i] = (cadena[i] – ‘a’ + 5) %26 + ‘a’; ... Este fragmento de código hace 10000 lecturas de un vector almacenado a partir de la posición/dirección de memoria A0000h. El procesador dispone de una memoria caché interna para instrucciones de forma que sólo accede a la memoria principal para acceder a los datos. Esto implica que a partir de la primera lectura de datos (cadena[0]) el procesador hace 9999 lecturas más en memoria principal. En esa primera lectura se debe acceder por primera vez a una fila de la matriz de datos del módulo de memoria correspondiente à primera “precarga RAS” o utilizando la notación vista en clase primer “ACTIVTE”. Se utiliza un sistema de memoria con varios chips/módulos de DRAM de 1Mb x 4, es decir, memorias de 1M de bus de direcciones con un bus de datos de 4 bits y por lo tanto con una capacidad total de 0,5MBs. ¿Cuál será el valor de la variable “i” cuando se produzca la segunda “precarga RAS”, es decir, cuando se tenga que acceder a otra nueva fila en los módulos de memoria? 3) Considere una RAM dinámica a la que deba darse un ciclo de refresco 64 veces por milisegundo. Cada operación de refresco requiere 150 ns. Un ciclo de memoria requiere 250 ns. ¿Cuál es el tiempo total de funcionamiento de la memoria que se pierde debido a los refrescos? 4) Considerar un sistema basado en un microprocesador 68000 con una memoria entrelazada de 2 vías/bloques de tamaño 2k bytes. El subsistema de memoria se diseña con chips de 2j posiciones de 2i bits (matriz de 2j x 2i bits). Utilizar el número de chips necesarios para diseñar el subsistema de memoria mostrando el circuito con todas las líneas de interconexión necesarias. Boletín problemas Tecnología de Memorias. Departamento de Arquitectura y Tecnología de Computadores. Universidad de Sevilla. 1 5) Se dispone de una memoria PC1600 (DDR200) que trabaja con un frecuencia real de 100 MHz. Concretamente se tiene un único chip de 4Mb x 8 y que también contiene un único banco de memoria. No se dispone de memoria caché para datos. La memoria puede trabajar en modo ráfaga 4. Sus principales características se muestran en los siguientes cronogramas: CL es la latencia CAS y t PR el tiempo de precarga. El “command” ACT selecciona una fila de un banco, el “command” READ selecciona una columna dentro de una fila y el “command” PRE (precarga) desactiva fila y columna seleccionada. Por otro lado el “command” NOP indica que no se envía ninguna operación a la memoria. En un programa de usuario se quiere sumar un uno a todos los elementos de una matriz cuadrada de números enteros de dimensión 100. Un número entero se representa mediante 4 bytes. La matriz se encuentra cargada a partir de la dirección de memoria 0h. ¿Cuánto tiempo emplea el programa en lo que son accesos a memoria? Indique número de ciclos y tiempo total. Boletín problemas Tecnología de Memorias. Departamento de Arquitectura y Tecnología de Computadores. Universidad de Sevilla. 2 RESPUESTAS Tecnología de los sistemas de memoria. Curso 03/04. 1) Como ya se ha visto en la teoría hay operaciones relativas al acceso a memoria DRAM que no son hechas ni por el procesador ni por el módulo de memoria. Esas operaciones son realizadas por un dispositivo externo llamado controlador de memoria que puede ir en el propio DIMM o en la placa base (chipset) del ordenador. Las tres funciones básicas que realiza son: 1- Refresco. Por ejemplo a los módulos de memoria SDRAM o DDR-DRAM les llegan periódicamente “mandatos” AUTO REFRESH o SELF REFRESH y mediante un hardware interno (contador) van refrescando las diferentes filas de los bancos de memoria. Estos “mandatos” son enviados por el controlador de memoria y a veces incluso la frecuencia de envío se puede modificar a través de la BIOS de un ordenador. Esto a veces hay que hacerlo si se produce un cambio de DIMMs o RDIMMs en el ordenador. 2- Arbitración. No siempre los módulos de memoria DRAM están disponibles para ser accedidos por parte del procesador. A veces la DRAM está ocupada por tareas concernientes al refresco. El controlador de memoria se encarga de dar paso a la petición de la CPU cuando no se esté realizando ninguna tarea de refresco. 3- Multiplexación direcciones. El procesador “ve” la memoria (caché, DRAM, disco duro) como un todo. Se dice que la memoria es “transparente” al procesador. Simplemente envía direcciones y envía/recibe datos. Por otro lado al módulo de DRAM le llega la dirección del procesador en dos partes: la fila y la columna, validadas por las señales RAS# y CAS# respectivamente. En medio por tanto, tiene que existir un circuito que como mínimo haga la múltiplexación y activación de las señales CAS# y RAS#. 2) Supongamos que se duplican los chips de memoria, es decir, se utilizan dos chips en paralelo. De esa forma por cada acceso se lee un byte y el bus datos por tanto son 8 bits. En cuanto al bus de direcciones está claro que son 20 bits ya que los chips son de 1M. En resumen, de cara al procesador se dispone de 1MB (un mega byte) = 220 bytes. Por cada página (fila) se podrán leer 210 columnas, o lo que es lo mismo 1024 elementos, ya que las direcciones son divididas por el controlador de memoria en dos partes: la fila (parte alta) y la columna (parte baja). Al leer el primer elemento del vector en el programa de usuario (cadena[0], i = 0), ¿qué fila y qué columna se seleccionan en la DRAM? Como “cadena[0]” está a partir de la dirección A0000h = 1010 0000 0000 0000 0000b, entonces la fila es 1010 0000 00b (diez bits de la parte alta de la dirección) y la columna es la 00 0000 0000b (diez bits de la parte baja de la dirección). El primer acceso por tanto es a la columna 0 y como hay 1024 columnas (de la 0 a la 1023) entonces cuando la dirección de la columna sea 11 1111 1111b = 1023, i valdrá 1023. En concreto la dirección que “marcará” una nueva fila será la A0400h = 1010 0000 0100 0000 0000b Boletín problemas Tecnología de Memorias. Departamento de Arquitectura y Tecnología de Computadores. Universidad de Sevilla. 3 4) En el esquema siguiente se van a representar el bus de direcciones (A1-23 ), el bus de datos (D0-15 ) y parte del bus de control (señales UDS# y LDS#) del microprocesador 68000. Faltarían las señales del bus de control R/W#, AS# y DTACK#. Por lo tanto sólo se muestra el diseño del sistema concerniente a la parte de decodificación de direcciones. Suponiendo que para simplificar k - 2 = j + i entonces cada bloque de chips será de la siguiente forma: Si j + i < k – 2 entonces habría que poner más configuración de 2i+j x 8 chips para cubrir los 2k-2 x 8 bits. Si j + i > k – 2 entonces habrá posiciones de memoria que no se usarán en esta configuración, es decir, se desaprovechará memoria. En cualquier caso k tiene que ser menor o igual que 24 ya que ese es el tamaño del bus de direcciones del 68000. Por otra parte cada chip de memoria del bloque tendrá una estructura como la que sigue: Boletín problemas Tecnología de Memorias. Departamento de Arquitectura y Tecnología de Computadores. Universidad de Sevilla. 4 3) 1ms = 1000 µs = 106 ns El periodo de refresco por tanto será 106 / 64 = 12625 ns Esto quiere decir que por cada 15625 ns se pierden 150 ns por motivos de refresco. El resto (15475 ns) se supone que es tiempo útil para realizar accesos a memoria. Por otro lado se dice que un ciclo de memoria (leer o escribir un dato en memoria) son 250 ns. Esto quiere decir que se podrán hacer 61 accesos a la DRAM y que el 62 no se podrá completar ya que 15475 ns / 250 ns por acceso = 61,9 accesos. En total 61 accesos como máximo. ¿Cuál es el tiempo perdido entonces al refresco? Para ello se va a calcular el porcentaje de ocupación de la memoria para acceso a información útil: 15625 ns 250 x 61 ns 100 % X X = 97,6 % del tiempo se accede a información útil à 100 % - 97,6 % = 2,4 % del tiempo perdido en refrescos El tiempo total perdido debido a los refrescos será por tanto: 15625 ns x 0,024 = 375 ns 5) Si se dispone de un memoria de 4Mb x 8, eso quiere decir que se tienen 4MBs en total. Como sólo hay un banco de memoria (y no se dice nada al respecto) la memoria no puede ser entrelazada. Por otro lado una dirección de memoria siempre se divide en dos partes: fila y columna. Por lo tanto hay 211 filas y en cada fila hay 211 columnas ya que 4MB = 211 *211 bytes. Como la memoria es de x8 cada vez que se lea una columna se estarán recuperando por el bus de datos 8 bits, o lo que es lo mismo, 1 byte. En ese caso para leer un número entero será necesario acceder 4 veces al chip, o lo que es lo mismo, leer 4 columnas (4 bytes) de una misma fila o de dos filas si el número da la mala suerte de que se almacena entre dos filas del chip. Casualmente ese es el tamaño de la ráfaga, por lo que por cada “command” READ se podrá leerá un número entero en dos ciclos de reloj reales (4 virtuales) con sólo tener Boletín problemas Tecnología de Memorias. Departamento de Arquitectura y Tecnología de Computadores. Universidad de Sevilla. 5 que mandar la dirección de inicio del número (primera columna). Previamente por supuesto habrá que haber seleccionado la fila con el “command” ACT, y si no es la primera vez que se utiliza ACT, previamente al ACT habrá que haber echo una precarga mediante el “command” PRE. ¿Cuántas filas hay que leer en el chip de DRAM? Si la matriz de datos del usuario es de dimensión 100 eso quiere decir que hay un total de 100 x 100 números enteros y por lo tanto hay que leer 100 x 100 x 4 bytes = 40000 bytes. En una fila de nuestro chip de memoria hay 211 bytes = 2048 bytes. Por lo tanto la matriz del programa estará almacenada en veinte filas consecutivas del chip (40000/2048 = 19,53). • En concreto las primeras 19 filas habrá que leerlas completamente à 211 bytes / 4 bytes por número entero (y ráfaga) = 512 números por fila y por lo tanto 512 “commands” READ consecutivos por fila. Recuérdese que cada “command” READ lee en modo ráfaga 4 columnas. El chip en cada acceso proporciona 8 bits (x8) de datos y por lo tanto al leer una columna se proporciona en la salida del chip 1 byte. • La última fila no se lee entera. 40000 – 2048*19 = 1088 bytes à 1088 bytes o columnas / 4 bytes por número entero = 272 números en la fila número 20 y por lo tanto también 272 “commands” READ. Resumiendo: - 20 “commands” ACT (uno por fila) - 20 “commands” PRE (al finalizar la lectura de la fila anterior. Si después de leer la última fila NO se quiere hacer precarga entonces serían 19 “commands” PRE) - 19 x 512 + 272 “commands” READ (como ya se ha visto, casualmente hay que hacer un sólo READ por cada número contenido en la matriz) Si ahora se quieren calcular el número de ciclos totales habrá que fijarse en los cronogramas para ver cuánto dura por ejemplo la lectura de una fila del chip. La secuencia de lectura de una fila en el chip DRAM es: primero se manda ACT (fila), luego diferentes READs (columnas) y finalmente PRE (precarga). En este caso no se utilizan/proporcionan READs o WRITREs con pre-carga incluida. De todas formas como las precargas hay que hacerlas de una u otra forma el hecho de haber utilizado unos “commands” u otros no altera el tiempo final. Entre un ACT y un READ como mínimo un 1 ciclo de reloj (real) ya que los mandatos (“commands”) se activan con un flanco de subida de la señal de reloj en las memorias DDR (y por supuesto también en las SDR). Realmente a la vista del cronograma tampoco está claro que sea un solo ciclo, pero como mínimo tiene que pasar un ciclo. Entre 2 READs consecutivos hay 2 ciclos de reloj (esa es la latencia CAS). Como hay 512 “commands” READ entonces 1024 ciclos. Finalmente tiempo de precarga tPR, PRE (precarga): 3 ciclos más antes del siguiente ACT (siguiente fila). Ver primer cronograma. Boletín problemas Tecnología de Memorias. Departamento de Arquitectura y Tecnología de Computadores. Universidad de Sevilla. 6 Total por fila completa: 1 (ACT) + 511*2 (READs) + 3 (PRE) = 1026 ciclos por fila Última fila: 1 (ACT) + 272 *2 (READs) + 3 (PRE, no estrictamente obligatorio) = 548 ciclos por la última fila TOTAL: 19 filas x tiempo fila completa + tiempo última fila = 19 x 1026 + 548 ciclos = 20042 ciclos. Si se quiere expresar en tiempo absoluto habrá que multiplicar los ciclos por la frecuencia. Como la frecuencia real es 100 MHz entonces el periodo es 10 ns. Por lo tanto el tiempo total es 20042 ciclos * 10 ns = 200420 ns , es decir, aproximadamente 0,2 ms Boletín problemas Tecnología de Memorias. Departamento de Arquitectura y Tecnología de Computadores. Universidad de Sevilla. 7