Tutor´ıa 2. Banco de memoria de 8 y 16 bits (8086)

Anuncio

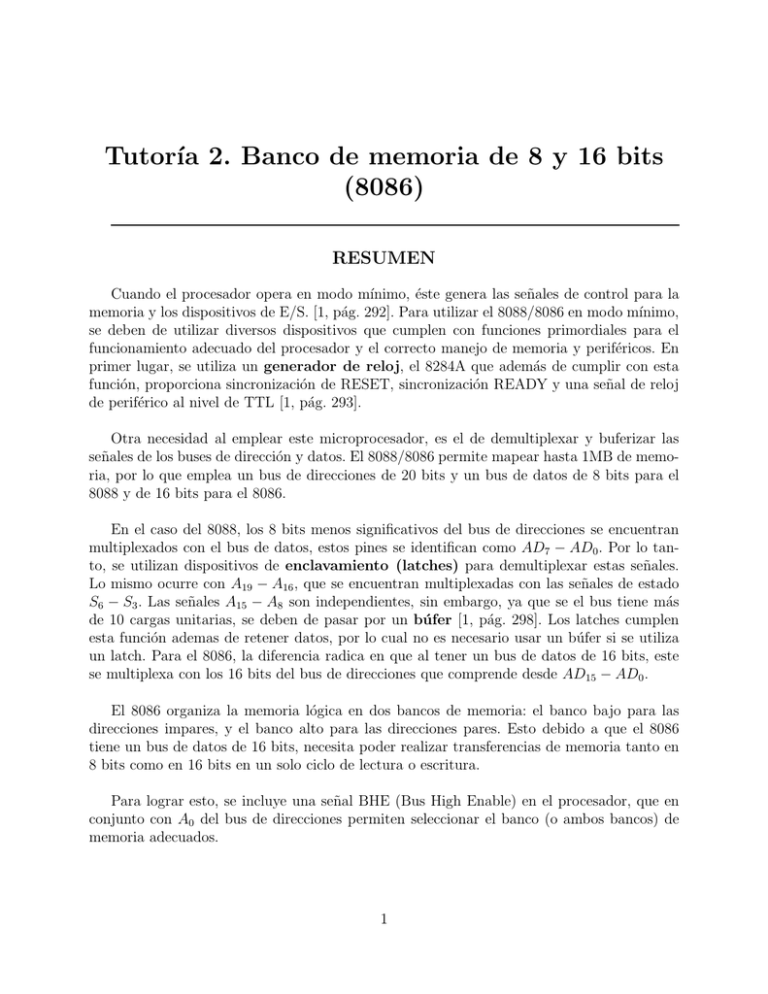

Tutorı́a 2. Banco de memoria de 8 y 16 bits (8086) RESUMEN Cuando el procesador opera en modo mı́nimo, éste genera las señales de control para la memoria y los dispositivos de E/S. [1, pág. 292]. Para utilizar el 8088/8086 en modo mı́nimo, se deben de utilizar diversos dispositivos que cumplen con funciones primordiales para el funcionamiento adecuado del procesador y el correcto manejo de memoria y periféricos. En primer lugar, se utiliza un generador de reloj, el 8284A que además de cumplir con esta función, proporciona sincronización de RESET, sincronización READY y una señal de reloj de periférico al nivel de TTL [1, pág. 293]. Otra necesidad al emplear este microprocesador, es el de demultiplexar y buferizar las señales de los buses de dirección y datos. El 8088/8086 permite mapear hasta 1MB de memoria, por lo que emplea un bus de direcciones de 20 bits y un bus de datos de 8 bits para el 8088 y de 16 bits para el 8086. En el caso del 8088, los 8 bits menos significativos del bus de direcciones se encuentran multiplexados con el bus de datos, estos pines se identifican como AD7 − AD0 . Por lo tanto, se utilizan dispositivos de enclavamiento (latches) para demultiplexar estas señales. Lo mismo ocurre con A19 − A16 , que se encuentran multiplexadas con las señales de estado S6 − S3 . Las señales A15 − A8 son independientes, sin embargo, ya que se el bus tiene más de 10 cargas unitarias, se deben de pasar por un búfer [1, pág. 298]. Los latches cumplen esta función ademas de retener datos, por lo cual no es necesario usar un búfer si se utiliza un latch. Para el 8086, la diferencia radica en que al tener un bus de datos de 16 bits, este se multiplexa con los 16 bits del bus de direcciones que comprende desde AD15 − AD0 . El 8086 organiza la memoria lógica en dos bancos de memoria: el banco bajo para las direcciones impares, y el banco alto para las direcciones pares. Esto debido a que el 8086 tiene un bus de datos de 16 bits, necesita poder realizar transferencias de memoria tanto en 8 bits como en 16 bits en un solo ciclo de lectura o escritura. Para lograr esto, se incluye una señal BHE (Bus High Enable) en el procesador, que en conjunto con A0 del bus de direcciones permiten seleccionar el banco (o ambos bancos) de memoria adecuados. 1 Tutorı́a 2. Banco de memoria de 8 y 16 bits (8086) Figura 1: Organización de la memoria lógica en 8086 Existen otros dispositivos que se utilizan como parte del sistema mı́nimo. Por ejemplo, cuando se van a utilizar tanto elementos de memoria como de Entrada/Salida para comunicarse con el usuario u otros sistemas, es importante proveer de señales de control de escritura y lectura para cada tipo de dispositivo. Por esta razón se suele implementar un decodificador de control. Cuando se habla de banco de memoria o interfaz de memoria, se debe de identificar dos tipos de memoria principales: la memoria de sólo lectura (ROM) y la memoria de acceso aleatorio (RAM). La memoria ROM se utiliza para contener datos permanentes del sistema y software. Por otro lado, la memoria RAM se accede para almacenar datos en tiempo de ejecución y software de aplicaciones. Algunas veces los elementos fı́sicos de memoria disponibles no son suficientes de modo que se pueda implementar toda la memoria requerida en un sólo dispositivo. Por esta razón, se utiliza un decodificador de memoria que se encarga de asignar a cada dispositivo de memoria fı́sica una parte de la memoria lógica. 2 Tutorı́a 2. Banco de memoria de 8 y 16 bits (8086) PRÁCTICA DE DISEÑO DE BANCO DE MEMORIA CON 8088 y 8086 Para fin didáctico, en este caso se diseñará el banco de memoria de una microcomputadora tanto con un procesador 8088 (8 bits de bus de datos) y un 8086 (16 bits de bus de datos) para observar las diferencias entre el diseño de ambos bancos de memoria. Las especificaciones de diseño son la siguientes: Frecuencia de operación del sistema de 8 Mhz. Implementar lógica de demultiplexación de buses y enclavamiento de señales Usar un generador de reloj 8284A para el microprocesador. Implementar memoria de código de programa en las direcciones E0000H − F F F F F H del mapa de memoria total. Implementar un solo segmento de 64 KB de memoria de datos. Este único segmento debe contener los vectores de interrupción del microprocesador para cumplir con las especificaciones de Intel. Para desarrollar y demostrar la solución de esta etapa debe realizar lo siguiente: 1. Realizar el mapa de memoria fı́sico y lógico. 2. Realizar el diseño del decodificador para la selección de memoria y el decodificador de señales de control de lectura/escritura. Para esto debe de mostrar un diagrama de bloques con las correspondientes señales de entrada y salida de cada uno de los decodificadores, y ademas, debe de justificar los diagramas mediante su respectiva tabla de verdad. 3. Realizar el circuito esquemático con la conexión fı́sica del CPU con: el generador de reloj, demultiplexación de los buses de datos y direcciones, enclavamiento de señales de control, dispositivos de memoria y decodificadores de selección de memoria y de señales de control de escritura y lectura. 3 Tutorı́a 2. Banco de memoria de 8 y 16 bits (8086) SOLUCIÓN 1. 1. Mapeo de memoria Para realizar el mapeo de la memoria requerida, hay que cumplir con una restricción importante predispuesta por el fabricante del procesador. En la hoja de datos del 8088 de Intel, se indica que existen localidades de memoria reservadas por el procesador tanto en memoria ROM como en memoria RAM [2, pág. 7]. Estas localidades comprenden en memoria ROM las direcciones FFFF0H hasta FFFFFH para vector de reset, y en RAM las localidades desde 00000H hasta 003FFH para los vectores de interrupciones. Estos 256KB para interrupciones constan de vectores de interrupción con 4 bytes cada uno, que contienen 2 bytes para la dirección del segmento y 2 bytes para el offset. El usuario debe como parte de la programación asignar estos valores para el correcto funcionamiento de las interrupciones que vaya a utiilizar. El mapeo de memoria lógica representa la ubicación de los segmentos de memoria de código (ROM) y de datos (RAM) en el espacio de 1MB que puede direccionar el microprocesador. La figura 2 muestra el mapa de memoria lógica a implementar en el caso de estudio. El mismo consta del espacio de memoria ROM requerido que va desde E0000H hasta FFFFFH, es decir, 128KB. La memoria RAM debe ser de 64KB en un sólo bloque, y para cumplir con la restricción de Intel, se coloca desde la dirección 00000H. 4 Tutorı́a 2. Banco de memoria de 8 y 16 bits (8086) Figura 2: Mapa de memoria lógica Para realizar un mapeo que comprenda los dispositivos reales de memoria para implementar el diseño, se debe tomar en cuenta la cantidad de memoria que estos chips pueden manejar: Cuadro 1: Dispositivos de memoria Dispositivo 27512 62256 Tipo de memoria EPROM SRAM Cantidad de memoria 64KB x 8 32KB x 8 Considerando la capacidad de estos dispositivos, se puede realizar un mapa de memoria más completo conforme a la implementación del diseño. Este es el mapa fı́sico y se debe de concebir diferente para el 8088 y el 8086. En el caso del 8088, se necesitan dos chips de cada tipo de memoria para lograr alcanzar la memoria deseada. Como la arquitectura es de 8 bits y las memorias también lo son, esto permite que su implementación sea directa. La figura 3 muestra cómo para implementar cada segmento de memoria con 8088. 5 Tutorı́a 2. Banco de memoria de 8 y 16 bits (8086) Figura 3: Mapa de memoria fı́sica para 8088 Como en el 8086 la memoria se organiza en dos bancos de memoria, es necesario que cada segmento de memoria se encuentre dividido en dos segmentos de la mitad de la memoria. En este caso se pueden utilizar la misma cantidad de dispositivos de memoria RAM y ROM, pero la conexión difiere tanto para el bus de direcciones: 6 Tutorı́a 2. Banco de memoria de 8 y 16 bits (8086) Figura 4: Mapa de memoria fı́sica para 8086 Para realizar la tabla de verdad se debe de tomar en cuenta las lı́neas del bus de direcciones que ocupa cada memoria. Ası́ entonces, la parte del bus de direcciones más alta que no soporten las memorias, es la que será clave para su correcta selección por medio del decodificador de memoria. El 62256 se direcciona con 15 bits, mientras que el 27512 se direcciona con 16 bits. En el caso del 8088 la tabla de verdad queda como la figura 5, se observa que se separa cada memoria la cual guarda un espacio de todo el bloque de memoria. En 8086 la tabla varı́a ligeramente, puesto que en este caso cada bloque de memoria esta conformado por dos memorias cada una con las direcciones pares e impares, tal como se observa en la figura 6. 7 Tutorı́a 2. Banco de memoria de 8 y 16 bits (8086) Figura 5: Tabla de verdad de la memoria lógica en 8 bits Figura 6: Tabla de verdad de la memoria lógica en 16 bits 2. 2.1. 2. Diseño de decodificadores de memoria y de señales de control Decodificador de memoria El decodificador utiliza las direcciones de memoria más altas del procesador que los chips de memoria no pueden manejar, de manera que se logra la convergencia entre el mapeo de memoria lógica y fı́sica. Además este decodificador está controlado por la señal IO/M (en 8 Tutorı́a 2. Banco de memoria de 8 y 16 bits (8086) 8088) o M /IO (en 8086), la cual es utilizada por el procesador para definir cuándo se debe acceder a la memoria o a un dispositivo de entrada/salida. Ası́, se logra decodificar las señales de selección de cada chip (chip select). La figura 7 muestra el diagrama de bloques de señales de este decodificador en 8088. Importante!: Para saber cuales lı́neas de direcciones son necesarias para el decodificador de memoria, identifique cual es el dispositivo de memoria con menor capacidad. Las lı́neas del bus de direcciones del procesador que sobren para controlar este dispositivo serán las que se usen para el decodificador. En el caso de 8088, como el 62256 utiliza hasta A14 , el decodificador ocupará las lı́neas A19 − A15 . Figura 7: Diagrama de bloque del decodificador de memoria en 8088 La tabla de verdad que justifica este decodificador se muestra a continuación: Figura 8: Tabla de verdad del decodificador de memoria en 8088 En el caso del 8086, para poder utilizar ambos bancos de memoria, bajo y alto, se utiliza la señal BHE en conjunto con A0 para realizar la selección de los bancos. Estas señales por lo tanto se incluyen en el decodificador de memoria, tal como se observa en la figura 9. Su tabla de la verdad se muestra en la figura 10. 9 Tutorı́a 2. Banco de memoria de 8 y 16 bits (8086) Figura 9: Diagrama de bloque del decodificador de memoria en 8086 Figura 10: Tabla de verdad del decodificador de memoria en 8086 2.2. Decodificador de señales de control escritura/lectura Este decodificador se utiliza para separar las señales que se utilizan en la escritura o lectura ya sea de un dispositivo de memoria o, por otro lado, de un dispositivo de entrada/salida. Como entradas se utilizan las señales del microprocesador RD y W R para cada tipo de transferencia, IO/M para indicar qué clase de dispositivo el procesador debe acceder, y además se conecta la señal HLDA, utilizada cuando existe un dispositivo periférico (como un DMA) que provee externamente las señales de control para el control de los buses de datos y direcciones, por lo cual inhabilitarı́a las señales de control del procesador. La tabla de verdad de este decodificador se muestra a continuación: Recuerde que este decodificador nunca se ve afectado por la cantidad o los tipos de memorias que se vayan a implementar. Observe que cada una de las señales sólo se activa en un 10 Tutorı́a 2. Banco de memoria de 8 y 16 bits (8086) Figura 11: Diagrama de bloque del dcodificador de control de señales de escritura y lectura Figura 12: Tabla de verdad del decodificador de control estado especı́fico: cuando el microprocesador envı́a sólo una petición de lectura o de escritura, pero no ambas ni ninguna. Además cuando HLDA está activo se deben de liberar las señales, por lo cual se conectan a un ’244 (buffer) después del decodificador y para asi poder configurarlas en alta impedancia cuando se requiere. 3. Diagrama esquemático El diagrama esquemático debe de llevar la conexión fı́sica del CPU con el generador de reloj (señales de CLK, READY y RESET), demultiplexación de los buses de datos y direcciones (con latches), enclavamiento de señales de control (buffer), todas las memorias SRAM y EPROM, y tanto el decodificador de selección de memoria ası́ como el de señales de control de escritura y lectura. Consejo: Antes de realizar el diagrama esquemático: 11 Tutorı́a 2. Banco de memoria de 8 y 16 bits (8086) Haga un planeamiento de donde colocar todos los dispositivos. Extienda los buses de datos y direcciones lo necesario para conectar las memorias. Etiquete todas las señales y los bloques, especialmente cuando se necesita utilizar una señal de un extremo a otro del esquemático. Referencias [1] Brey, B.: Microprocesadores Intel, 7ma edición. Pearson Educación de México, 2006. [2] Intel: 8088 8-BIT HMOS MICROPROCESSOR, Data sheet, August 1990. [3] Carvajal, J.: Interfaz de memoria con 8086/8088, ITCR, Curso Estructura de Microprocesadores, 2009. 12