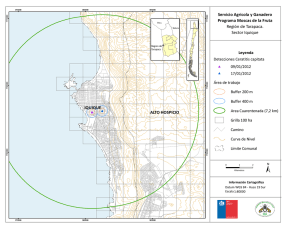

Figura 6

Anuncio