Estudio de utilización efectiva de procesadores vectoriales

Anuncio

Universidad de Las Palmas de Gran Canaria

Estudio de utilización efectiva de

procesadores vectoriales

Proyecto de Fin de Carrera

Ingenierı́a en Informática

Laura Autón Garcı́a

Tutores:

Francisca Quintana Domı́nguez

Roger Espasa Sans

Las Palmas de Gran Canaria, 9 de julio de 2014

Agradecimientos

Quiero agradecer a Francisca Quintana y a Roger Espasa, mis tutores de proyecto, el haberme

brindado la oportunidad de adentrarme en una experiencia que bien podrı́a ser el sueño de cualquier futuro ingeniero informático cuando avista cada vez más cerca la meta de su esfuerzo. Este

viaje no solo ha dado como resultado el presente trabajo, sino también la satisfacción profesional de haber trabajado en Intel, empresa puntera en el ámbito de la computación, y personal de

haber trabajado con extraordinarios ingenieros a la vez que fantásticas personas durante todo el

proceso. Entre ellos, quiero agradecer especialmente a Manel Fernández por la enorme paciencia

y dedicación con las que consiguió guiarme cuando me desviaba del camino, y a Jesús Sánchez

porque su buen humor y positivismo amenizaba todas las tormentas de ideas, por muy oscuras

que pudieran divisarse a lo lejos.

Del mismo modo, quiero agradecer muy especialmente a Susana y Delfı́n, por haber sido

mi familia durante mi estancia en Canarias. A mis padres, Marı́a y Cándido por haber sabido

apoyarme desde la distancia con sus palabras al otro lado del teléfono. Y a Raúl, mi gran compañero

en este viaje, porque ha sido la única persona de este mundo que realmente ha conocido mis más

profundas inquietudes, y que ha sabido iluminarme el camino y cederme las mangas sobre las que

derramar mis lágrimas.

i

Índice de figuras

2.1. SISD . . . . . . . . . . . .

2.2. SIMD . . . . . . . . . . .

2.3. MISD . . . . . . . . . . .

2.4. MIMD . . . . . . . . . . .

R Xeon PhiTM . . .

2.5. Intel

2.6. Esquema general . . . . .

2.7. Microarquitectura . . . .

2.8. Vector Processing Unit . .

2.9. Interconexion . . . . . . .

2.10. Directorio de etiquetas . .

2.11. Controladores de memoria

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

5

5

5

5

9

9

10

10

11

11

12

4.1. Arquitectura software de Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22

5.1.

5.2.

5.3.

5.4.

5.5.

5.6.

Diagrama de funcionamiento CMP$im . . . .

Simulación en modo buffer . . . . . . . . . .

Simulación en modo instrucción a instrucción

Ejemplo de bloque básico . . . . . . . . . . .

Proceso de descubrimiento de bloques . . . .

Punteros a objetos cache . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

31

32

33

34

34

36

6.1. Índice de vectorización de las aplicaciones de Polyhedron .

6.2. Razones para no vectorizar bucles en Polyhedron . . . . .

6.3. Índice de vectorización de las aplicaciones de Mantevo 1.0

6.4. Razones para no vectorizar bucles en Mantevo 1.0 . . . .

6.5. Índice de vectorización de las aplicaciones de Sequoia . . .

6.6. Razones para no vectorizar bucles en Sequoia . . . . . . .

6.7. Índice de vectorización de las aplicaciones de NPB . . . .

6.8. Razones para no vectorizar bucles en NPB . . . . . . . . .

6.9. Índice de vectorización de las aplicaciones de SPEC fp . .

6.10. Razones para no vectorizar bucles en SPEC fp . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

40

41

42

43

44

44

45

46

47

48

7.1.

7.2.

7.3.

7.4.

7.5.

7.6.

7.7.

Pipeline dentro de CMP$im . . . . . . . . . . . . .

Pipeline del bloque de s171 . . . . . . . . . . . . .

Localización del simulador de pipeline en CMP$im

Idea para la implementación de KNC . . . . . . . .

Instrucción que toca dos lı́neas . . . . . . . . . . .

Bloques con ningún y un corte . . . . . . . . . . .

Bloques con 2 cortes . . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

50

52

56

56

58

63

64

8.1.

8.2.

8.3.

8.4.

8.5.

Versión vectorizada vs no vectorizada de Polyhedron

Ciclos desglosados de las aplicaciones de Polyhedron

Versión vectorizada vs no vectorizada de Mantevo .

Ciclos desglosados de las aplicaciones de Mantevo . .

Versión vectorizada vs no vectorizada de Sequoia . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

66

67

69

69

70

iii

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

ÍNDICE DE FIGURAS

iv

8.6. Ciclos desglosados de las aplicaciones de Sequoia . . . .

8.7. Versión vectorizada vs no vectorizada de NPB . . . . . .

8.8. Ciclos desglosados de las aplicaciones de NPB . . . . . .

8.9. Versión vectorizada vs no vectorizada de SPEC fp . . .

8.10. Ciclos desglosados de las aplicaciones de SPEC fp 2006 .

8.11. Comparación entre las versiones :nodes y do de gas dyn

8.12. Resultado de doblar la UL2 de 1024Kb a 2048Kb . . . .

8.13. Mejora de SPEC fp/433.milc al doblar la L2 . . . . . . .

8.14. Consecuencia posible por aumento de aciertos en L2 . .

8.15. Resultado de doblar las lı́neas de DTLB2 de 256 a 512 .

8.16. Mejora de IS de NPB al doblar la TLB . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

. 70

. 71

. 72

. 73

. 73

. 84

. 97

. 98

. 99

. 100

. 100

Índice de tablas

R ICC . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1. Knobs soportados por Intel

28

6.1.

6.2.

6.3.

6.4.

6.5.

.

.

.

.

.

40

42

43

45

47

7.1. Latencias de memoria y de instrucción (load-op) . . . . . . . . . . . . . . . . . . .

51

8.1. Bloques 1 y 2 de la lista de bloques básicos más ejecutados en Fatigue, Polyhedron

8.2. Bloque 3 de la lista de bloques básicos más ejecutados en Fatigue, Polyhedron . . .

8.3. Bloques 1, 2, 4 y 5 de la lista de bloques básicos más ejecutados en Induct, Polyhedron

8.4. Bloques 1 y 2 más ejecutados de Aermod, Polyhedron . . . . . . . . . . . . . . . .

8.5. Bloques 3, 5 y 10 más ejecutados de Aermod, Polyhedron . . . . . . . . . . . . . .

8.6. Bloques 7 y 9 más ejecutados de Aermod, Polyhedron . . . . . . . . . . . . . . . .

8.7. Bloque 8 más ejecutado de Aermod, Polyhedron . . . . . . . . . . . . . . . . . . .

8.8. Desglose de instrucciones de las versiones escalar y vectorial de Gas dyn, Polyhedron

8.9. Bloques 1 y 3 más ejecutados de Gas dyn, Polyhedron . . . . . . . . . . . . . . . .

8.10. Bloques 1, 2, 3 y 4 más ejecutados de SPhotmk, Sequoia . . . . . . . . . . . . . . .

8.11. Bloque 1 de los más ejecutados de BT, NPB . . . . . . . . . . . . . . . . . . . . . .

8.12. Bloques 1 y 2 de los más ejecutados de LU, NPB . . . . . . . . . . . . . . . . . . .

8.13. Bloques 1 y 2 de los más ejecutados de Povray, SPEC FP . . . . . . . . . . . . . .

8.14. Aplicaciones con una mejora inferior al 1 % . . . . . . . . . . . . . . . . . . . . . .

75

76

77

79

80

80

82

82

83

88

90

91

94

97

Desglose

Desglose

Desglose

Desglose

Desglose

de

de

de

de

de

instrucciones

instrucciones

instrucciones

instrucciones

instrucciones

de

de

de

de

de

las

las

las

las

las

aplicaciones

aplicaciones

aplicaciones

aplicaciones

aplicaciones

de

de

de

de

de

Polyhedron

Mantevo . .

Sequoia . .

NPB . . . .

SPEC FP .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

R ICC Specific Pragmas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

A.1. Intel

R ICC Supported Pragmas . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

B.1. Intel

R Fotran Directives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

C.1. Intel

D.1. Mensajes del compilador . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

v

Índice general

Agradecimientos

I

Lista de figuras

VIII

Lista de tablas

VIII

1. Introducción

1.1. Objetivos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2. Estado del arte

2.1. Taxonomı́a de Flynn . . . . . . . . . . . . . . .

2.2. Vectorización . . . . . . . . . . . . . . . . . . .

2.2.1. SIMD . . . . . . . . . . . . . . . . . . .

R Xeon PhiTM Coprocessor . . . . . . . .

2.3. Intel

2.3.1. Microarquitectura . . . . . . . . . . . .

R Advanced Vector Extensions . . . . . .

2.4. Intel

R Advanced Vector Extensions 1 .

2.4.1. Intel

R Advanced Vector Extensions 2 .

2.4.2. Intel

R Advanced Vector Extensions 512

2.4.3. Intel

1

2

.

.

.

.

.

.

.

.

.

3

4

5

5

8

9

13

13

13

13

3. Metodologı́a

3.1. Plan de trabajo . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15

15

4. Herramientas

4.1. Pin . . . . . . . . . . . . . . . . . . . . .

4.1.1. Pintools . . . . . . . . . . . . . .

4.1.2. Arquitectura software . . . . . .

4.2. CMP$im . . . . . . . . . . . . . . . . . .

4.3. Benchmarks . . . . . . . . . . . . . . . .

4.3.1. Polyhedron Fortran Benchmarks

4.3.2. Mantevo 1.0 . . . . . . . . . . . .

4.3.3. ASC Sequoia Benchmark Codes .

4.3.4. NAS Parallel Benchmarks . . . .

4.3.5. SPEC CPU 2006 . . . . . . . . .

4.4. Compiladores . . . . . . . . . . . . . . .

4.4.1. ICC . . . . . . . . . . . . . . . .

4.4.2. IFORT . . . . . . . . . . . . . .

4.5. Pragmas . . . . . . . . . . . . . . . . . .

4.6. Herramientas internas . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

19

19

19

21

22

23

24

25

25

25

26

27

27

28

29

29

5. Arquitectura del Simulador

5.1. Flujo de ejecución . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2. Estructuras y clases . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3. Parámetros de ejecución . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

31

31

33

37

vii

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

ÍNDICE GENERAL

viii

6. Caracterización de benchmarks

6.1. Polyhedron . . . . . . . . . . .

6.2. Mantevo 1.0 . . . . . . . . . . .

6.3. Sequoia . . . . . . . . . . . . .

6.4. NPB . . . . . . . . . . . . . . .

6.5. SPEC FP . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

39

39

41

42

43

46

7. Adaptación del Simulador

7.1. Pipeline . . . . . . . . . . . . . . . . . . . . . .

7.2. Detección de instrucciones y registros . . . . .

7.2.1. Instrucciones . . . . . . . . . . . . . . .

7.2.2. Registros . . . . . . . . . . . . . . . . .

7.2.3. Latencias . . . . . . . . . . . . . . . . .

7.3. Nuevas estructuras y clases . . . . . . . . . . .

7.4. Estadı́sticas . . . . . . . . . . . . . . . . . . . .

7.5. Invocación activando la funcionalidad vectorial

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

49

49

53

53

54

54

55

62

64

8. Estudio experimental

8.1. Resultados . . . . . . . . . .

8.1.1. Polyhedron . . . . .

8.1.2. Mantevo . . . . . . .

8.1.3. Sequoia . . . . . . .

8.1.4. NPB . . . . . . . . .

8.1.5. SPEC fp . . . . . . .

8.2. Diagnóstico Software . . . .

8.2.1. Polyhedron . . . . .

8.2.2. Mantevo . . . . . . .

8.2.3. Sequoia . . . . . . .

8.2.4. NPB . . . . . . . . .

8.2.5. SPEC fp . . . . . . .

8.3. Diagnóstico Hardware . . .

8.3.1. Incremento de UL2 .

8.3.2. Incremento de TLB

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

65

65

65

68

70

71

72

74

75

84

86

89

92

96

97

99

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

9. Conclusiones

101

9.1. Trabajo Futuro . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

R ICC Specific Pragmas

A. Intel

105

R ICC Supported Pragmas

B. Intel

109

R Fortran Directives

C. Intel

113

D. Mensajes del compilador

117

Capı́tulo 1

Introducción

Echando una profunda mirada al pasado para recorrer toda la historia de la informática, desde

donde venimos, en qué punto nos encontramos y a dónde vamos, nos damos cuenta del gran esfuerzo

que ha hecho y sigue haciendo el ser humano para no solo automatizar tareas, sino también para

que éstas se hagan lo más rápido posible. Y es que, ya en su momento, para realizar cálculos

balı́sticos de gran utilidad en posibles contiendas, se incrementaba el número de personas que

realizaban una tarea. Al segmentar el trabajo se conseguı́a realizar la tarea en menos tiempo de lo

que lo conseguirı́a una sola. A estas personas se las denominaba antiguamente computers[Bar08],

nombre que más tarde se adoptó para las máquinas que sustituyeron su trabajo.

Desde entonces, la capacidad de cómputo de las máquinas ha ido evolucionado enormemente

gracias a, por ejemplo, la cantidad de transistores que fuimos capaces de insertar dentro de una

onza de silicio y que bien supo pronosticar Gordon Moore, cuya afirmación se bautizo como Ley

de Moore. Cuando las limitaciones fı́sicas se convirtieron en un problema, empezamos a introducir

más núcleos en un mismo procesador: primero dos, luego cuatro... Está claro que, sean los motivos

que sean los que impulsen al ser humano a seguir escudriñando mejoras en cualquier tipo de

artefacto, mecanismo o sistema que tenga entre manos, y sobre el que haya trabajado desde

tiempos inmemoriales, el mundo, inexorablemente, se sigue moviendo. Y es en ese mundo en

constante cambio y movimiento, donde acaban por surgir ideas como aquella sobre la que se ha

construido el trabajo que se presenta: la vectorización.

Hoy en dı́a, una importante muestra de procesadores disponibles en el mercado disponen de

unidades de cómputo, denominadas vectoriales, que permiten la explotación de este concepto. Y

es que la vectorización explota un caso particular de paralelismo cuyo objetivo consiste en realizar

la misma operación, en vez de sobre un único dato como venı́a siendo hasta ahora, sobre la mayor

cantidad de datos contenidos en un vector que le sea posible. Por ello, se denomina DLP (Data

Level Parallelism) o Paralelismo de datos. Algunos de estos procesadores, por ejemplo, son los de

R basados en la arquitectura Sandy Bridge que, con el objetivo de permitir la explotación del

Intel

paralelismo de datos, incluyen extensiones AVX (Advanced Vector Extensions) sobre el repertorio

de instrucciones x86. Sin embargo, esta obra de ingenierı́a no es suficiente por sı́ sola. Es necesario

un engranaje más, y que no es otro que un compilador especialmente construido para máquinas

como estas, que sea capaz de extraer el mayor paralelismo de datos posible de una aplicación.

Pese a que todos los elementos mencionados conforman la receta perfecta para sacar el mayor

rendimiento posible a aplicaciones que requieren de una importante capacidad de cómputo, no

siempre se obtienen los resultados esperados. Las razones pueden residir tanto en el software como

en el hardware. Puede que la aplicación no experimente las mejoras esperadas después de ser

vectorizada. Es posible que el compilador no sea capaz por sı́ mismo de encontrar potenciales

secciones de código vectorizables debido a ambigüedades en el acceso a los datos. O bien, podrı́a

1

2

CAPÍTULO 1. INTRODUCCIÓN

ser que la memoria esté suponiendo un cuello de botella a la hora de recuperar los datos sobre los

que operar.

Basándonos pues en la realidad descrita, se propuso la realización del trabajo que se detalla

en este documento, con el objetivo fundamental de determinar el grado de utilización efectiva

de la unidad vectorial de un procesador. Se realizarı́a entonces, para aquellos casos donde el uso

fuera menor del esperado, un diagnóstico del problema que permitiera lograr una mejora en el

rendimiento de la aplicación.

1.1.

Objetivos

El objetivo principal de este Proyecto Final de Carrera, consiste en determinar el grado de

utilización efectiva de la unidad vectorial de un procesador. Para lograr la consecución del mismo,

se proponen los siguientes objetivos parciales:

Analizar y clasificar un conjunto de aplicaciones numéricas en función del grado de vectorización sobre un compilador determinado.

Determinar las causas del bajo grado de vectorización, a partir de la simulación de las

aplicaciones según el funcionamiento de un producto existente que hace uso de la unidad

vectorial. Las posibles causas serán las siguientes:

• Problemática en el algoritmo base de la aplicación debido a dependencias en el código.

• Problemática en los criterios seguidos a la hora de escribir el código fuente.

• Incapacidad del compilador de detectar que el código es vectorizable.

• Problemas en la microarquitectura.

Proponer cambios hardware/software que faciliten el uso efectivo de la unidad vectorial.

Capı́tulo 2

Estado del arte

La computación paralela es una forma de cómputo consistente en paralelizar la mayor cantidad

de tareas posible con el objetivo de reducir el coste de cómputo de un programa. Tradicionalmente

se utilizaba otro paradigma: la computación serie. Con ella las instrucciones se ejecutaban una

tras otra en la Unidad Central de Procesamiento (CPU). La utilización de este paradigma produce

que, a medida que se incrementa la frecuencia de funcionamiento de la máquina, se disminiuya el

tiempo que tardan en ejecutarse los programas[HP02]. El aumento de la frecuencia, que tuvo su

apogeo durante las dos últimas décadas del siglo XX y principios del XXI, no podı́a ser infinito,

ya que es directamente proporcional al aumento de la energı́a consumida por el procesador y, por

ende, a la generación de calor. Por este motivo, pese a que la computación paralela se empezó a

usar principalmente en el área de la computación de altas prestaciones, este lı́mite en el aumento

de la frecuencia propició que desde la ultima década, el paradigma principal en arquitectura de

computadores sea la computación paralela.[Bar07]

Existen diferentes fuentes de paralelismo disponibles para sacar partido a la computación

paralela. Estas son: Paralelismo de Instrucciones (ILP), Paralelismo de Datos (DLP) y Paralelismo

de Tareas (TLP)[Dı́06]:

ILP: consiste en ejecutar el mayor número de instrucciones posibles en paralelo sin que ello

afecte al correcto flujo del programa. Como ejemplos tenemos las arquitecturas superescalares

y VLIW, del inglés Very Long Instruction Word:

• Superescalares: capaces de introducir en el pipeline de ejecución una o más instrucciones por ciclo, de manera que se pueden estar ejecutando paralelamente varias en un

mismo ciclo.

• VLIW: la arquitectura permite empaquetar varias instrucciones independientes que se

ejecutarán simultáneamente.

Con el objetivo de explotar al máximo esta fuente de paralelismo, existen diferentes técnicas

que se podrı́an clasificar en técnicas de planificación estática y dinámica[Dı́06].

• Técnicas de planificación estática: trabajan sobre el código de la aplicación para

conseguir eliminar todos los obstáculos que impiden que las instrucciones se ejecuten

lo antes posible: desenrollamiento de bucles, reordenamiento de instrucciones...

• Técnicas de planificación dinámica: se aplican sobre el diseño del hardware para

que tengan lugar en tiempo de ejecución: Ejecución Fuera de Orden (OOO).

DLP: consiste en la realización de la misma operación simultáneamente sobre un conjunto

de datos. Para explotar esta técnica de paralelismo, es necesario que el programa tenga

3

4

CAPÍTULO 2. ESTADO DEL ARTE

secciones de código que se puedan adaptar a la aplicación de este concepto. Además, la

arquitectura tiene que proveer de instrucciones especiales, denominadas SIMD, del ingles

Simple Instruction Multiple Data, y de recursos suficientes, como por ejemplo los registros

vectoriales, los cuales puedan contener más de un dato. La estructura de ejecución por

antonomasia sobre la que se pone en práctica este mecanismo, es el bucle. Las estructuras

de datos análogas son los vectores y matrices.

TLP: el concepto radica en la descomposición de la ejecución del programa en diferentes

trazas con instrucciones independientes para ejecutarlas de forma concurrente. Un ejemplo es

la Tecnologı́a Multihilos, SMT, del inglés Simultaneous MultiThreading. Consiste en ejecutar

instrucciones de diferentes hilos independientes en el mismo ciclo de reloj.

En el mercado existen una gran variedad de arquitecturas que implementan recursos para

explotar cualquiera de las fuentes de paralelismo arriba mencionadas. Por ejemplo, la arquitectura

ARM con su extensión SIMD Avanzada, también conocida como NEON o MPE, del inglés Media

Processing Engine, para explotar el paralelismo de instrucciones; Nvidia y su plataforma CUDA,

del inglés Computed Unified Device Architecture, junto con el set de instrucciones PTX, del

inglés Parallel Thread Execution[nvi], que define una máquina virtual y un ISA con el objetivo de

R

explotar la GPU como máquina de ejecución de hilos paralelos de propósito general; Intely

su

R MIC, del inglés Many Integrated Core, sobre la que han desarrollado varios

arquitectura Intel

R Xeon PhiTM Coprocessor, lanzado al mercado en

productos, siendo el último de ellos el Intel

Noviembre de 2012 y descrito en la Sección 2.3 (pág. 8), que explota tanto el paralelismo de

instrucciones como de tareas.

2.1.

Taxonomı́a de Flynn

La taxonomı́a de Flynn consiste en una clasificación de arquitecturas paralelas desarrollada por

Michael J. Flynn en 1966 y expandida en 1972[Fly72]. Desde el punto de vista del programador en

lenguaje ensamblador, las arquitecturas paralelas estarı́an clasificadas según la concurrencia del

procesamiento de secuencias, datos e instrucciones. Esto da como resultado una metodologı́a de

clasificación de las distintas operaciones paralelas disponibles en el procesador. Propuesta como

una aproximación que clarificara los tipos de paralelismo soportados tanto a nivel hardware como

software, en ella se definen las siguientes cuatro arquitecturas[fly]:

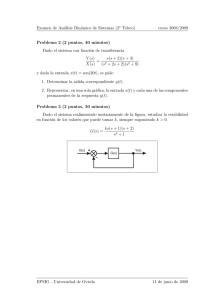

Single Instruction Single Data (SISD): arquitectura secuencial que no explota el paralelismo ni a nivel de instrucciones ni a nivel de datos. Las máquinas tradicionales de un

único procesador secuencial o antiguos mainframes entrarı́an en esta categorización. Ver

Figura 2.1 (pág. 5).

Single Instruction Multiple Data (SIMD): arquitectura que explota el paralelismo durante la ejecución de una única instrucción para realizar operaciones de naturaleza paralela.

Claros ejemplos son los procesadores vectoriales o las GPU. Ver Figura 2.2 (pág. 5).

Multiple instruction Single Data (MISD): múltiples instrucciones operan sobre un

único stream de datos. Es una arquitectura poco común generalmente usada para tolerancia

de fallos, esto es, varios sistemas operan en el mismo stream de datos y obtienen un resultado

que debe ser concorde para todos ellos. Ver Figura 2.3 (pág. 5).

Multiple instruction Multiple Data (MIMD): múltiples procesadores executan simultáneamente diferentes instrucciones sobre diferentes datos. Las arquitecturas VLIW son

un claro ejemplo aparte de sistemas distribuidos o procesadores multicore. Ver Figura 2.4

(pág. 5).

2.2. VECTORIZACIÓN

Figura 2.1: SISD

2.2.

5

Figura 2.2: SIMD

Figura 2.3: MISD

Figura 2.4: MIMD

Vectorización

La vectorización es un proceso de explotación de paralelismo de datos consistente en convertir

un algoritmo de implementación escalar a vectorial. La implementación escalar es aquella en

la que se realiza una única operación simultánea sobre un par de operandos que contienen un

único dato cada uno. La implementación vectorial realizarı́a la misma operación, pero el par de

operandos pasan de contener un único dato a contener una serie de valores. Literalmente, las

escalares operan sobre un escalar y las vectoriales sobre un vector. El bucle siguiente es un claro

ejemplo de candidato a ser vectorizado.

1

2

for ( i =0; i < n ; i ++)

c [ i ] = a [ i ] + b [ i ];

Listado 2.1: Bucle vectorizable

Con el objetivo de poner en práctica esta técnica, es necesario que la arquitectura sobre la que

se va a ejecutar el programa disponga de un repertorio de instrucciones especı́fico, de una unidad

vectorial y de registros vectoriales que puedan contener una serie de datos[LPG13] [SMP11] [Pip12]

[SLA05]. Este repertorio de instrucciones suele ser una extensión sobre las que ya conformen la

ISA con la que se trabaje, denominadas instrucciones SIMD. SIMD también sirve para indicar el

tipo de la máquina. La unidad vectorial contendrá las unidades funcionales necesarias para operar

sobre los registros vectoriales. Finalmente, para generar el código vectorizado, hace falta utilizar

un compilador que sea capaz de reconocer secciones de código potencialmente vectoriales para

generar las instrucciones SIMD que correspondan.

2.2.1.

SIMD

SIMD, como se describió previamente, es un término definido dentro de la taxonomı́a de Flynn

para caracterizar aquellas arquitecturas que explotan el Paralelismo de Datos (DLP). Son arquitecturas que contienen múltiples elementos de procesamiento que permiten realizar la misma

operación sobre varios datos simultáneamente. Esta forma de paralelismo se diferencia de la concurrencia en que es en el mismo momento, y no en momentos diferentes, cuando se realiza de forma

simultánea la misma operación sobre el conjunto de datos que corresponda. Estas instrucciones se

denominan comúnmente como instrucciones SIMD.

Un procesador vectorial, por tanto, es un procesador que puede operar en todos los elementos de

un vector dado con una única instrucción. Esto supone una reducción importante en el número de

instrucciones leı́das, decodificadas y ejecutadas para un mismo programa vectorizado, frente a otro

que no haya sido compilado o escrito usando este recurso. El vector sobre el que se opere, puede a

su vez ser leı́do usando diferentes técnicas que diferencian a unos procesadores vectoriales de otros.

En el caso de ser una arquitectura vectorial memoria-memoria, los operandos son inyectados a la

6

CAPÍTULO 2. ESTADO DEL ARTE

unidad vectorial directamente de memoria, siendo el resultado devuelto a la misma a posteriori. En

el caso de las arquitecturas vectoriales vector-registro, los operandos son depositados en registros

vectoriales que alimentaran a la unidad vectorial, siendo asimismo el resultado depositado en otro

registro vectorial[MS03]. Independientemente de sendos modus operandi descritos, la mejora en

la reducción del número de instrucciones leı́das y decodificadas resulta no ser tal si al final la

instrucción va a tener que esperar a que se lea el vector o porción del vector de memoria. Por

esto, existen diversos esquemas de optimización del rendimiento centrados en reducir el tiempo de

acceso a la memoria:

Hardware y software prefetching: prefetching en términos generales significa traer datos

o instrucciones de memoria antes de que se necesiten. Cuando la aplicación necesita datos que

se han traı́do con el prefetching, puede tomarlos directamente en vez de tener que esperar por

la memoria. Esta técnica puede ser iniciada tanto desde el hardware como desde el software.

Gather-scatter: estas instrucciones permiten un tipo de direccionamiento de memoria propio del tratamiento de vectores. El gather se encargarı́a de indexar la lectura del vector mientras que el scatter se encargarı́a de la escritura. En su funcionamiento intervienen máscaras

que indicarı́an los elementos del vector sobre los que se realizarı́a la operación. Estas podrı́an

ser útiles en caso de haber condiciones en el interior del bucle para acceder a datos de forma

dispersa.

Stripmining: técnica que afronta un problema en la vectorización consistente en que los

registros vectoriales no tienen por qué ser capaces de contener un vector completo definido

en la aplicación. Consistirı́a en romper el bucle de la aplicación que opera sobre el vector en

diferentes bucles: prólogo, principal y epı́logo según conviniera, para tratar un número de

datos <= M V L, donde MVL es la Longitud Máxima de Vector del procesador.

Bancos de memoria: permiten realizar varios load y stores simultáneamente. Los datos

tratados cada vez no tendrı́an por qué ser necesariamente secuenciales.

Repertorio de instrucciones SIMD

El primer uso de instrucciones SIMD fue en los supercomputadores vectoriales a principios de

los 70. Sin embargo, el modo de funcionamiento de entonces era ligeramente distinto al concepto

actual. Anteriormente la instrucción que operaba sobre el vector lo hacı́a sobre un pipeline de

procesadores, cada uno de los cuales operaba únicamente sobre una palabra del vector. En el

concepto moderno, es un procesador el que realiza la operación simultáneamente sobre el vector

completo o una porción del mismo.

A lo largo del tiempo, esta tecnologı́a salto a las máquinas sobremesa, mercado en el que

tuvo gran repercusión y posterior demanda debido a que podı́a soportar aplicaciones tales como

procesamiento de vı́deo y juegos en tiempo real. Es por ello que a lo largo de la historia ha

habido gran variedad de repertorios SIMD fruto de la competencia entre diferentes compañı́as del

momento. Hoy en dı́a no hay computadora de uso general que no haga uso de una arquitectura que

explote el paralelismo de datos a través de la vectorización. A continuación se nombran algunos

de los diferentes repertorios de instrucciones SIMD de la historia:

VIS: Visual Instruction Set. Repertorio desarrollado y lanzado al mercado en 1994 por Sun

Microsystems, adquirida por Oracle Corporation en 2010. La primera version fue implementada en el UltraSPARC en 1995 y por Fujitsu en el SPARC64 GP. Registros de 8, 16 y 32

bits. Hubieron varias versiones posteriores esta: VIS2, VIS2+ y VIS3.

R y lanzado en 1997 en su gama Pentium MMX.

MMX: repertorio desarrollado por Intel

Registros de 64 bits.

2.2. VECTORIZACIÓN

7

3DNow!: extensión al repertorio de la arquitectura x86 desarrollado por AMD. Registros

32 bits para operaciones de punto flotante de simple precisión. El objetivo era mejorar el

ya existente repertorio MMX de Intel de cara a elevar el rendimiento de las aplicaciones

gráficas. En 2010 AMD anunció el fin del mantenimiento y soporte del mismo.

SSE: Streaming SIMD Extensions. Extensión de la arquitectura x86 diseñado por Intel y

lanzado al mercado en 1999 en su serie Pentium III, como respuesta al lanzamiento por parte

de AMD de su extensión 3DNow. Registros de 128 bits.

AltiVec: repertorio diseñado por y propiedad de la siguientes empreas: Apple, aquı́ recibe

el nombre de Velocity Engine; IBM, donde se denomina VMX; Freescale Semiconductor,

propietaria de la marca registrada AltiVec. Registros de 128 bits.

AVX: Advanced Vector Extensions. Extensión al repertorio de la arquitectura x86 destinada

a procesadores Intel y AMD. Registros de 256 bits. Su desarrollo fue propuesto por Intel

en 2008 pero no fue hasta tres años después cuando salió al mercado como caracterı́stica

de la generación de procesadores Sandy Bridge de Intel y Bulldozer de AMD. Posterior a

ella tenemos otra extension denominada AVX2 soportada por Haswell, Broadwell, Skylake

y Cannonlake de Intel y por Excavator de AMD. En Julio de 2013 Intel anunció AVX-512,

última extensión con registros de 512 bits.

Ventajas

Los procesadores vectoriales y por extensión el uso de la vectorización, proporcionan las siguientes ventajas:

Los programas son de menor tamaño al reducir el número de instrucciones que pudiera

requerir un bucle. Ademas, el número de instrucciones ejecutadas también se ve reducido al

poder concentrar un bucle en una única instrucción.

El rendimiento de la aplicación mejora. Se tienen N operaciones independientes que utilizan

la misma unidad funcional, explotando al máximo la localidad espacial de la memoria cache.

Las arquitecturas son escalables: se obtiene un mayor rendimiento cuantos más recursos

hardware haya disponibles.

El consumo de energı́a se reduce. Mientras la instrucción vectorial se está ejecutando, no es

necesario alimentar otras unidades tales como el ROB o el decodificador de instrucciones.

Tomando como ejemplo una aplicación multimedia que cambia el brillo a una imagen, la

vectorización proporciona dos mejoras claras: en primer lugar el conjunto de datos se entiende

como un vector y no como valores individuales. Esto permitirá cargar en un registro todos aquellos

datos que éste pueda albergar, en vez de convertir el programa en una retahı́la carga-opera-guarda

sobre una gran cantidad de pı́xeles individuales. En segundo lugar, la paralelización del trabajo en

una única instrucción es evidente. Cuanto más datos pueda albergar, mayor será el rendimiento.

Inconvenientes

Los procesadores vectoriales comparados con multiprocesadores o procesadores superescalares

podrı́an resultar menos interesantes si lo miramos desde el punto de vista del coste:

Necesitan memoria on-chip rápida y por consiguiente cara.

8

CAPÍTULO 2. ESTADO DEL ARTE

Hay que diseñarlos de forma especı́fica. La unidad vectorial de los procesadores vectoriales

no se compone de elementos prefabricados más allá de las unidades básicas, por tanto pocas

ventas del producto final se traducirı́a en pérdidas debido a su coste de diseño y validación.

Mientras que se conseguı́a una ventaja en el consumo de energı́a al reducir la alimentación

de otras unidades, el consumo por parte de los registros vectoriales podrı́a no mejorar el

balance final de consumo.

Los compiladores, al igual que pueden facilitar la tarea, pueden dificultarla en caso de que

la vectorización del código no se adapte a los requerimientos esperados por el compilador.

Existe entonces una posibilidad real de que haya una importante implicación del ingeniero

tanto a nivel alto como bajo para conseguir vectorizar una aplicación.

No hay un estándar establecido en el proceso. La utilización de un repertorio de instrucciones

SIMD u otro puede dificultar la tarea en caso de compilar la misma aplicación sobre distintas

arquitecturas. Aparte, es posible que el ingeniero tenga que proveer de una implementación

no vectorial de la misma.

No todas las aplicaciones se pueden vectorizar. Por ejemplo, las aplicaciones de análisis de

código, caracterizadas por su fuerte control del flujo de ejecución, son claras candidatas para

no beneficiarse de las ventajas de la vectorización.

2.3.

R Xeon PhiTM Coprocessor

Intel

R Xeon PhiTM es el primer producto basado en la arquitectura Intel

R

El coprocesador Intel

R

MIC que se ha comercializado. Se lanzó al mercado en Noviembre de 2012. La arquitectura Intel

R dentro de un único chip. Esta desMIC se basa en la combinación de muchos núcleos de Intel

tinada a su uso en la Computación de Alto Rendimiento o HPC, del inglés High Performance

Computing, para la ejecución de programas paralelos que se venı́an ejecutando en grandes clústeres1 . Pese a que su objetivo no es sustituir los sistemas ya existentes, es una interesante alternativa

para conseguir buenos resultados de rendimiento de throughput 2 , en entornos donde no haya demasiado espacio para la instalación de múltiples clústeres y donde se impongan limitaciones de

consumo de energı́a. Ademas, un punto clave de la microarquitectura es que esta construida especialmente para proporcionar un entorno de programación similar al entorno de programación del

R XeonTM [intb].

procesador Intel

R Xeon PhiTM puede pasar por un sistema en sı́ mismo, puesto que corre

El coprocesador Intel

una distribución completa del sistema operativo Linux, soporta el modelo x86 de ordenamiento

de memoria y el estándar IEEE 754 de aritmética en punto flotante. Ademas es capaz de ejecutar

aplicaciones escritas en lenguajes de programación propios de la industria del HPC como es el caso

de Fortran, C y C++. Esto permite proporcionar con el producto un rico entorno de desarrollo

que incluye compiladores, numerosas librerı́as de apoyo (siendo de especial importancia aquellas

con soporte multi-thread y operaciones matemáticas para HPC) y herramientas de caracterización

y depurado.

R Xeon, denominado ”host”, a través de un bus PIC

Está conectado a un procesador Intel

Express. Véase Figura 2.6 (pág. 9). Dado que el coprocesador ejecuta de forma autónoma el

sistema operativo Linux, es posible virtualizar una comunicación tcp/ip entre éste y el procesador,

permitiendo al usuario acceder como si fuera un nodo más en la red. Por tanto, cualquier usuario

puede conectarse al mismo a través de una sesión ssh (secure shell) y ejecutar sus aplicaciones.

Además, soporta aplicaciones heterogéneas en las que una parte de la misma se ejecutarı́a en

el host y otra en la propia tarjeta. Ni qué decir tiene que se pueden conectar más de un Xeon

1 Se aplica a los conjuntos de computadoras construidos mediante la utilización de elementos hardware comunes

y que se comportan como si fuesen una única computadora

2 Cantidad de trabajo que un ordenador puede hacer en un periodo de tiempo determinado

R XEON PHITM COPROCESSOR

2.3. INTEL

9

R Xeon PhiTM

Figura 2.5: Intel

Phi en un mismo sistema, pudiéndose establecer entre ellos la comunicación ya sea a través de la

interconexión p2p (peer to peer) o a través de la tarjeta de red del sistema, sin intervención en

ambos casos del host.

Figura 2.6: Esquema general

2.3.1.

Microarquitectura

R Xeon Phi esta formado por más de 50 núcleos de procesamiento,

El coprocesador Intel

memorias cache, controladores de memoria, lógica de cliente PCIe y un anillo de interconexión

bidireccional que proporciona un elevado ancho de banda al sistema. Véase Figura 2.7 (pág. 10).

La ejecución es en orden mientras que la terminación es en desorden. Cada core consta de una L2

privada que mantiene completamente la coherencia con el resto gracias a un directorio de etiquetas

distribuido denominado TD, del inglés Tag Directory. Los controladores de memoria y la lógica

de cliente PCIe proporcionan una interfaz directa con la memoria GDDR5 del coprocesador y el

bus PCIe respectivamente. Ademas, cada core fue diseñado para minimizar el uso de energı́a a la

vez que maximiza el throughput en programas altamente paralelos. Usan un pipeline en orden y

soportan hasta 4 hilos hardware.

10

CAPÍTULO 2. ESTADO DEL ARTE

Figura 2.7: Microarquitectura

VPU

R Xeon PhiTM es la VPU.

Un importante componente de cada núcleo del coprocesador Intel

Véase Figura 2.8 (pág. 10). La VPU cuenta con un repertorio de instrucciones SIMD de 512 bits,

R Initial Many Core Instructions (Intel

R IMCI). Por ello puede

oficialmente conocido como Intel

ejecutar 16 operaciones de simple precisión (SP) u 8 de doble precisión (DP) por ciclo. También

soporta instrucciones Fused Multiply-Add (FMA), que ordenan multiplicar y sumar en la misma

instrucción, y gracias a las cuales se pueden ejecutar 32 instrucciones de simple precisión o 16 de

punto flotante por ciclo. Ni qué decir tiene que proporciona soporte para operaciones con enteros.

Figura 2.8: Vector Processing Unit

Las unidades vectoriales proporcionan una evidente mejora energética en la ejecución de aplicaciones HPC, ya que una única operación codifica una gran cantidad de trabajo, a la vez que no

incurre en el coste adicional de energı́a que supondrı́an las etapas de fetch, decode y retire para

la ejecución de múltiples instrucciones. Sin embargo, hicieron falta varias mejoras para lograr soportar instrucciones SIMD de estas caracterı́sticas. Por ejemplo, se añadió el uso de máscaras a la

VPU para permitir predecir sobre qué datos operar dentro de un registro vectorial. Esto ayudó en

la vectorización de bucles con flujos de ejecución condicionales, mejorando ası́ la eficiencia software

del pipeline. La VPU tambien soporta instrucciones de tipo gather y scatter directamente a través

del hardware. De este modo, para aquellos códigos con patrones de acceso a memoria esporádicos

e irregulares, el uso de este tipo de instrucciones ayuda a mantener el código vectorizado.

Finalmente, la VPU también cuenta con una EMU, del inglés Extended Math Unit, que puede

ejecutar instrucciones trascendentes como son las recı́procas, raı́ces cuadradas y logarı́tmicas. La

EMU funciona calculando aproximaciones polinómicas de estas funciones.

R XEON PHITM COPROCESSOR

2.3. INTEL

11

Interconexión

La interconexión se implementa como un anillo bidireccional. Véase Figura 2.9 (pág. 11). Cada

dirección está compuesta de tres anillos independientes. El primero, que se corresponde con el

más ancho y caro de los tres, es el anillo de datos. Este es de 64 bytes para soportar el requisito

de gran ancho de banda debido a la gran cantidad de cores presentes. El anillo de direcciones es

más estrecho y se utiliza para enviar comandos de lectura/escritura y direcciones de memoria.

Por último, el anillo más estrecho y barato es el anillo de reconocimiento, que envı́a mensajes de

control de flujo y coherencia.

Figura 2.9: Interconexion

Figura 2.10: Directorio de etiquetas

Cuando un core accede a su cache L2 y falla, una solicitud de dirección se envı́a sobre el

anillo de direcciones a los directorios de etiquetas. Véase Figura 2.10 (pág. 11). Las direcciones de

memoria se distribuyen de manera uniforme entre los distintos directorios que hay en el anillo para

añadir la fluidez de tráfico como una caracterı́stica más del mismo. Si el bloque de datos solicitado

se encuentra en la cache L2 de otro core, se dirige una petición a la L2 de ese core sobre el anillo

de direcciones. Finalmente, el bloque de solicitud es posteriormente reenviado sobre el anillo de

datos. Si los datos solicitados no se encuentran en ninguna de las caches, se envı́a la dirección de

memoria desde el directorio de etiqueta hasta el controlador de memoria.

La Figura 2.11 (pág. 12) muestra la distribución de los controladores de memoria en el anillo.

Como se aprecia, se intercalan de forma simétrica alrededor del él. La asignación de los directorios

de etiquetas a los controladores de memoria se realiza de forma todos-a-todos. Las direcciones

se distribuyen uniformemente a través de todos los controladores, eliminando de este modo los

hotspots y proporcionando un patrón de acceso uniforme esencial para un uso efectivo del ancho

de banda.

Volviendo al modo de funcionamiento, durante un acceso de memoria, cada vez que se produce

un error en el nivel L2 de cache en un core, éste genera una petición de dirección en el anillo

12

CAPÍTULO 2. ESTADO DEL ARTE

Figura 2.11: Controladores de memoria

de direcciones y consulta a los directorios de etiquetas. Si los datos no se encuentran en estos

directorios, el core genera otra solicitud de dirección y solicita los datos a la memoria. Una vez

que el controlador recibe el bloque de datos desde la memoria, se entrega al core a través del

anillo de datos. En todo el proceso los elementos trasmitidos a los anillos son: un bloque de datos,

dos solicitudes de dirección junto con dos mensajes de confirmación. Debido a que los anillos de

datos son los más caros y están diseñados para soportar el ancho de banda requerido, es necesario

incrementar el número de anillos de dirección y reconocimiento, más baratos en comparación, en

un factor de dos para soportar las necesidades de ancho de banda causadas por el elevado número

de peticiones sobre los anillos.

Caches

R MIC invierte en mayor medida tanto en caches L1 como L2 en compaLa arquitectura Intel

R Xeon PhiTM implementa un subsistema

ración con las arquitecturas GPU. El coprocesador Intel

de memoria en el que cada core está equipado con una cache de instrucciones L1 de 32KB, una

cache de datos L1 de 32KB y una cache L2 unificada de 512KB. Son totalmente coherentes e

implementan el modelo de orden de memoria x86. Las caches L1 y L2 proporcionan un ancho de

banda agregado que es entre 15 y 7 veces, respectivamente, más rápido que el ancho de banda de

la memoria principal. Por lo tanto, el uso efectivo de esta jerarquı́a es clave para lograr el máximo

rendimiento en el coprocesador. Además de mejorar el ancho de banda, son también más eficientes

que la memoria principal en cuanto al uso de energı́a para el suministro de datos al core. En la era

de la computación exascale 3 , las caches jugarán un papel crucial a la hora de conseguir maximizar

el rendimiento bajo estrictas restricciones de potencia.

R

Imágenes cortesı́a de Intel.

3 La

computacion exascale se refiere a los sistemas de computacion capaces de alcanzar un exaFLOPS.

R ADVANCED VECTOR EXTENSIONS

2.4. INTEL

2.4.

13

R Advanced Vector Extensions

Intel

AVX, del inglés Advanced Vector Extensions engloba, como veı́amos en la Sección 2.2.1 (pág. 6),

el conjunto de extensiones sobre la arquitectura del repertorio de instrucciones x86, propuestas

por primera vez por Intel en Marzo de 2008 tanto para procesadores de Intel como de AMD. El

primer producto en soportarlo fue el procesador Sandy Bridge de Intel en el primer cuarto de

2011, seguido por el procesador Bulldozer de AMD en el tercer cuarto del mismo año.

2.4.1.

R Advanced Vector Extensions 1

Intel

R Advanced Vector Extensions 1 (AVX) mejoraban las extensiones SSE

Las extensiones Intel

mediante el incremento del ancho del banco de registros SIMD de 128 bits a 256 bits. El nombre

de los registros, XMM0-XMM7, se cambió en consecuencia de YMM0-YMM7 (en el caso de x8664, YMM0-YMM15). Sin embargo, en los procesadores con soporte AVX, las instrucciones de la

extensión SSE podı́an ser usadas para operar en los 128 bits menos significativos de los registros

YMM. Entonces podı́a seguir usándose la nomenclatura XMM0-XMM7.

AVX introdujo además un formato de instrucción SIMD de tres operandos donde el registro

de destino podı́a ser distinto a los dos registros fuente. Por ejemplo, una instrucción SSE usando

la forma convencional a = a + b, podı́a ahora utilizar el método de tres operandos c = a + b,

impidiendo que se destruyera la información almacenada en alguno de ellos como ocurrı́a hasta

el momento. Este formato estaba limitado a las instrucciones que utilizan los registros YMM, no

incluyendo por tanto instrucciones con registros de propósito general (por ejemplo EAX).

2.4.2.

R Advanced Vector Extensions 2

Intel

R Advanced Vector Extensions 2 (AVX2) mejoraban el set de extensiones

Las extensiones Intel

R Haswell. La compañı́a

AVX, y fueron introducidas por primera vez en la microarquitectura Intel

amplió por tanto el juego AVX con nuevas instrucciones que funcionaban también sobre números

naturales, ampliando casi la totalidad del conjunto SSE de 128 bits a 256 bits. El formato no

destructivo de tres operandos estuvo ahora también disponible para instrucciones a nivel de bits

y multiplicación de propósito general y para instrucciones FMA (Fused Multiply-Accumulate).

Finalmente, esta nueva ampliación permitió realizar instrucciones gather, lo que significarı́a la

posibilidad de acceder a la vez a varias posiciones no contiguas en memoria, aumentando considerablemente las capacidades de procesado vectorial de la arquitectura x86-64.

2.4.3.

R Advanced Vector Extensions 512

Intel

R Advanced Vector Extensions 512, AVX-512, son las extensiones a 512 bits de las insIntel

trucciones SIMD recogidas en las Advanced Vector Extensions de 256 bits. Fueron propuestas

R Xeon PhiTM denominado

por Intel en Julio de 2013 para ser incluidas en el coprocesador Intel

Knights Landing que se espera lanzar al mercado en el año 2015[inta]. No todas las extensiones están destinadas a ser soportadas por todos los procesadores que las implementen. Sólo la

extensión del núcleo AVX-512F (AVX-512 Foundation) se requiere para todas las implementaciones. Atendiendo al repertorio de instrucciones y a las principales caracterı́sticas de AVX-512, las

extensiones se clasifican del siguiente modo:

AVX-512 Foundation: expande la mayorı́a de instrucciones AVX de 32 y 64 bits con el

esquema de codificación EVEX para soportar los registros de 512 bits, las operaciones con

14

CAPÍTULO 2. ESTADO DEL ARTE

máscaras, la difusión de parámetros y las excepciones de control y redondeo empotradas.

AVX-512 Conflict Detection Instructions (CDI): añade detección de conflictos eficiente para permitir que más bucles puedan ser vectorizados.

AVX-512 Exponential and Reciprocal Instructions (ERI): operaciones exponenciales

y recı́procas diseñadas para ayudar en la implementación de operaciones trascendentes, como

por ejemplo la función de logaritmo.

AVX-512 Prefetch Instructions (PFI): soporte para prefetches.

En cuanto a las caracterı́sticas técnicas, se resumen en los siguientes puntos:

32 registros vectoriales de 512 bits de ancho bajo la nomenclatura ZMM0-ZMM31.

8 registros dedicados a las máscaras, lo cual es de especial trascendencia para las instrucciones

gather y scatter.

Operaciones de 512 bits sobre datos empaquetados enteros y de punto flotante.

Los programas podrán entonces empaquetar en los nuevos registros de 512 bits cualquiera de

las siguientes combinaciones de datos: 8 datos en punto flotante de precisión doble, o 16 datos en

punto flotante de precisión simple, u 8 enteros de 64 bits o 16 enteros de 32 bits. Esto permitirá el

procesamiento del doble de elementos que el AVX/AVX2 con una sola instrucción y cuatro veces

el de SSE.

R AVX-512 ofrece un nivel de compatibilidad con AVX

Es interesante resaltar que Intel

muchı́simo mayor que las transiciones anteriores sobre el ancho de las operaciones. A diferencia de

lo que ocurre con SSE y AVX, que no se pueden mezclar sin penalizaciones en el rendimiento, la

mezcla de instrucciones AVX y AVX-512 es posible sin penalización alguna. Los registros YMM0YMM15 de AVX se mapean en los registros ZMM0–ZMM15 de AVX-512 del mismo modo que se

mapeaban los registros SSE sobre AVX. Por lo tanto, en procesadores que soporten AVX-512, las

instrucciones AVX y AVX2 operarán en los 128 o 256 bits inferiores de los primeros 16 registros

ZMM.

Capı́tulo 3

Metodologı́a

Las ideas que surgieron a la hora de definir el anteproyecto del presente Proyecto Final de

Carrera lo describı́an claramente como un trabajo con una fuerte carga de análisis. Comprendı́a

desde el análisis de todas y cada una de las herramientas a utilizar, hasta el análisis de cada resultado, cada gráfica elaborada, cada bloque básico implicado y cada lı́nea de código que supusiera

un objeto de interés sobre el que adentrarse. Por este motivo no se aplicó una estrategia especı́ficamente etiquetada que seria propia de un trabajo vinculado a la rama de ingenierı́a del software.

Ciertamente, parte de este trabajo consistı́a en desarrollar un simulador sobre el que ejecutar las

aplicaciones, con el objetivo de obtener más estadı́sticas aparte de aquellas conseguidas gracias a

R Sin embargo, incluso el tomar la

las herramientas ya disponibles para los ingenieros de Intel.

decisión de incorporar el desarrollo de este simulador como una extensión de otro ya existente,

supuso un fuerte trabajo de análisis para tratar de reciclar la mayor cantidad de información ya

disponible. Esta información se encontraba almacenada, en su mayor parte, sobre una gran variedad de estructuras y clases que evitaron, ya no solo no reinventar la rueda, sino también impedir

sobrecargar al simulador con operaciones y tareas que eran necesarias y que por supuesto ya se

estaban realizando.

En este capı́tulo, se describirá la forma de trabajo, es decir aquellas actividades que supusieron

una importante parte para la consecución del trabajo, cómo se distribuyeron todas las tareas a

realizar y el tipo de metodologı́a usada cuando se procedió al desarrollo de la nueva extensión del

simulador.

3.1.

Plan de trabajo

Al plan de trabajo diseñado inicialmente y presentado en el anteproyecto se le aplicaron modificaciones sin que ello repercutiese en el computo total de horas. A continuación se presenta la

planificación final y las justificaciones sobre los cambios en el caso de haberlos.

Fase 1: Selección y caracterización de benchmarks

1. Selección del conjunto de benchmarks sobre los que realizar el estudio a partir de los disponibles, como NPB, Polyhedron, PARSEC, etc.

2. Compilar las aplicaciones de los benchmarks para la arquitectura x86 con la extensión AVX512 para la obtención de una caracterización inicial. Utilizando los compiladores disponibles,

15

16

CAPÍTULO 3. METODOLOGÍA

como ICC e IFORT, se realiza la compilación del conjunto de aplicaciones seleccionadas utilizando aquellas opciones que permitan realizar optimizaciones y vectorización del código.

Implica un pequeño análisis mediante el parsing del informe generado, para tener una aproximación inicial al comportamiento de cada aplicación.

Esta fase se redujo a la selección y posterior caracterización de las aplicaciones. El motivo por

el que no se realizó una criba inicial radica en que al principio, sin más datos que los disponibles

estáticamente con el informe del compilador, la mera descripción de la aplicación no parecı́a

suficiente para descartar unas u otras. Era más interesante quedarnos con todas las disponibles

y, a partir de diferentes estadı́sticas, tomar decisiones sobre cuáles analizar según las soluciones

software o hardware a aplicar.

Fase 2: Recopilación y análisis de información sobre la ejecución vectorial de los

programas de prueba

1. Determinación del grado de vectorización de los programas: Usando el emulador Pin/SDE,

se obtiene el número de instrucciones ejecutado por cada programa y se determina el grado

de vectorización de los mismos.

2. Recopilación de información sobre la jerarquı́a de memoria: Usando el emulador CMP$im,

se obtiene la tasa de fallos de los diferentes niveles de la jerarquı́a de memoria para cada

uno de los programas de prueba.

3. Determinación del grado de utilización de la unidad vectorial: En este apartado se desaR Xeon PhiTM

rrollará un núcleo sencillo basado en la arquitectura del coprocesador Intel

sobre el simulador CMP$im, que permita obtener datos estadı́sticos para ası́ determinar el

grado de utilización de la unidad vectorial.

La única modificación planteada en esta fase consistió en realizar el desarrollo del simulador de

un core con arquitectura vectorial embebido dentro del simulador de cache CMP$im. El motivo

radica en que el simulador de cache proporciona mucha información de interés que puede utilizarse

para la simulación de la arquitectura. Además, contiene multitud de estructuras y clases que se

pueden utilizar a la vez que se introduce el código sobre el esqueleto correspondiente a la simulación

de cache.

En primer lugar se llevarı́a a cabo una exhaustiva fase de análisis sobre CMP$im, para conocer

en profundidad tanto la configuración de ficheros del simulador, como las estructuras y clases

usados, aparte del funcionamiento especı́fico de la simulación de la cache. Los objetivos principales

eran reutilizar estructuras, esquemas y clases ya presentes, saber de qué modo introducir el código