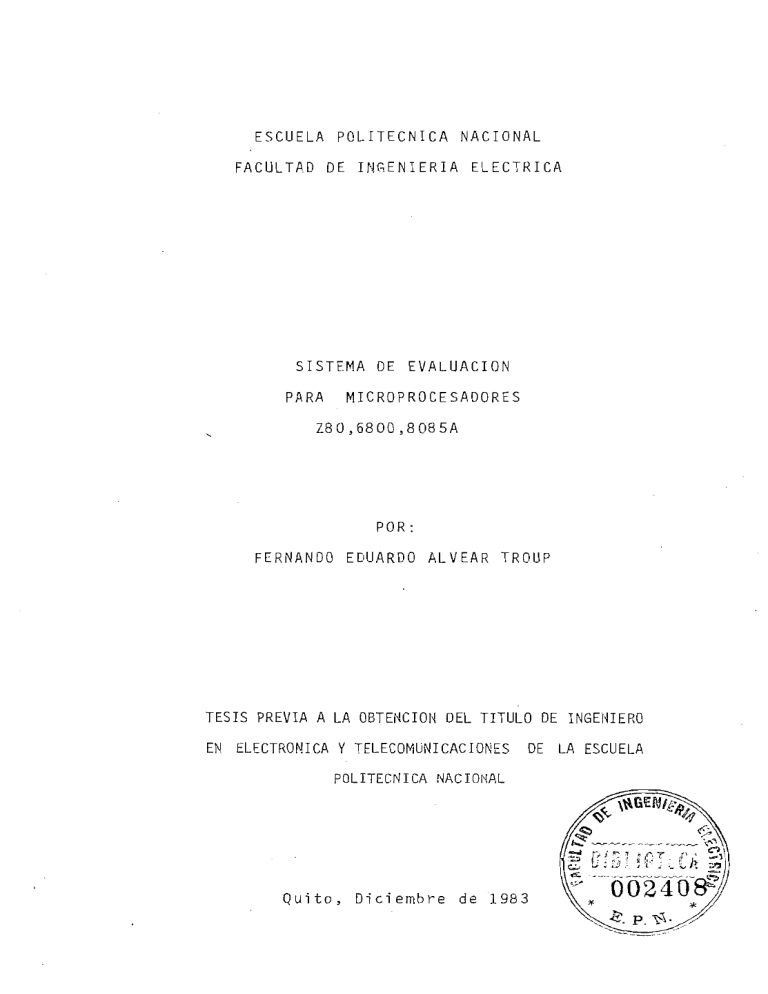

ESCUELA POLITÉCNICA

FACULTAD DE INGENIERÍA

SISTEMA

PARA

NACIONAL

ELÉCTRICA

DE E V A L U A C I Ó N

MICROPROCESADORES

Z80,6800,8085A

POR:

FERNANDO EDUARDO A L V E A R TROUP

TESIS PREVIA A LA OBTENCIÓN DEL TITULO DE INGENIERO

EN ELECTRÓNICA Y TELECOMUNICACIONES DE LA ESCUELA

POLITÉCNICA NACIONAL

Q u i t o , D i c i e m b r e d e 1983

Certifico que el presente

trabajo ha sido elaborado

en su totalidad por el s£

ñor: Fernando E. Alvear.

:NG.

ALFONSO ESPINOSA

Director de Tesis

R.

D E D I C A T O R I A

A mis

padres.

ÍNDICE

I.

INTRODUCCIÓN

I

II.

DISEÑO

*

2.1.

ESPECIFICACIONES

1

2.2.

DISEÑO DEL HARDWARE

2

2.2-1. DESCRIPCIÓN

GENERAL

2

2. 2-71.a. DIAGRAMA DE BLOQUES

2.2-l.b. DESCRIPCIÓN

2

FUNCIONAL

•

2.3.

UNIDADES CENTRALES DE PROCESO

2.4.

CIRCUITOS

3

6

DE ENTRADA Y SALIDA

(I/O;

9

2.4-1. INGRESO DE DATOS Y DIRECCIONES

9

.2.4-^2. GENERACIÓN DE SEÑALES DESDE EL TECLADO

9

2.4-3.

INDICADORES DE DATOS Y DIRECCIONES

11

2.4^4.

INDICADORES

12

DE STATUS

2.5.

MEMORIA

13

2.6.

BUFFERS

16

2.6-1. BUFFERS

DE DATOS Y DIRECCIONES DE LOS

uPs

2.6-2. BUFFERS

16

DE DATOS Y DIRECCIONES DE TECLA-

DO

18

2.6-3. BUFFERS DE INTERCONECCION

2.7.

2.7-1.

20

CIRCUITOS DE CONTROL

21

SEÑALES BÁSICAS

2.7-2. INTERRUPCIONES

'

21

'

22

2 . 7 r-3 . CONTROL DE I/O

24

2.7-4. CONTROL DE TRANSFERENCIA DE DATOS CON

LOS UPS EN ALTA IMPEDANCIA

2.7-4.a. INICIALIZACION

DEL SISTEMA

PROGRAMACIÓN

26

PARA LA

'

2 . 7-4.b . INGRESO DE DATOS

2.7-4.C. LECTURA DE LOCALIDADES DE MEMORIA

26

29

33

2.7-r5. SELECCIÓN DE LOS uPs

2.7-6.

CONTROL

38

DE TRANSFERENCIA DE DATOS BAJO

COMANDO DE LOS uPs

42

2 . 7- 7 . CONTROL DE INICIALIZACION (R13SUT)

2.'8.

2.9.

P R O G R A M A D O R DE

•

2.10.

FUENTES DE

EPROMS

45

48

PODER

50

DISEÑO DEL SOFTWARE

52

2 . 10-7 1 .DIAGRAMAS DE FLUJO

52

2.10-2.PROGRAMAS

60

III.

OPERACIÓN DEL SISTEMA

61

3.1.

DESCRIPCIÓN DEL PANEL

61

3.1-1. DESCRIPCIÓN

DE LOS TECLADOS

61

3.1-r2. INDICADORES

DE STATUS

66

3.1-2.a. INDICADORES DE STATUS DEL MONITOR

66

3.1-2.b. INDICADORES DE STATUS

66

DE LOS uPs

3.1-2.C. INDICADORES DE P R O G R A M A C I Ó N

DE EPROMS

67

3.2.

ENCENDIDO, POR Y REUBICACION DE MEMORIA

67

3.3.

PROCESOS DE OPERACIÓN

68

INTRODUCCIÓN

DEL MONITORES

PROGRAMA DEL USUARIO

\2

USO DE LOS

68

3.3-1

3.3-2.a. 280

72

3.3-2t b. 8085A

85

3.3-2.c. 6800

86

3.4.

USO DEL SISTEMA

CON CIRCUITOS

EXTERNOS

86

3.4-1. PERIFÉRICOS EXTERNOS

90

3.4-2.

uPs EXTERNOS

93

CONSTRUCCIÓN

94

IV.

4.1.

DISTRIBUCIÓN

GENERAL

4.2.

DISTRIBUCIÓN

DE ELEMENTOS EN LAS

TAS

94

TARJE96

72

*

V.

EXPERIMENTACIÓN Y CONCLUSIÓN

122

VI.

BIBLIOGRAFÍA

124

VII.

APÉNDICES

125

I N T R O D U C C I Ó N

"El microprocesador es uno de los desarrollos

tecnológicos más excitantes

desde que apareció el -transij^

tor en 1948. Se ha predicho que este artefacto no sólo

revolucionará el campo de la electrónica digital, sino

que tendrá una gran influencia sobre el modo de vida de

las generaciones presente y futura".

cro comp u ters and Microprocessors:

and Applications,"

(Traducido de "Mi-

Hardware, Software

Prentice-Hall, Inc. 1976 .JOHN L.-=•

HILBURN- PAUL M. JULICH.)

A esta fecha, siete años después de la publicacación del libro mencionado, la cita anterior ha sido

completamente comprobada.

Dentro de la amplia gama de microprocesadores

existentes, son tres los que pueden considerarse como

los que más difusión han tenido y que han servido de base para el desarrollo de otros mas sofisticados y eficaces; éstos son: el 8085A de INTEL CORPORATION, el 6800

de MOTOROLA INC. y el Z80 de 2ILOG INC.

La mayoría de los fabricantes de microprocesado

res, sino todos/ fabrican también pequeños sistemas .llamados de "evaluación", cuyo principal objetivo es el de

proporcionar un medio de familiarización con el micropro_

cesador pertinente.

El lenguage de programación de es-

tos sistemas es el hexadecimal, salvo alguno que otro

caso en el que existe un ensamblador de un paso.

Estos

sistemas soportan solamente un microprocesador, haciendo

que la familiarización

con varios diferentes sea un pro-

blema básicamente económico.

Considerando ésto, se decidió

que la presente

tesis incorpore los tres micros mencionados anteriormente en un solo sistema.

Además de ésto, se incorporará

un pequeño programador de EPROMS bajo el control del Z80.

Al describir las diferentes partes del circuito

se hará referencia a las coordenadas en el diagrama general del mismo.

paréntesis.

Estas coordenadas están encerradas entre

Como ejemplo: 280, (2D); al localizar el

integrado respectivo en el diagrama se encontrará junto

a él un código alfa-numérico que indica su localización

en la tarjeta respectiva del aparato.

Así, para el ejem

pío anterior, se encontrará junto al Z80 elcódigo 3TD , que

indica que el circuito integrado está localizado en la

tarjeta 3, columna T, fila D.

En algunos casos, los in-

tegrados se encuentran compartiendo dos filas y/o dos

columnas, en este caso habrán mas de dos letras después

del numero de la tarjeta.

Al analizar la parte circuital de la Tesis, se

podrá ver que muchos circuitos pueden eliminarse, si se

incorpora su función en los programas de monitor.

Sin

embargo, es necesario señalar que al momento de realizar

la Tesis, no se tenía acceso a ningún equipo que facilitara esta tarea, de ahí que se tuvo que recurrir a im-

III

plementar circuitalmente muchas funciones.

II.

2.1.

DISEÑO

ESPECIFICACIONES

Como se menciono en la introducción, el sistema de evaluación de microprocesadores, acerca del cual

trata esta tesis, llevará incorporados los microprocesadores Z80 de ZILOG INC., 6800 de MOTOROLLA INC, y 8085A de INTEL CORPORATION.

Para facilitar la familiarización del'usuario

con cada uno de estos uPsl/, el sistema tendrá

un progra-

ma monitor por cada uno que se encargará de realizar las

funciones correspondientes a la evaluación de programas

y registros de los úPs.

Los programas monitores estarán en memoria novolátil (EPROM) , mientras g_ue datos y programas del usuario se almacenarán en RAM.

Por medio de un teclado el usuario ingresará datos y/o instrucciones al sistema, el c.ual a su vez se

comunicará con el usuario mediante un grupo de indicadores visuales (displays) y LEDS.

Para poder expandir la memoria del sistema, así

como poder utilizar la familia de circuitos integrados

periféricos de cada uP, se deberá poder tener acceso,

desde el exterior^ a los buses de datos y direcciones así

como señales de control de los .UP s .

2.2.

DISEÑO DEL HARDWARE

2.2rl.

DESCRIPCIÓN GENERAL

O'

Q

2

<

e:

<

u

3

2:

4-

uJ

•z.

c/)

uJ

c

FUNCK

2.2-1.a. DIAGRAMA DE BLOQUES

/.

,

\

S

1

0

<

UJ

Q

_J u

/

•:

0

<

0

c

n

^

u

0.

_j

6

§

O O

* •?

.

m

a

2

O

c;

o.

LU

J

;

_j

J

t-

'

2

•z.

u

u

c:

CL

•

>•

/•«

c:

ÜJ

O

Q

Q

<

0

ce

1U)

<

LL

Q

5

<

O

UJ

t±r

o

0

a

5

<

<

cr

o

¿

0

g

v

8

-

UJ

<

-J

0

t2

0

2

U

a

c/i

c;

u

p

LU

Q

c

K-

0

o

/

'

Q

„

u

Q

>

to

ir

LU

O

LU

u.

LL

ul

UJ

o

ra

ÜJ

~

O

£

S

u

u

UJ

Q

^

£

/\

0

ui

c:

;

5 E

Q

—

Q

Q

\

u

c

<

c

5

h

CENTRALES

~

O

a

.

<

*

"

to

«

UJ

c;

uJ

c3

o

/)

JJ

J

D

~

UJ

tr

P:

Q

"Q

o

tu

S

LU

Q

U)

P

°

LQ

<

-1

^

í!

2.2^1.b. DESCRIPCIÓN FUNCIONAL

TECLADO DE DATOS Y MONITOR

Estos contienen 19 teclas cada uno, teniendo

el de DATOS 16 teclas para generar caracteres aexadecimales (los datos propiamente dichos) y 3 de control que se

suman a las 19 teclas del MONITOR para un total de 22

teclas para operación y control del sistema.

DECODIPICñDORES

DEL TECLADO.

Son decodificadores-registros para 20 teclas

y se encargan de monitorear el teclado y presentar las

señales y palabras de control, en forma binaria, al

bloque de control, y los caracteres hexadecimales a los

registros de direcciones y datos.

REGISTROS DE DIRECCIONES Y DATOS

El registro de direcciones se conecta a través

de un buffer de 16 bits co'n el' bus de direcciones del

sistema.

Contiene contadores UP/DOWN para así leer lo-

calidades sucesivas de memoria, ya sea hacia arriba,

(incremento de direcciones) o hacia abajo (decremento

de direcciones). •

El registro de datos conecta a éstos al bus de

los indicadores de datos a través de dos buffers de 8 bits

cada uno.

Estos constan de 4 indicadores hexadecimales

cada uno.

Los indicadores de DIRECCIONES se encienden

cuando el sistema está en el modo de programación o. los

microprocesadores están en estado de alta impedancia.

En los indicadores de DATOS , los dos más significativos

se encienden o apagan automáticamente según sea requerido

durante las diversas operaciones del sistema mientras

que los

menos significativos siempre están encendidos.

BUFPERS.

Estos unen a los microprocesadores con los buses de direcciones y datos del sistema y con los registros que guardan la información proveniente de los teclados.

También están considerados dentro de los BUFPERS

los circuitos integrados que sirven para la lectura y es

critura, por parte de los microprocesadores, de datos re

queridos durante su operación.

MEMORIA.

Esta tiene dos áreas:

RAM.

una de EPROM y otra de

En el área de BPROM se encuentran los programas

monitores del sistema.

En el

área de RAM se almacenan

tanto los datos intermedios de los programas monitores

como los programas del usuario.

CONTROL DE PROGRAMACIÓN/LECTURA DE EPROMS.

Este bloque contiene la circultería necesaria

para la programac-ión o lectura de las siguientes EPROMS:

2716

(1K x 8 bytes) y las dos versiones de la 2758 (1K x 8

bytes).

Estas tres memorias requieren una sola fuente

de + 5V para su funcionamiento normal y una adicional

de + 25 V para su programación.

INDICADORES DE STATUS.

Son un conjunto de dio.dos emisores de luz

(LEDs)

que señalan al usuario la operación en proceso y el status delsistema.

UNIDADES CENTRALES DE PROCESO.

En este bloque están comprendidos los tres microprocesadores residentes del sistema: 280, 8085A y

6800.

Además, se incluyen los circuitos básicos necesarios para el funcionamiento de dichos microprocesadores

como la generación de las señales de reloj respectivas

y un registro/buffer para el bus de datos del 8085A.

CONTROL

Contiene todos los circuitos necesarios para

el control total de la .operación del sistema por el usua

rio

y ciertos procesos-por los microprecesadores.

2.3.

UNIDADES CENTRALES DE PROCESO

Z80/8085A/6800/OTROS

POSIBLES

Los tres microprocesadores residentes en el sistema son de 8 bits y tienen capacidad para direcciónar

directamente 64K bytes de memoria.

El Z80 y el 8085A

direccionan separadamente memoria y periféricos mientras

que el 6800 no establece ninguna diferencia entre ambos.

En cuanto a los circuitos adicionales necesarios

para su funcionamiento, el Z80 y el 6800 necesitan de generación externa de los pulsos de reloj mientras que el

8085A necesita de un registro de 3-estados para obtener

los 8 bits menos significativos de las direcciones, a

partir del bus de datos por ser los datos y los 8 bits

menos

significativos de las direcciones multiplexados

en este bus.

Estos microprocesadores, en cuanto a los buses

de datos y direcciones se refiere, están conectados en

paralelo y separados del resto del sistema por buffers

de 3-estados, cuyo objetivo es colocar la meno£ carga

posible a los uPs.

Algunas señales de control están también en paralelo , como son las de escritura

(WR) y lectura

(RD).

Cabe señalar aquí que el 280 y el 8085A tienen estas señales

7

separadas, a diferencia del 6800 que tiene una sola señal

para ambos propósitos (R/W).

Además, el Z80 tiene una s_e

nal para procesos de memoria (MREQ) y una para procesos

de I/O (IORQ) , mientras que el 8085A tiene uno solo 'para

ambos propósitos

(IO/M) y el 6800 no tiene ninguno.

El manejo tanto de memoria como periféricos fue

diseñado alrededor de las señales de control del Z80 y

por tanto fue necesario generar las respectivas señales

en base a las existentes en los ü;.Ps restantes.

Para el 8085A

tamente a MREQ

(2B), IO/M está conectado direc-

del Z80 (2D) ya que para proceso.s; de

memoria las dos líneas funcionan igual.

I/O, IO/M

dos

Para procesos

se conecta a través de un inversor de 3-esta-

(2H) con IORQ del 280 7

este inver.sor se habilita

solamente cuando se selecciona el 8085A.

Para el 6800 (2F), antes de obtener estas señalas separadas es necesario una señal de habilitación para

estas.

Dicha señal se logra haciendo una función AND en-

tre la señal VMA del 6800, a través de los inversores

(II), y MEM CLK del generador de fases de reloj MC6875L

(4J), función que se logra con la compuerta AND de colee

tor abierto

sores

( 1IH).

La función que realizan los inver-

(II) se explicara mas adelante.

Para la señal rOT se hace un AND de R/W con la

señal anterior

( R/W. VM. MEM CL'.K) , (3H) , y luego se in-

vierte

ésta (3H), conectándose luego la señal obtenida

a RD en el Z80 y 8085A.

Para la señal WR , R/W pasa

sor de colector abierto

a través de un inver-

(2H) y se hace el sincronismo con

la señal especial de habilitación como en el caso anterior, obteniéndose R/W • VMA ' MEMCLK mediante el AND y el

inversor respectivo

( 3H), siendo luego conectado a WR

en los otros uPs.

La señal MREQ se obtiene a partir de la señal

BA del 6800 y una señal de habilitación proveniente del

biestable ( 9F) ,

pin 9, la cual está en 1L mientras

esté seleccionado el 6800.

Estas dos señales, a través

del circuito formado por los ÑOR (lj), el ÑOR (3K) y el

transistor conectado a la salida de éste, generan la señal MREQ, la cual está siempre presente ( no es un pulso)

mientras esté seleccionado el 6800.

La habilitación de

memoria o periféricos depende entonces solo de RD o WR.

Para IORQ,

solo se invierte VMA mediante el in

versor de colector abierto

( 2H).

Esta señal, sin embar-

go, hace un OR (2H) con la señal proveniente de la compuerta AND (1H) que realiza la función lógica RD • WR

sincronizando de esta manera IORQ con -RD o WR.

Esta com-'

puerta OR (2H) es común a los 2 uPs.

En cuanto a - l a s señales de reloj

necesarias pa-

ra los uPs, el 8085A necesita de un cristal que se conecta, directamente a dos terminales que tiene para este

propósito; la frecuencia de oscilación del cristal utilizado es 4 MHz y esta frecuencia se obtiene dividida por

2, en un terminal dedicado del mismo 8085A.

Este reloj

es de niveles TTL y en este caso es de aproximadamente

4V. Pasando esta señal de reloj a través de una compuerta AND (IB) se obtiene una señal de reloj que se usa para diversos propósitos en el resto del sistema, obteniendo además un "FAN-OUT" de una compuerta TTL normal. Esta señal pasa también por una compuerta de colector

abier

to (IB) y se conecta luego a la entrada CLK del Z80. La

resistencia recomendada por el fabricante, que debe ser

conectada a la salida de la compuerta de colector abierto que maneja a la entrada CLK, es de 330 J * - , para cumplir las características AC y DC de dicha entrada.

•Para el 6800 se utilizo un circuito integrado

dedicado para generar las críticas fases no superpuestas

de reloj que éste necesita. Este circuito integrado es

el MC6875L (4J), y la frecuencia que genera para este

caso, está entre 900 KHZ y 1 MHZ.

2.4.

CIRCUITOS DE ENTRADA Y SALIDA

2.4-1.

INGRESO DE DATOS

Y

(I/O)

DIRECCIONES

El principal circuito de este grupo es el que

se encarga de la decodificacion de los teclados y de la

generación de caracteres hexadecimales y señales básicas

de control.

Para decodificar los dos teclados de, 19 teclas

cada uno, se utilizan dos circuitos integrados 74C923

cada uno con capacidad para manejar 20 teclas arregladas

en una matriz de 4 x 5. El primero de ellos (7L) se encarga de los caracteres hexadecimales y tres señales de

control; el segundo ( 1 3 J) maneja el resto de las señales de control, que con las tres anteriores suman un total de 22. Los caracteres hexadecimales, en el caso de que

sean direcciones, son cargados en contadores "UP/DOWN" pro

gramables ( 7 K, 7K, 8K, 9K) componiendo así los 16 bits

para direccionar las diferentes localidades de memoria.

En el caso de que sean datos, son cargados en dos registros de 4 bits 74C175 (10K,11K) obteniéndose así los 8

bits de datos.

2.4-2.

GENERACIÓN

Estas

DE SEÑALES DESDE EL

TECLADO.

señales se obtienen del decodificador

10

74154 (15J) y del decodificador 74L3155 (8L) .

cador de teclado

(13J)

El decofi-

comanda al decodificador (15J)

y

la mitad del decodificador (8L), mientras que el otro deco_

dificador de teclado

codificador

(8L).

(7L) comanda a la otra mitad del de-

Los dos bits menos significativos de

los decodificadores de teclado

(7L) y (13J) son comunes

a ambas mitades del decodificador

(8L) y llegan a través

de un circuito AND-OR-INVERT 74LS51 (9L)que hace las veces de un multiplexer

doble 2 a 1.

La habilitación de cada mitad del decodificador

(8L) se logra mediante dos señales para cada mitad; una

de ellas

(la entrada C) proviene del bit mas significati-

vo de cada decodificador de teclado mientras que la otra

(la entrada G) proviene de las señales DAdecodificadores de teclado

de los mismos

(7L) y (13J) , previamente tra

tados por el circuito formado por los biestables (12L) y

(13L)-(14L).

Estos circuitos adicionales fueron necesa-

rios debido a la forma en que trabajan los

74C923 al

momento de señalar la presencia de un dato válido en sus

salidas.

Esto es, la señal DA indica una entrada válida

del teclado y está presente antes de que se estabilize el

dato correspondiente a la salida (máximo 150 ns antes).

Esta señal, al ser aplicada directamente a la entrada

de habilitación respectiva del decodificador (8L) generaría dos pulsos diferentes a la salida en vez de uno solo

como es lo deseado.

Esto se debe a que como la señal DA

está presente antes que el dato, se habilita la mitad

respectiva del decodificador (8L) con el dato presente

11

al momento de activarse DA y luego cambia su salida de

acuerdo al dato deseado.

Se corrige ésto dando una demo-

ra a la señal DA mediante el circuito de biestables mencionado -anteriormente.

La demora es el tiempo equivalen-

te a medio ciclo de la señal de reloj aplicada a la entra.

da de reloj en los biestables (aproximadamente 75 u.S.).

Esta señal demorada se obtiene de Q del segundo biestable

en cada circuito de demora, mientras que las señales para

controlar al "multiplexer" (9L) .

Se obtienen de las salí.

das Q, a través de los OR (12L y 13L, derecha) respectivo,

de los dos biestables de cada circuito de demora.

2 . 4-: 3 .

INDICADORES DE DATOS Y DIRECCIONES

Consisten en dos grupos de 4 indicadores luminosos hexadecimales de 7 segmentos, TIL311, conteniendo cada indicador la lógica necesaria para la retención y conversión de 4 bits binarios a 7 segmentos, como también el

manejo de los LEDS que componen los segmentos.

En el grupo de indicadores que muestran las direcciones de . localidades de memoria no se utiliza su capacidad de retención de datos ya que éstos son retenidos

en los registros retenedores de direcciones y conectados

a los indicadores a través de los buffers respectivos.

Estos indicadores se encienden solo cuando el sistema está en el modo de programación.

En el 'otro grupo, el de

datos, los dos dígitos menos significativos se encienden

o apagan de acuerdo a las necesidades del sistema; ésto

12

es , cuando el sistema está en el modo de programación están apagados, y son encendidos bajo control de los progr_a

ma's monitores o del usuario.

Cada indicador tiene, en la parte inferior del

dígito, un LED a cada lado del mismo y que normalmente

se usan para indicar el punto decimal.

Se usan estos

LEDS , encendiendo ambos al mismo tiempo, para indicar

el próximo dígito a escribirse.

La circuitería que con-

trola estos LEDS asi como la retención de datos en los

indicadores se explica en los numerales 2.7-4.a y 2.7-6

respectivamente.

2.4-4.

INDICADORES DE STATUS.

Muestran el status tanto de los programas monitores como de algunas señales de control.

caso, 16 LEDS realizan dicha

En el 'primer

función y son manejadas

por los retenedores (19H), los cuales son a su vez controlados por el decodificador 74LS154' (13H) que realiza

la función de decodificador de periféricos (I/O) bajo

control de los programas monitores.

'Para el caso de las señales de control, éstas

son manejadas por el retenedor (27E) que trabaja sólo

como buffer.

Estas señales son activas algunas en alto

y otras en bajo, por lo cual, para las activas en alto,

se han colocado los inversores

(28E) a las salidas res-

pectivas del retenedor (27E) para el encendido de los LEDS.

13

2.5.

MEMORIA

El bloque de memoria puede dividirse en tres gru.

pos:

MONITOR, RAM DE MONITOR y RAM DEL USUARIO.

TOR ocupa tres EPROMS 2716

El MONI_

( 2 K x 8 bits c/u): dos de ellos

(13C) y (14C) en los primeros 4 K bytes de memoria, mientras que al tercero (15C) en los últimos 2K de memoria.

Este ultimo 2716 no es utilizado totalmente, ocupándose

las siguientes localidades: F800H- F916H y FC00H->FFFFH ;

de manera que quedan libres las localidades F917H-*-FBFFH,

pudiendo ser utilizadas en el futuro para almacenar algún

programa que pueda ser útil al sistema.

El RAM DEL MONITOR es el área de memoria utilizja

do por los programas monitores para almacenar datos obtenidos durante los diversos procesos que estos realizan.

Esta área se encuentra en las localidades 1000H-»1125H

El resto de la memoria (aproximadamente 58K bytes!

son para el usuario (RAM DEL USUARIO), comenzando en 1126H

Existen implementados en el sistema 4k bytes de

RAM que se reparten entre RAM del Monitor y RAM del usuario, siendo ésta reubicable mediante el conmutador SW1

(16E) .

Antes de explicar esta reubicación es necesario

explicar la decodificacion para la memoria, tanto EPROM

como RAM.

Para ésto se pensó habilitar la memoria resi-

14

dente en el sistema en bloques de IKxS bytes, para lo cual

se requerirán 4 decodificadores 4 a 16 ( 74LS154) , de los

cuales dos están implementados en el sistema (15D)y

(15F) ;

un decodificador 2 a 4 (18C) , que habilita a los decodificadores anteriores, complementa el circuito de decodifica

ci5n de memoria.

El decodificador (15D) selecciona los primeros

16K bytes mientras que el decodificador

los últimos 16 K bytes.

(15F)

selecciona

Los dos decodificadores restan-

tes necesarios deben ser suministrados exteriormente y

seleccionan el segundo y tercer bloque de 16K bytes, recibiendo su habilitación

te las salidas

del decodificador (18C) median-

2YI y 2Y2 que son accesibles externamen -

te .

Los primeros 2K bytes de EPROM

(13C) se habili-

tan mediante el decodificador (15D), 1.a compuerta AND

(14D) y el OR (13D) .

bido a que el

Esta compuerta OR es necesaria de-

MP6800 no establece diferencia entre

cir-

cuitos de I/O y memoria, y dado que la decodificación

de. I/O fue diseñado alrededor del Z 8 O y se realiza en

los primeros

256 bytes, es necesario deshabilitar los

primeros 2K de memoria

6800.

(13C) cuando está seleccionado el

El OR (13D) recibe las señales para habilitar lo's

2K de memoria mencionados

(3K) .

El AND

(13C) del AND

(14D) y del ÑOR

(14D) recibe las señales de selección de

los primeros 2K de memoria provenientes del decodificador

(15D) mientras que el ÑOR

(3K) genera la señal de

15

deshab-ilitación mencionada cuando se selecciona el 6800.

Los siguientes 2K de EPROM (14C) reciben su habilitación del decodificador (15D) através del AND (15D)

re spectivo.

Los últimos 2K de EPROM (15C) reciben su habilitación del decodificador (15F) a través del AND (15D)

res-

pectivo .

La RAM incorporada en el sistema recibe su habilitación del multiplexer cuádruple 74S257 (16E) que sirve

como " reubicador" de esta, a excepción de los circuitos

de memoria (17D) y (18D) que son utilizados para RAM del

Monitor y se habilitan directamente

del

decodificador

(15D) r Pin 5, como el quinto K de memoria.

El conmutador SW1 (16E) , como se menciono anteriormente, controla la reubicacíón de las áreas de RAM,

y estando en la posición indicada en el diagrama (funcionamiento normal) permite que los 2114, que forman la RAM

del sistema, reciban las señales presentes en las salidas B del multiplexer

(16E).

Además, la entrada OE de

los 2716'está puesta a tierra mediante el conmutador

SW1 y su control depende de la entrada CE en cada uno.

La distribución de RAM en este caso, analizando las sal_i

das del multiplexer

(16E), es la siguiente: 1Y=5K—6K-1,

2Y = 6K-^7K_1, 3Y = 7K->8K— 1 , y 4Y = 8K-'9K~1 .

16

AL cambiar al conmutador SW1 de posición , la entrada ~OE (fe los 2716 se coloca en XL deshabilitando a éstos, y la entrada SEL del multiplexer

(16E) se coloca a

tierra pasando a sus salidas las señales presentes en las

entradas A, en cuyo caso aquellas tienen la

siguiente

distribución de RAM: 1Y = OK-*1K—1 , 2Y = lK-r2K-l , 3Y=6 2K—6 3K— 1 ,

y

"-tí.

u j jx-^

-i- .

Esto quiere decir que se pueden utilizar

los pr_o_

gramas monitores para desarrollar programas del usuario

y probar éstos, luego, en las localidades en las que estarían en la práctica, es decir, a partir de 0000H en el

caso del Z80 y 8085A, y en el último K de memoria en el

caso del 6800.

También es útil ésto al utilizar micro-

procesadores externos al sistema cuya primera instrucción

se obtiene de 0000H o FFFEH.

2.6.

BUFFERS

2.6-71.

BUFFERS DE DATOS Y DIRECCIONES DE LOS

uP s .

'Están formados por 4 circuitos integrados 8212

y separan a los uPs del resto del sistema con el fin de

colocar la mínima carga posible en los respectivos buses

de éstos.

Dos de ellos, (4B) y (4C), son para el bus de

direcciones, y los otros dos, (4E) y (4F), son para el

bus de datos.

17

Los primeros, (4B) y (4C) se habilitan cuando

se selecciona uno de los tres uPs residentes, y se logra

controlando las entradas DS1

y DS2 de estos integrados.

La entrda DS2 está comandada por el selector de uP s

74LS175, (10F) pin 14, que es la señal de habilitación

(activo en OL) para un uP externo, y que al estar en IL

activa la entrada DS2 en los buffers en cuestión.

La en.

trada DS1 se desactiva solo cuando el sistema entra en el

modo de programación lo cual se logra mediante el biestable

(16N) pin 9.

Los buffers (4E) y (4F) tienen conectadas las

entradas del uno con las salidas respectivas del otro

formando un buffer de 8 bits de dos vías para el bus de

datos.

La entrada DS2 del buffer

(4E) está comandada

por dos señales; la una proveniente del selector de uPs

74LS175 (10F), pin 15, a través

del inversor de colector

abierto (5D) que habilita al buffer cuando se selecciona

uno de los uPs residentes, y la otra proveniente del AND

de 4 entradas

(3G), a través del transistor (5D) respect^

vo, compuerta que deshabilita al buffer cuando detecta

uh estado de alta impedancia en todos los uPs- Estoes nece

sario para casos como el de transferencia de datos median

te DMA.

La entrada DS1 del buffer

(4E)' y la entrada DS2

del buffer (4F) están conectadas entre sí y controladas

18

por la señal WR de los uPs; la entrada DS1 del buffer

(4F) está controlado por la señal proveniente del circuito formado por los ÑOR (4G), (4G) y (1E).

La señal proveniente de este circuito es equivalente a la señal RD y se genera cuando el uP seleccionado ejecuta una operación de lectura.

Sinembargo , es nec_e_

sario considerar que aunque los uPs generan directamente

la señal RD, el Z80 realiza un cierto tipo de lectura

sin generar esta señal.

Esto se produce durante inte-

rrupciones que utilizan la entrada INT del uP .

Este nece

sita que le sea suministrada cierta información para poder dar servicio _a dicha interrupción, y el uP genera entonces las señales MI e IORQ juntas/

(sin la señal RD)

debiéndose obtener de las mismas la señal requerida para

habilitar al buffer

(4F).

Las tres compuertas ÑOR mencionadas (4G), (4G)

y (1E) generan esta señal de habilitación a partir de las

señales RD, Mi e IORQ.

Con ésto, los buffers se habilitan de acuerdo

a la operación en proceso:

lectura

(RD), escritura

o alta impedancia,

2.6-2.

BUFFERS DE DATOS Y DIRECCIONES

DEL TECLADO

A semejanza del caso anterior/ estos buffers

están formados por 4 circuitos integrados 8212 y separan

19

las direcciones y datos provenientes del teclado, de los

buses de direcciones y datos, respectivamente, del sistema .

Los buffers (71) y (81) son para el bus de dire£

cienes, cuyas salidas se conectan a las de los buffers

(4B) y (4C), respectivamente, descritos en el numeral anterior; sus entradas son alimentadas desde los contadores

UP/DOWN programables (7K), (7K), (8K), (9K) mencionados

en los numerales

2.4-1 y 2.7-4.C.

Los buffers (101) y 111) corresponden a los datos y están conectados en paralelo, con sus salidas alimentando a los indicadores de datos (11C), (11C) , (12C) ,

(12C); sus entradas reciben la información de los retenedores (10K) y (11K)

que componen

los 8 bits de datos.

Los buffers (101) y (111) están en paralelo debido a que para ciertos procesos los uPs necesitan leer

dos bytes de información provenientes del teclado, bytes

que necesitan ser mostrados primero en los cuatro indicadores de datos y luego leidos por los uPs.

Debido a ésto,

es necesario retener esta información en alguna parte, y

esto se logra utilizando los buffers mencionados como retenedores además de buffers.

Los buffers (71) se habilitan cuando el sistema

está en -el modo de programación y esto se logra controlan

do las entradas DS1 desde el biestable (16N) , pin

20

El control de los buffers (101) y (111) es compartido entre señales de control del teclado y el contr_o

lador de I/O de los uPs, y será explicado en el numeral

2.7 - -4 .b.

Durante el modo de programación solo se habilita el buffer

(111) para la transferencia de datos desde

el teclado hacia la memoria.

2.6-3.

BUFFERS DE INTERCONEXIÓN.

A este grupo corresponden los buffers (6H),

(61) , (13D) y (13E) .

Los dos primeros sirven en reali-

dad como pórticos de I/O para la lectura de datos del te

ciado y escritura de datos a los indicadores de éstos;

reciben su habilitación, en la entrada DS2, desde el

biestable

(16N), pin 8, deshabilitandose cuando el siste-

ma está en el modo de programación.

El control de la dirección de flujo de los datos viene del decodificador

el buffer

de I/O 74LS154 (13H): para

(6H) a través del AND

decodificador, y para el buffer

(19M)/ salidas 4 y 5 del

(61) a través del AND

(131)/salidas 6 y 7 del decodificador.

Las señales pro-

venientes de estos AND alimentan las entradas DS1 de los

respectivos buffers.

Los buffers

(13D) y (13E) unen el bus de datos

proveniente de la memoria (bus de datos del sistema) con

21

el bus de los indicadores de datos; se habilitan solo

cuando el sistema está en el modo de programación y para

este proposito, la entrada DSl en el buffer (13D), y la

entrada DS2 en el buffer (13E) reciben la señal de habilitación del biestable (16N), pines 8 y 9, respectivamente .

La entrada DS2 en el buffer (13D) está conectada a la entrada DSl en el buffer (13E) y señalan la dire_£

ción de flujo de los datos de acuerdo a la señal proveniente de la compuerta OR

(L 3L, izquierda). Esta señal será ex

plicada en el capítulo 2.7— 4.b.

En general, estos dos

buffers permiten, gue un dato sea escrito en memoria e inmediatamente leído (programación del sistema), o leer,

sucesivamente, localidades de memoria.

2.7.

•

CIRCUITOS

2.7-1.

DE CONTROL

SEÑALES BÁSICAS

El decodificador '74154 (15J) y el decodificador

74LS155 (8L) constituyen el "centro" de los circuitos

de control. Entre los dos generan todas las señales de

control del sistema provenientes de los teclados.

A continuación se indica la correspondencia en

tre las salidas de los decodificadores y las respectivas

señales de control.

22

74154 (15J)

74LS155 (8L)

0 -

ESCAPE

8 -ARS

1Y0- SHIFT

1 -

SS

9 -BREAK CHECK

1Y1- L

2 —

RD PGM4-

10 -BREAK REMOVE

1Y2— H

3 _

RD

pGMí

u -BREAK

INSERT

1Y3

4 —

RESET CPU 12 —EXTRA

2Y0— GO

5 -

WR PGM

2Y1— REG

6 -

REG. STR 14 -8085A

2Y2- REG

7 -

MNU

2Y3-

13 -6800

15 -280

2 . 7-2.

INTERRUPCIONES

De las señales anteriores, las siguientes son

usadas por los programas monitores:

ESCAPE, SS, REG STR,

MNU, A R S , BREAK CHECK, BREAK REMOVE, BREAK INSERT, L, GO ,

REG, REG.

Estas señales producen una señal de

interrupción

a través del NAND de 13 entradas (18J), la cual se canaliza a cada uP mediante los' NAND

el paso de la señal proveniente

al uP seleccionado.

(7F) y (8F) que permiten

del NAND (18J) solamente

Esto es necesario debido a que si se

aplica la señal de interrupción a todos los uPs

simultá-

neamente, en ciertos casos, al seleccionar uno a continua

ción de otro

el uP seleccionado reconocerá

la señal y

entrará a decodificar y dar servicio a dicha interrupción

inmediatamente después de haber sido seleccionado, realizando así una función errónea.

23

Estas señales de interrupción se aplican a las

entradas de interrupción de mayor prioridad en los uP s:

NMI para el caso del 280 y 6800, y TRAP para el 8085A.

Las compuertas NAND (7F) que manejan estas entradas de

interrupción/ son de colector abierto ,_ lo cual permite

que señales de interrupción provenientes de circuitos

externos al sistema puedan ser aplicados a las entradas

respectivas en los uPs del sistema

8085A la señal de interrupción

(Z80 , 6800).

Para el

(TRAP) externa debe ser

aplicada a la entrada del inversor de colector abierto

(7E), abriendo antes el interruptor ESI (1),(7E) .

Para ejecutar la rutina correspondiente a la fun

ción que se desea, el uP seleccionado, al recibir la señal de interrupción, lee los buffcrs 74367 (171) que permiten el paso de las señales provenientes del teclado y

que producen una interrupción.

El uP identifica la fun-

ción que se está solicitando y procede a la ejecución

de la rutina respectiva.

Si después de leer los buffer (171) el uP encuentra que ninguna de las señales está activa, es decir,

no se solicita ninguna función, el uP determina que la in

terrupción proviene de algún circuito externo al sistema

y salta a una localidad de memoria determinada donde el

usuario deberá haber puesto una instrucción de salto hacia la rutina de servicio de dicha interrupción.

24

2.7^3.

CONTROL DE I/O

El decodificador 74LS154 (13H) genera todas las

señales de control para los circuitos de I/O del sistema,

bajo control de los programas monitores. Sus entradas de

selección (A,B,C,D,) están conectadas al bus de direcciones del sistema, y en cuanto a sus entradas de control,

G2 está comandada

por la señal 10RQ proveniente de la

compuerta OR (2H) cuyo funcionamiento está explicado en

el numeral 2.3.

La entrada Gl está comandada por el NAND

de cuatro entradas

(7H), el cual, en conjunto con el AND

de dos entradas de colector abierto

(7H), determina que

para el 280 y el 8085A el decodificador

(13H) responda

a las últimas 16 direcciones del mapa de I/O, es decir,

desde P0H hasta FFH.

Para el 6800, el decodificador

(13H) responde a las direcciones desde 00F0H hasta

00FFH del mapa de memoria.

Esto se logra añadiendo al circuito

anterior

de habilitación de la entrada Gl del decodificador

(13H)

el circuito formado por las compuertas OR (7C), el transistor

(7D) y el transistor

(6F).

Las compuertas OR (7C), en conjunto con el transistor (7D), generan un 1L solo cuando los 8 bits más

significativos del bus de direcciones'están en OL, y conectan esta señal en paralelo con la salida de colector

abierto del AND (7H) para deshabilitar a la entrada Gl

del decodificador (13H) , a través del NAND (7H) , si uno

25

de los 8 bits mencionados está en 1L.

El transistor

(6F) está siempre saturado

no está seleccionado el 6800.

cuando

Mediante la señal prove-

niente de la compuerta ÑOR (U) , cuyo funcionamiento fue

explicado en general en el numeral 2.3

y que produce un

OL siempre que este seleccionado el 6800, este transistor se corta, liberando la base del transistor (7D) y per_

mitiendo así que las OR (7C) formen parte del control de

la entrada Gl del decodificador (13H).

Las señales de control de I/O que genera el decodificador (13H) se describen a continuación:

Las salidas 14 y 15 habilitan a los buffer's

(171) para la lectura de las señales de interrupción provenientes del teclado; las salidas 13 y 12 controlan la

carga de datos en los retenedores

(19H) que manejan a

los indicadores de status; las salidas 11,10,9 y 8 controla al interfase de periféricos programables 8255 (27C)

que controla el circuito de programación de EPROMS; las

salidas 7 y 6 habilitan al buffer de interconexión

(GI)

através del AND (131) , la salida 7 habilita además al

buffer

(101) a través

ta también al buffer

del AND (91), y la salida 6 habili(111)

a través del AND (111); las sa-

lidas 5 y 4 habilitan la retención de datos en los indica

dores (12C) y (lie) a través de los AND de co 1 ector

to

(19L)

y

( 2 0 L ) r e s p e c t i v a m e n t e , las

l i b r e s uy p

u e d e n ser

^

u t i l i z a d o s por

el

*•

¿

//

s a l i d a s 3 /^:.2 e s t á n

u s u a r i o ,' rcí?rbéfe¿on--T

[ | c¿; u.- . ív -t . < i

f(j .

00340

26

diendo a las direcciones F3H y F2H

00F3H y 00F2H

(280 y 8085A) y

(6800) de I/O; las salidas 1 y 0 permiten

el control de parte del circuito que maneja las funciones

de introducción de datos al sistema desde el teclado. Este circuito será explicado en el siguiente subcapítulo.

2.7-4.

CONTROL DE TRANFERECNIA DE DATOS CON LOS uPs

EN ALTA

IMPEDANCIA.

Este circuito recibe señales de control desde

el teclado, y de los uPs a través del controlador I/O, pa

ra manejar la transferencia de datos a los indicadores

de datos y direcciones, el encendido o apagado

de estos,

y a los indicadores del dígito a escribirse.

Dado que este circuito recibe varias señales

de comando, su funcionamiento será explicado describien

do las diversas funciones que realiza.

2.7-4.a.

INICIALIZACION DEL SISTEMA

PARA LA PROGRA-

MACIÓN.

Este modo se activa al presionar WRPGM.

El de-

codificador 74154 (15J) responde colocando la salida 5 en

OL, el cual genera una señal de borrado en el contador

UP/DOWN 74193

(15L) , a través de los AND

(15K) y el inver-

sor (15L), sirviendo además como señal de reloj para los

biestables (16N) accionando a estos al regresar a 1L.

De estos biestables, el de la" derecha 'genera las señales

27

que

indican que el sistema está en el modo de programa-

ción ocn sus salidas Q y Q.

La salida Q (pin 9) habilita

(o deshabilita, según sea el caso) a los buffers

(13E)

entrada DS2 , (4C) entrada DS1, y (4B) entrda DS1; además,

a través de los inversores de colector abierto (18K) se

coloca un OL en la entrada LSI de los indicadores de dígitos (12C) correspondientes a los dos dígitos menos sig

K

nificativos / manteniendo a éstos habilitados.

Esta misma señal, proveniente del pin 9 del

table en cuestión , a través de los inversores ( 18J) coloca un OL en las entradas 2G y 2C del decodificador

(18C)

habilitando a éste y por lo tanto el acceso a la memoria

del sistema; estas dos señales generadas a través

de los

inversores (18J) están en paralelo con las señales MREQ

(salida 12 del inversor inferior) y la formada por RD"WR,

mediante el AND (1H) , (salida 10 del inversor superior) ,

señales explicadas en el numeral 2.3.

La señal proveniente de Q (pin 8), del biestable

(16N, derecha) habilita o deshabilita según sea el caso

a los buffers: (13D)

entradas DS1,(6H) entrda DS2, (61)

entrada DS2, (71) entrada DS1 y (81) entrada DS1. La salida

Q (pin 6) del otro biestable

(16N, izquierda) coloca un

OL en el OR (12K) para permitir el paso de una señal

proveniente de este mismo circuito de transferencia de

datos, destinada a incrementar automáticamente los conta

dores que direccionan las localidades de memoria cuando

se está cargando un programa del usuario en el sistema;

28

también coloca un OL en el OR (17E) que permite el paso

de la señal de escritura WR, proveniente del sistema de

transferencia de datos, hacia la memoria.

Esta señal WR PGM generada desde el decodificador

(15J) genera también una señal de borrado a través

del AND

(10M) que inicializa el circuito de selección de los uPs

y el circuito de generación de RESET inicial de los mismos, circuitos que serán explicados mas adelante; esta

misma señal, a través del AND (11M) produce una señal de

borrado para el biestable (15N izquierda), y el biestable (17M) .

Este, a través cb Q (pin 8) controla el bloqueo

de los dos dígitos mas significativos de los indicadores

de datos (11C), y al estar el biestable borrado, éstos

están bloqueados.

Al estar borrado (15N) , izquierda) ,

la salida Q coloca OL en la entrada B del decodificador

(16L) a través del AND

(15L) respectivo, lo. cual permite

que la selección de las salidas del decodificador

(16L)

dependa solamente de la entrada A: la salida Q del biestable coloca un 1L en la entrada de

selección de pala-

bra del multiplexer (17L, izquierda) y un OL, a través

del inversor respectivo en el multiplexer (17L, derecha).

El 1L selecciona la palabra A2, B2 ,C2 ,D2, mientras que

un OL selecciona la. palabra £1,131,01,01.

Asumiendo que

el biestable (15N, dere'cha) esta

borrado, éste coloca un OL en la entrada lG,a través

AND

(15L)

del

respectivo, y un 1L en la entrada 2G, del deco-

dificador (16L) habilitando de esta manera las salidas

29

1YO,1Y1,1Y2,1Y3 del mismo.

Las salidas del multiplexer

(17L, derecha) dependen, entonces del contador UP/DOWN

(15L); al estar este borrado, aparece un OL en la salida

1YO del decodificador

(16L), y al estar conectados los

multiplexers (17L) como se muestra en el diagrama, este

OL aparece en la salida QB del multiplexer

(17L, derecha).

Las salidas de este multiplexer están conectadas, a través de resistencias, a los cátodos de los LEDS de los pu_n

tos decimales del dígito más significativo; estos puntos

decimales, al encenderse, indican cual es el siguiente

dígito que se va a escribir.

De esta manera, para este

caso, el dígito a escribirse es equivalente al medio byte

más significativo de la palabra (8 bits) que se va a escribir en memoria.

2.7-4.b.

INGRESO DE DATOS

Al presionar

una tecla correspondiente a un

carácter hexadecimal, el valor binario correspondiente

a dicho carácter se coloca en las salidas del decodificador (7L) y se genera un pulso, DA, mediante el circuito explicado en el numeral 2.4—2.

Esta señal pasa por

el OR (13L , izquierda) cuya entrada es la señal provenieri

te del bit mas significativo del decodificador (7L),

a través de los inversores (7L), lo cual determina que

solo los caracteres hexadecimales permitan el paso del

pulso DA hacia el contador (15L) y los demás circuitos

involucrados con esta' señal.

Estos circuitos son: el

de escritura en memoria, los buffers de

interconexión

30

(13D) y (13E)-, y las compuertas que generan diferentes

pulsos para la carga de los datos en diferentes retenedores, estas compuertas son las localizadas en (18L),

(18M),

(19L) y (20L).

Para la escritura en memoria, la señal DA proveniente del OR

(13L, izquierda) pasa a través del OR

(17E) .

habilitado, como ya fue explicado, por el biestable (16N ,

izquierda) hacia la entrada

lo.s.-'.inversores (17E).

WE de las memorias a través

de

La salida del inversor de colector

abierto (17E) está conectada a la salida WR de los uPs.

Como DA es un pulso, cuando éste no está presente, la memoria está habilitada para la lectura, ésto implica que

los buffers de Ínter coneccion (13D) y (.13E) permitan el

paso de información desde los buffers de datos del teclado hacia la memoria solo durante la duración

de DA', mien

tras que en ausencia de éste, el sentido del paso de información debe ser desde la memoria hacia los indicadores

de dígitos.

Esto se obtiene conectando la señal en cues

tión a la entrda DS2 del buffer (13D) y a la entrada

DS1 del buffer

(13E) .

La señal DA está conectada a todos los OR (18L)

y

(18M) pero solo pasará por aquél cuya otra entrada es-

té en OL, y esto ocurre, para este caso, s5lo con el OR

conectado a QB del multiplexer (17L, derecha) obteniéndose así un pulso a OL en su salida que se transmite a tres

compuertas AND como se puede apreciar en la figura.

conexión

La

al AND de colector abierto no tiene, en este

31

caso ( el de ingreso de datos), ninguna consecuencia ya

que su salida está fija a OL por acción del biestable

(16N, derecha), pin 9 y los inversores (19K) como fue

explicado anteriormente.

De los otros A N D - aquél que

a su salida tiene el inversor (19K, derecha) da un pulso

de carga para el retenedor

(10K) que cargará el valor c_o

rrespondiente al carácter hexadecimal a la salida del decodificador

(7L).

El tercer AND genera dos pulsos, (uno

a OL , a través del AND

(91) en la entrada DS1 del buffer

(101) y uno a 1L, a través

del inversor ( 91) en la entr_a

da STB del mismo buffer.

Con ésto se realizan dos funciones:

Se habilita

al buffer para que permita el paso del dato presente a

sus entradas y que proviene de los retenedores (10K) y

(11K), y al desaparecer los pulsos

se retiene este dato

aunque el buffer queda deshabilitado, es decir, en alta

impedancia.

Aquí caben dos explicaciones, una acerca del

estado de alta impedancia del buffer y otra para justificar la retención del dato ya que esto parecería ser

redundante debido a los retenedores (10K) y (11K).

Para

el caso-de la alta impendancia, se menciono anteriormente

que durante el modo de programación los buffers, (13D) y

(13E) estaban conectados de tal manera que la dirección

del paso de información - sea desde la 'memoria hacia los

indicadores de datos

(y por consiguiente a las salidas

de los buffers (101) y (111) ), excepto durante la duración de DA, de ahí que es necesario que estos se habiliten solo durante el pulso mencionado.

En realidad el

32

buffer (111) se habilita solo para una función que puede

realizarse solo bajo control del programa monitor.

En

cuanto a la retención/ durante ciertos procesos bajo control del monitor/ el uP en funcionamiento necesita -de 16

bits

de información desde el teclado

{ y es aquí donde

el buffer (111) entra), información que pasa por los

retenedores (10K) y (11K)

(solo 8 bits) y por tanto 8

bits deben ser retenidos mien-tras se cargan los otros 8.

Al retornar-DA

a 1L se incrementa' el contador

(15L), y debido a que los AND

(15L) no han variado/ la

salida QA del multiplexer (17L, derecha) se coloca en OL,

con el resto de sus salidas

del pulso DA a través

3 AND

en 1L.

Esto permite el paso

del OR (18L) respectivo y hacia los

(19L) correspondientes, y en este caso, el AND que

tiene a su salida el inversor

(18K, izquierda)da vn impul-

so de carga en el retenedor (11K)/ el AND de colector abierto no realiza ninguna función debido a la explicación

dada en el caso de la salida QB, y el tercer AND es el

mismo mencionado en el caso de QB y que genera dos pulsos

en el buffer (101) con un resultado semejante al anterior

pero en este caso con la nueva información procedente

del retenedor (11K) y por supuesto la retenida anteriormente en (10K) .

Al retornar DA a 1L , se incrementa nu_e

vamenté el contador

(15L) y como los AND (15L) aun no han

variado/ la salida QB del multiplexer (17L, derecha) , se

pondrá en OL y QA regresará a 1L; este pulso generado

por QA y DA a través del AND respectivo (18L) pasa por el

OR y AND (12K) hasta la entrada CU del contador (9K) el

33

cual incrementa su valor en 1, incrementando así la cadena de contadores que direccionan las localidades de

memoria.

De aquí en adelante, sin cambiar de función, el

proceso anterior ( el de ingreso de datos) es cíclico.

Un OL estará alternando entre QA y QB del multiplexer

(17L) generando los pulsos de carga, escritura e incremento de direcciones.

2.7-4.C.

LECTURA DE LOCALIDADES DE MEMORIA

Estando el sistema en el modo de programación, al

presionar la tecla H se entra al modo de lectura de una

localidad cualquiera de memoria; el decodificador (8L)

coloca su salida 1Y2 en OL, el cual acciona la entrada

LOAD del contador (15L), da una señal de reloj para el

biestable (15N, derecha) , y un.a señal de borrado para el

biestable (16N, izquierda).

Al borrar (16N , izquierda) su salida Q se coloca en 1L deshabilitando, mediante el OR (12K) el incremen

to de direcciones como efecto de la introducción de carao

teres hexadecimales.

El biestable (15W, derecha), por su parte, al re

cibir la señal de reloj, coloca un 1L en su salida Q y un

OL en Q.

Q está conectado a la entrada PR del biestable

(15N, izquierda) y al OR (15L), el cual permite el paso de

34

la señal proveniente de la salida 1YO del decodificador

(16L), al mismo tiempo que el OL en la entrada PR de

(15N , izquierda) coloca un 1L en su salida Q conectada

al AND (15L, superior) habilitando a este para pasar la

señal de la salida QB del contador (15L), además la salida Q del mismo biestable (15N, izquierda) se coloca en

OL, seleccionando así la palabra Al, B1,C1,D1 en el multiplexer (17L , izquierda) y A2, B2,C2,D2, en (17L , derecha) .

El 1L en Q de (15"N , derecha) permite el paso

de la señal de la salida QC del contador (15L) a la entra

da 1G del decodificador (16L) y el complemento de esta se

nal a 2G del mismo decodificador.

El OL en la entrada LOAD del contador (1SL) carga el valor 4b, el cual, conjuntamente con los AND

selecciona las salidas 2YO ,2Y1 , 2Y2 , 2Y3

(15L)

del decodificador

(16L) y estando las entradas A y B del mismo en OL, coló

ca un OL en la salida 2YO.(

, Las salidas 2YO, 2Y1, 2Y2, 2Y3 están conectadas,

a través de resistencias, a los catados de los LEOS de los

puntos decimales de los indicadores de direcciones, corres

pendiendo 2YO al mas significativo, también están conecta

dos a los OR (18M).

Los puntos decimales, al igual que

en el caso de los datos, indican el dígito a escribirse.

Los OR (18M) cumplan una función similar a los OR

(18L)

en cuanto permiten el paso de la señal DA, proveniente

35

del OR (13L), si su otra entrada está en OL, al retenedor

respectivo.

En este caso, los retenedores son los conta-

dores (7K), (7K), (8K), (9K) que componen los 16 bits para direcciónar las localidades de memoria.

• Al introducir

la dirección de la localidad de

memoria que se quiere leer, el OL en la salida 2YO del

decodificador (16L) se va desplazando hacia 2Y3 cargando

al mismo tiempo cada dígito en el retenedor

respectivo, hasta que llega a 2Y3 .

contador

(contador)

En este momento, el

(15L) tiene en sus salidas el valor 7b y hasta

ahora los AND

(15L) no han variado, sin embargo , al intro-

ducir otro carácter hexadecimal, las salidas del contador

cambian al valor 8b y esto coloca un OL, a través del AND

(15L,

inferior) en la entrada 1G y un OL en la entrada

2G del decodificador (16L) seleccionando así las salidas

1YO, 1Y1, 1Y2, 1Y3 y colocando un OL en 1YO.

transmite a través del OR y los AND

Este OL se

(15M) a la entrada de

borrado del biestable (15N, izquierda); el OL en su entra

da PR todavía está presente, de manera que estas dos seña

les, en conjunto, colocan tanto a la salida Q como Q en

1L.

Este 1L en Q realiza la misma función descrita en el

numeral 2.7-4.a. , mientras que el 1L en Q permite aún

el paso de la señal de la salida QB

del contador (15L),

a través del AND respectivo, a la entrada B del decodificador (16L).

En este punto, cabe la explicación de la función

de retroceso de la señal que indica el siguiente dígito a

36

escribirse.

dor

Al presionar la tecla SHIFT, el decodifica-

(8L) coloca su salida 1YO en OL, el cual se transmite

a la entrada CD del contador

(15L) decrementando a éste.

Esto tiene como efecto que el OL a la salida seleccionada

del decodificador (16L) pasa a la salida anteriormente s_e

leccionada, y esto a su vez tiene como efecto que los LED

que indican el siguiente dígito a escribirse, se apagan

y se encienden los del dígito aunteriormente escrito.

Con esto se ve la necesidad de aplicar una señal

de bo-

rrado y PR simultáneamente, en el biestable (15N, izquier;

da) para el CHSo anterior.

Al presionar SHIFT una vez que

el Olf pasó de la salida 2Y3 a la salida 1YO en el decodificador

(16L) , dicho OL regresará a 2Y3 y las salidas Q y

Q del biestable (15N , izquierda) serán 1L y OL, respectivamente y el sistema estará nuevamente en el modo de lectura de una localidad de memoria.

Si, por el contrario, una vez pasado el OL de la

salida 2Y3 a la salida 1YO se presiona un carácter hexadecimal, el OL, que pasa a la salida 1Y1 es una señal de bo

rrado para el biestable

(15N, izquierda) , el cual quita

el OL de la entrada PR de (15N, izquierda) permitiendo

que sea la entrada de borrado, CLR, la que tome control

y mantenga borrado al biestable y el sistema queda fijado para el modo de ingreso de datos excepto por una señal:

la proveniente del biestable (16N, izquierda), que fue

borrado al presionar la tecla H y no ha sido alterado

desde entonces.

Esta señal, como ya se ha explicado ,

permite o (y, en este caso) impide el paso, mediante el

37

OR (12K), de la señal de incremento para los contadores

que forman los 16 bits

para direccionar las localidades

de memoria, como también la señal de escritura de memoria

mediante el OR (17E) y los inversores (17E).

De esta manera, al seguir tratando de introducir caracteres, hexadecimales, no pasará nada: no variará la dirección de localidad introducida ni se alterará

el contenido de dicha localidad aunque sí variarán los

datos en los retenedores de éstos.

Para poder alterar

el contenido de la localidad de memoria es necesario

presionar WR PGM nuevamente, y con ésto el sistema se

comportará como ya fue descrito para dicho caso.

Con el sistema en el modo de programación después de haber presionado WR PGM, H, o haber introducido

datos, se puede leer localidades sucesivas de memoria

hacia arriba ( incremento de dirección) o hacia abajo

(decremento de dirección) presionando las teclas RD PGM!

a RD PGMi, respectivamente.

Al presionar el primero,

el decodificador (15J) coloca su salida 3 en OL, el cual

se transmite , a través del AND

(12K)

, a la entrada CU

del contador (9K) incrementando la cadena y por ende la

dirección mostrada al momento..

La tecla RD PGMI por su

parte, activa la salida 2 del decodificador (1SJ) y esta

señal se conecta directamente a la entrada CD del contador mencionado, decrementando la dirección.

sucesivas de estas teclas

Presiones

incrementarán o decrementaran

según sea el caso, la dirección que aparece en los indi-

cadores respectivos.

La acción de estas dos teclas es independiente

de cualquier otra función, excepto durante la señal aut£

mática de RESET (POR).

2.7-5.

SELECCIÓN

DE LOS uPs.

Una vez introducido el programa del usuario.

se

procede a la selección del UP con el que se va a trabajar, esto se logra simplemente presionando la tecla correspondiente al.uP deseado, lo cual coloca un OL en una

de las 4 últimas salidas del decodificador (15J).

Estas

salidas están conectadas al AND de 4 entradas (11G) y a

las entradas D de los biestables

(10H) y (11H) corres-

pondiendo los de (IIH) a las salidas más

vas.

significati-

El AND de 4 entradas (11G) , a través del inversor

(11G) produce un pulso de borrado

para el circuito de

Transferencia de Datos mencionado anteriormente

y este

mismo pulso, a través del otro AND (11G), cuya otra entrada es la señal proveniente

de la salida Q del bies-

table (14L), pin 9, generación de la señal DA para el

teclado (12J)), genera una señal de habilitación para el

biestable (8G) y de reloj para los biestables (10H) y

(11H).

-Al cargarse estos biestales, solo uno de ellos

tendrá a su entrada D el OL que corresponde al uP que

se quiere seleccionar, el resto tendrá obviamente un 1L;

ésto implica que la salida Q de estos biestables, que es

la que se utiliza en este circuito, estará en OL luego

39

del pulso de carga y deberá permanecer

en OL hasta que se

presione la tecla del uP correspondiente.

Esto obliga a

que después de un encender el sistema, es decir después

de la señal automática de RESET (POR) las salidas Q de los

biestables

(10H) y (11H) estén en OL, lo cual se logra

aplicando la señal POR a las entradas PR de estos biestables.

La aplicación de esta señal, proveniente del tem-

porizador 555 (41) a través

del inversor

(51), es a través

del AND (10M), cuya otra entrada proviene de la señal

WR PGM, la cual causa el mismo efecto que POR, para este caso.

Al habilitarse el biestable (8G) , con el mis-

mo pulso de carga de (10H) y (11H) , éste genera, en conjunto con: el contador doble 74393

(9H), el AND

(9H) y el inversor

(8H), el biestable

(9G), un solo pulso ha-

cia OL en la salida Q del biestable (9H) , que produce ,

a través del AND

(8G), cuya otra entrada es la señal

POR'WR PGM del AND (10M), un pulso de borrado en el bie£

table (9G) y el retenedor (10F); el biestable (9G) genera el pulso de reloj para el retenedor que cargará los

datos en las salidas Q de (10H) y (11H) a través

de•su

salida Q y la señal de encendido/apagado a través de ~Q

para los indicadores de direcciones.

La señal de sincro-

nismo del circuito que genera el pulso hacia OL en la

salida Q del biestable

(9H) es un tren de pulsos prove-

niente de la salida CLK (OUT) del uP 8085A a través

del

AND (IB) que sirve de buffer para esta salida, y que

llega a la entrada de reloj del biestable (8G).

trada D del biestable

La en-

(9G) proviene del AND de cuatro

entradas (3G), el cual genera un 1L siempre y cuando

40

los uPs hayan generado una señal, un 1L, de reconocimiento de al-ta impedancia y por lo tanto se pueda proceder

a la selección de uno de ellos.

Mas adelante se explica-

ra esto mas detenidamente.

Hecho estas descripciones individuales se puede

visualizar mejor el funcionamiento del circuito:

se pre-

siona la tecla correspondiente a un uP, se carga un OL en

el biestable respectivo

(10H •—• 11H) , se produce un pul-

so de borrado en el retenedor (10F) y luego un pulso de

carga en el mismo que se carga con los datos provenientes de los biestables

(10H) y (11H).

Las salidas del

retenedor manejan las entradas de control de alta impedancia- de los uPs.

Para el S80, la señal de control de alta impedancia proviene de la salida Q2

colector abierto

a través del inversor

de

(6E), de esta manera se puede contro-

lar el estado de alta impedancia,

medio de algún circuito periférico

si sé necesita,

por

externo al sistema

como por ejemplo un controlador de DMA y conectando la

señal de control respectiva directamente a la entrada

BUSRQ en el Z80.

Cabe anotar que esta señal externa de-

be provenier de una compuerta o salida de colector abier

to .

Para el 6800 la señal de control de alta impedancia proviene de la s.alida Q3 del retenedor y es conec

tada a la entrada D del biestable

(9F)7 cuya entrada de

41

reloj está comandada por la salida MEM CLK, a través del

inversor (4H), del circuito generador de las fases 01 y

02 para el uP .

Esto es necesario ya que la aplicación

d-e la señal HALT al uP debe cumplir una cierta condición

de sincronismo, y esto se logra mediante el circuito

descrito.

La salida Q del biestable se conecta a

entrada HALT del 6800

la

a través del inversor de colector

abierto (8F) que cumple la misma función que el inversor

(6E) en el caso del Z80.

Para el 8085A, la salida del retenedor (10P) que

controla la alta impedancia es Ql y se aplica a la entra

da HOLD

a través de los inversores (1A, derecha) y (IB) .

La señal de control externa debe aplicarse a la entrada

del inversor de colector abierto (1A, izquierda), abrien

do previamente ES1(8)(1A) .

Esta secuencia, de borra.do del retenedor

(10F)

y luego la carga del mismo con nueva información, es necesaria debido a la demora que puede haber en la puesta

en alta impedancia de un uP y la activación inmediata

de otro, lo cual puede llevar a que en determinado

tante estén ambos activos, produciéndose

contención en los buses de éstos.

tifica la secuencia descrita:

ins-

un estado de

De esta manera se jus-

colocar todos los uPs en

alta impedancia monitorear las señales de reconocimiento del alta impedancia, y una vez que todos han respondido, entonces proceder a cargar el retenedor (10P) con

la nueva información para seleccionar el nuevo uP con

42

el que se va a trabajar.

De esto se deduce la importan-

cia del AND (3G) cuya salida está conectada a la entrada

D del biestable (9G).

2.7-6.

CONTROL DE TRANSFERENCIA DE DATOS BAJO

COMAN

DO DE LOS uPs.

Como se menciono en el numeral anterior, al seleccionar uno de los uPs se produce un pulso de borrado

para el circuito de transferencia de Datos, lo cual inicializa al circuito para poder ser utilizado adecuadamert

te cuando el programa monitor lo requiera.

Mientras

está activado uno de los uPs los indicadores de direcciones están apagados, mientras que los correspondientes

a los dígitos mas significativos de los datos se encienden o apagan bajo control del monitor.

Al requerir el monitor datos desde el teclado

se genera un pulso en la salida 1 del decodificador

(13H), el cual es una señal de borrado para el contador

(15L) a través del AND de 3 entradas (15K), y una señal

de reloj para los biestables (17N) y (15N, izquierda);

este biestable cumple la misma función que fue explicada en el numeral 2.7-4.a: permite el paso de la señal

QB del contador (15L), a través del AND (15L, superior),

a la entrada B del decodificador

(16L) y selecciona las

palabras 1 y 2 en los multiplexers (17L, izquierda) y

(17L, derecha) , respectivamente.

El biestable (17N)

genera un OL en su salida Q, que está conectada a las

43

entradas de control de encendido, BLK, de los indicadores

de los dos dígitos mas significativos de los datos, encejí

diendo a éstos.

Con el circuito de transferencia de datos fijado

de esta manera, están encendidos los LEDS de los puntos

decimale-s del dígito -mas significativo de los datos , indicando que este es el que se va a escribir, esto implica

un OL en la salida QD del multiplexer (17L, derecha)

;es-

te OL se desplaza hacia QA del mismo multiplexer a medida que se introducen los datos, y por lo tanto, también

los pulsos que aparecen a las salidas de los OR (18L) correspondientes se desplazan en el mismo sentido.

La sa-

lida de cada uno de estos OR está conectada a tres compuertas AND, una de colector abierto, una cuya salida esta conectada a un inversor, y otra sola.

Los AND conec-

tados a los OR correspondientes a las salidas QA y QB del'

multiplexer (17L, derecha) funcionan de la manera que fue

descrita en el numeral 2.7-4.b. excepto los de colector

abierto; esto se debía a cjue el biestable (16N , derecha)

tenía su salida Q en 1L, que a través de los inversores

(19K) colocaban un OL a la salida de estos AND.

En es-

ta ocasión el biestable está borrado y por tanto su salida Q está en OL de manera que los inversores colocan un

1L a su salida, habilitando a los AND en cuestión.

cuatro AND de colector abierto

Los

(19L) y (20L) controlan

las entradas de retención (LSI) de los indicadores de dígitos, estando el que corresponde a la salida

QD del

multiplexer (17L, derecha) conectado al indicador del

44

dígito mas significativo.

En cuanto a los dos AND res-

tantes , el funcionamiento de uno de ellos ya fue explicado y es el que controla la carga de información en el

buffer

(101); el otro realiza una función similar pero

con el buffer { 111) y las señales provienen de los OR

conectados a las salidas QC y QD del multiplexer

(17L, derecha) .

El programa de monitor requiere, en ocasiones,

no solo de

datos provenientes del teclado, sino también

transferir datos al usuario,

4 indicadores de datos.

y para ésto utiliza los

Si son necesarios

dos bytes

de información, el monitor, tal como en el caso anterior, genera un pulso de reloj para el biestable

(17N)

a través de la salida 1 del decodificador (13H) > para el

encendido de los indicadores correspondientes a los dosdígitos más significativos de los datos; luego procede

a escribir la información , en los cuatro indicadores,

lo cual se logra escribiendo dos dígitos (1 byte) a la

vez .

Los pulsos de escritura, o mejor dicho, de retención para los indicadores porvienen del codificador

C13H) , salidas 4 y 5 correspondiendo la salida 4 al byte más significativo ( los dos dígitos más significativos).

Esta señal está conectada a los dos AND de colec-

tor abierto

(20L) que corresponden a los OR conectados

a las salidas QC y QD del multiplexer (17L, derecha);

mientras que la señal proveniente

de la salida 5 del

45

decodificador está conectada a los otros dos AND de cole£

tor abierto (19L) y (20L).

De manera que mediante estos

AND el uP controla la retención de información en los iri

dicadores.

Estas dos señales (salidas 4 y 5 del decodi-

ficador), mediante el AND (19M) generan un pulso de habilitación para el buffer (66H) , tal como se explica en el

numeral 2.6-3.

En caso de que solo se requiera la escritura de

1 byte ( el menos

significativo), no es necesario en-

cender los dos indicadores mas significativos y se puede proceder directamente a la escritura del byte en cues

tion .

2.7-7 .

CONTROL DE INICIALIZACION

(RESET) .

Existen tres tipos de señales de RESET: RESET

automático (POR), RESET desde el teclado, y RESET de selección inicial de uP .

La señal POR se produce luego de conectarse el

equipo .o de una perdida momentánea o total del voltaje de

la línea, y proviene del circuito formado por el compara

dor

(31) , y el temporizador

555 (41) .

En el caso de pérdida momentánea o total del

voltaje de línea, si comparador detecta la baja en la

señal de 5V y produce una señal de disparo para el 555,

el cual actúa como un

monoestable y da un pulso a 1L a

46

su salida, ésta es la señal de POR, obteniéndose POR

mediante el inversor

(51).

Para el caso de encendido del sistema, el comparador mantiene disparado al 555 hasta que la fuente

(+5V) haya llegado a un valor apto para el funcionamiento

de los circuitos del sistema.

El pulso generado por el

555 es de aproximadamente dos segundos.

Esta situación de POR puede ser generada manualmente mediante

SW2 (31), localizado en el panel frontal

La señal proveniente del 555 inicializa totalmente el sistema y coloca a los uPs en estado de alta

impedancia mediante el circuito de selección de los

uPs.

uPs

La señal-POR llega a las entradas de RESET de los

a través de los AND de colector -abierto (9E) .

La señal de RESET de selección inicial se refiere solo a los uPa y - s e aplica solamente la primera vez

que se

selecciona un uP

después de un POR o WR PGM.

Es-

to se hace para asegurar que los uPs empezarán a ejecutar

los monitores a partir de las localidades de memoria

a las que deben dirigirse después de la aplicación de un

RESET.

Esto se logra con el circuito formado por los

AND

(II), el retenedor

rables

(21) y (3J).

(II) y los monoestables redispa-

Las salidas de los NAND están conec

47

tadas a las entradas ID, 2D y 3D del retenedor y cada

uno corresponde a un uP, estando sus entradas conectadas

por un lado, a la señal de reconocimiento del estado de

alta impedancia del uP respectivo, y por otro a la salida

Q correspondiente a la entrada a la cual están conectados.

La entrada de reloj del retenedor es el tren de

pulsos proveniente de CLK (OUT) del 8085A debidamente buferado por el AND ( IB, superior) que carga al retenedor

constantemente con el valor presente en sus entradas.

Después de un POR o WR PGM, las señales de reconocimiento de alta impedancia de los uPs están en 1L al

igual que las salidas Q del retenedor, lo cual coloca un

OL en las entradas D, y que es cargado constantemente en

dicho retenedor manteniendo el 1L en Q.

Al seleccionar

un uP , su señal de reconocimiento de alta impedancia se

coloca en OL lo cual cambia la salida del NAND

respecti-

vo a 1L, el cual a su vez se carga en el retenedor y aparece en la salida Q respectiva como un OL que se realimen

ta a la entrada del NAND manteniendo su salida en 1L independientemente de cualquier variación, en adelante, de

la señal de reconocimiento de alta impedancia del uP en

cuestión-.

Estas salidas

Q se conectan a las entradas

A de los monoestables mientras que las entradas B están

conectadas a la señal RESET CPU proveniente del teclado

y que al estar desactivada está en 1L.

B en 1L, al cambiar

Con la entrada

a OL la entrada A, la transición

produce un pulso a la salida del monoestable, pulso que

se transmite a la entrada de RESET del uP respectivo

48

a través del OR y AND (9E) respectivo.

Los OR (9E) per-