Evaluación 2012

Anuncio

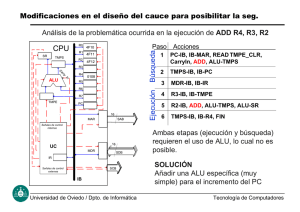

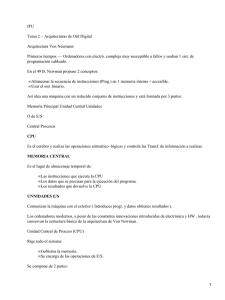

Página 1 de 3 Evaluación Trabajo Práctico Número 2 Sistemas con Microprocesadores 28/08/2012 Instrucciones La presente evaluación es individual y podrá utilizar todo el material escrito del que disponga. La misma consta de 2 ejercicios, donde la mayoría de los apartados son independientes y la duración será de 50 minutos. En cada ejercicio se indica el tiempo estimado para resolverlo y el puntaje que otorga el mismo. La evaluación se desarrollará en las hojas provistas por la cátedra a tal fin. No se permitirá intercambiar ni prestar ningún tipo de elemento entre los estudiantes. La buena presentación, ortografía y redacción serán tenidas en cuenta para la calificación final. Ejercicios Propuestos 1) (50 puntos – 25 minutos) Dada una CPU cuyo esquema simplificado se muestra en la figura y teniendo en cuenta que en la misma la ALU, todos los registros, rutas de datos y de direcciones son de 16 bits. AC MAR MDR SP PC Y IR Address Bus Data Bus Donde los registros son: PC: Registro Contador de Programa MAR: Registro de Direcciones AC: Registro Acumulador, único de propósito general Y, Z: Registros Temporales, utilizados operar en la ALU Z ALU Unidad de Control CCR Data Control Bus SP: Registro Puntero de Stack MDR: Registro de Datos CCR: Registro de Estado IR: Registro de Instrucciones Sabiendo finalmente que cada transferencia entre registros en esta CPU es de 1T y el tiempo de acceso a memoria mínimo es 2 T. a) (20 puntos) Desglose la secuencia de operaciones elementales que ejecutan la instrucción de una palabra JSRA disp, la cual tiene el siguiente RTN abstracto PC M[AC + disp] ; SP PC. Incluya en la ejecución de esta instrucción la búsqueda (fetch) de la misma. b) (10 puntos) Calcule el tiempo de ejecución de las instrucciones JMPSP y REXEC (siempre incluyendo la búsqueda de la instrucción) suponiendo que el control de procesador no presente retardo alguno. Evaluación Trabajo Práctico Número 2 Página 2 de 3 2) (50 puntos – 25 minutos) Dada la siguiente trayectoria de datos, donde todos los registros y caminos son de 16 bits. AC Y Z ALU ALU V MDR Data Bus MAR PC IR Unidad de Control Address Bus X CCR Data Control Bus Sabiendo finalmente que cada transferencia entre registros en esta CPU es de 1T y el tiempo de acceso a memoria mínimo es 3 T. T0: MAR PC; V PC + 1 T1: MDR M[MAR]; PC V T2: IR MDR T3: MAR X; V X + 1 T4: MDR M[MAR]; X V; AC Y T5: Z MDR T6: AC Z + Y T7: MAR PC; V PC + 1 T8: MDR M[MAR]; PC V T9: IR MDR T10: MAR 16@IR(16)#IR(15..0); MDR AC T11: M[MAR] MDR T12: MAR PC; V PC + 1 T13: MDR M[MAR]; PC V T14: IR MDR T15: PC 16@IR(16)#IR(15..0) a) (10 puntos) ¿Cuantos ciclos T demora la ejecución del código detallado? b) (30 puntos) Identifique las instrucciones que se ejecutan en código detallado, y escriba el RTN abstracto y el formato de cada una. c) (10 puntos) Calcule el CPI del programa. Evaluación Trabajo Práctico Número 2 Soluciones Propuestas 1) a) b) La ejecución demora 10T 2) a) Demora 25T b) c) CPI = 8.33 Página 3 de 3