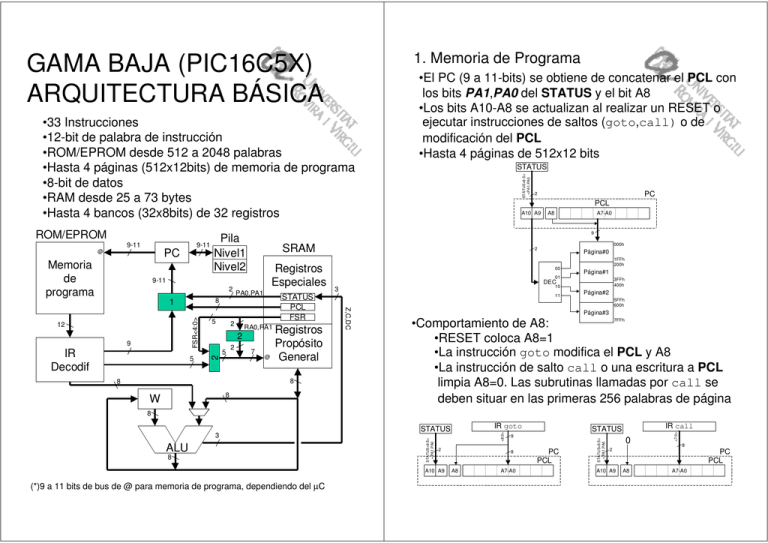

gama baja (pic16c5x) arquitectura básica

Anuncio

GAMA BAJA (PIC16C5X)

ARQUITECTURA BÁSICA

1. Memoria de Programa

ROM/EPROM

9-11

@

9-11

PC

Memoria

de

programa

8

Registros

Especiales

IR

Decodif

5

PA0,PA1

2

2

2

FSR<4:0>

9

5

5

2

STATUS

PCL

FSR

RA0,RA1

7

@

Registros

Propósito

General

8

8

8

W

A10 A9

A8

A7-A0

000h

2

Página#0

00

01

1FFh

200h

Página#1

3FFh

400h

DEC

10

3

11

Z,C,DC

12

PCL

SRAM

9-11

1

PC

2

9

Pila

Nivel1

Nivel2

2

STATUS

STATUS<6:5>

=PA1,PA0

•33 Instrucciones

•12-bit de palabra de instrucción

•ROM/EPROM desde 512 a 2048 palabras

•Hasta 4 páginas (512x12bits) de memoria de programa

•8-bit de datos

•RAM desde 25 a 73 bytes

•Hasta 4 bancos (32x8bits) de 32 registros

•El PC (9 a 11-bits) se obtiene de concatenar el PCL con

los bits PA1,PA0 del STATUS y el bit A8

•Los bits A10-A8 se actualizan al realizar un RESET o

ejecutar instrucciones de saltos (goto,call) o de

modificación del PCL

•Hasta 4 páginas de 512x12 bits

Página#2

5FFh

600h

Página#3

•Comportamiento de A8:

•RESET coloca A8=1

•La instrucción goto modifica el PCL y A8

•La instrucción de salto call o una escritura a PCL

limpia A8=0. Las subrutinas llamadas por call se

deben situar en las primeras 256 palabras de página

7FFh

8

2

A10 A9

(*)9 a 11 bits de bus de @ para memoria de programa, dependiendo del µC

8

A8

A7-A0

PC

PCL

0

2

A10 A9

A8

<7:0>

IR call

STATUS

9

STATUS<6:5>

=PA1,PA0

8

<8:0>

ALU

IR goto

STATUS

STATUS<6:5>

=PA1,PA0

3

8

A7-A0

PC

PCL

2. Memoria de Datos

•Los registros se encuentran organizados hasta en 4

bancos de 32 registros (bytes) cada uno

•Dos tipos de registro: Registros especiales (SFR) y de

propósito general (GPR)

•La selección del banco se hace con RA1,RA0 del FSR

•Los 16 primeros registros (0x00 a 0x0F) sólo se

encuentran en el Banco 0, y no son usados RA1,RA0

durante la selección a estos. Contienen los registros

especiales (PCL,FSR,STATUS,INDF,TMR0,PORTA...)

•La cantidad máxima de registros de propósito general

es 72 ó 73 (si no existe PORTC)

5

FSR<4:0>

FSR<6:5>=RA1,RA0

2

3

00h

01h

02h

03h

04h

05h

06h

07h

111

101

110

100

011

001

010

000

DEC

08h

GPR

0Fh

10h

1

5

0

2Fh

30h

4Fh

50h

6Fh

70h

D/I

Registros de propósito general(GPR)

1Fh

3Fh

Banco 0

00

Banco 1

01

5Fh

Banco 2

10

7Fh

Banco 3

11

Nota 1: Registro no real

Nota 2: Sólo en dispositivos con PORTC (PIC16C55/C57)

RA1,RA0

5

IR

20h

40h

60h

INDF1

TMR0

PCL

STATUS

FSR

Estas direcciones se

PORTA

mapean en el Banco 0

PORTB

PORTC2

<4>

•Cambio de página con A10-A9:

•Cambiar PA1, PA0 y ejecutar un salto goto, call

o escritura a PCL

bsf STATUS,PA1 ;PA1=1

bcf STATUS,PA0 ;PA0=0

movlw 0x5F

;W=0x5F

movwf PCL

;PCL=W=>Salto a 0x45F

•Ejecución de la última instrucción de una página. No

cambia PA1,PA0. Un salto goto, call o escritura

a PCL (sin modificar PA1,PA0) devolvería el PC a

la página anterior

nop

;instrucc en 0x3FF

nop

;instrucc en 0x400

goto 0x05F

;Salto a 0x25F

•RESET coloca A10=A9=A8=1, PCL=$FF y

PA1=PA0=0.

(El vector de reset se situa en la última palabra de

memoria de programa del µC, y la selección de

página apunta a Página#0)

•0x1FF para 512 palabras (PIC16C56 )

•0x3FF para 1024 palabras (PIC16C57 )

•0x7FF para 2048 palabras (PIC16C58 )

org 0x1FF

;ó 0x3FF,0x7FF

goto 0x0

;vector reset a 0x0

1

0

0

0

1

0

1

1

8

1

1

1

IR

W

ROM/EPROM

E2PROM/FLASH

@

9-13

PC

Memoria

de

programa

9-13

Pila

Nivel1

Nivel2

SRAM

Registros

Especiales

Nivel8

5

PCLATH

PCL

8

FSR

IRP,RP1,RP0

STATUS

FSR<7>

3

8

1

14

IR

Decodif

9-13

11

2

2

7

7

9

7

@

Registros

Propósito

General

8

8

8

W

8

3

ALU

8

(*)9 a 13 bits de bus de @ para memoria de programa, dependiendo del µC

3

Z,C,DC

•Direccionamiento Directo: Los 5 LSBs de la

palabra de instrucción seleccionan el registro y

RA1,RA0 del FSR seleccionan el banco

bsf FSR,6

;RA1=1

bcf FSR,5

;RA0=0

movwf 0x10

;Registro 0x50=W

movwf 0x26

;Equivale a movwf PORTB

•Direccionamiento Indirecto: Se usa un acceso al

registro no real INDF (0x00), accediéndose al registro

apuntado por FSR

movlw 0x10

movwf FSR

;FSR=0x10

b0 clrf INDF

;(FSR)=0; Dir indirecto

incf FSR,F

;FSR++

btfss FSR,5 ;Si FSR<0x20

goto b0

; Nueva iteración bucle

•14-bit de palabra de instrucción

•Memoria de programa desde 512 a 8192 palabras

•Hasta 4 páginas (2048x14bits) de memoria de programa

•8-bit de datos

•RAM desde 80 a 368 bytes

•Hasta 4 bancos (128x8bits) de 128 registros

2

1

GAMA MEDIA (PIC16CXXX)

ARQUITECTURA

BÁSICA

•35 Instrucciones

FSR<6:0>

•Tipos de direccionamiento: Inmediato, Directo, Indirecto

•Direccionamiento Inmediato: Los 8 LSBs de la

palabra de instrucción contiene el dato, que es

cargado a W

movlw 0x5F

;W=0x5F

PCH

IR goto o call

PCLATH

PC

PCL

PCH

A7-A0

5

A7-A0

3

8

2

8

11

0000h

13

Página#0

0000h

Memoria

de programa 1FFFh

00

•Comportamiento del PC:

•RESET coloca A12-A0 y PCLATH a 0, situando el

vector de reset en la primera posición (0x000)

org 0x0

goto 0x300

;vector reset a 0x0300

•La modificación del PCL actualiza PCH con los

5 LSBs del PCLATH. Selección lineal

<4:0>

PCLATH

PC

5

PCH

PCL

A12-A8

A7-A0

5

8

13

Memoria

de programa

movlw

movwf

movlw

movwf

11

2

A12-A8

PCL

A12-A8

<10:0>

•El PC (13-bits) se obtiene de la concatenación del PCL

con 5 bits A12-A8 (PCH)

•Los bits del PC se actualizan al realizar un RESET o

ejecutar instrucciones de saltos (goto,call) o de

modificación del PCL

PC

•En instrucciones de salto goto y call se obtienen

11 bits de la palabra de instrucción, actualizándose

PCL y PCH. PCLATH permite la selección paginada,

de hasta 4 páginas de 2048x14 bits

<4:3>

1. Memoria de Programa

0000h

1FFFh

0x1A

PCLATH

0x40

PCL

;Salto a 0x1A40

01

07FFh

0800h

Página#1

0FFFh

1000h

DEC

10

11

Página#2

17FFh

1800h

Página#3

1FFFh

bsf PCLATCH,3

bcf PCLATCH,4

call 0x45A

;PCLATH<3>=1

;PCLATH<4>=0

;Subrutina en 0x0C5A

•Ejecución de la última instrucción de una página. No

cambia PCLATH. Un salto goto, call o escritura

a PCL (sin modificar PCLATH) devolvería el PC a

la página anterior

nop

;instrucc en 0x0FFF

nop

;instrucc en 0x1000

goto 0x45A

;Salto a 0x0C5A

2. Memoria de Datos

•Los registros se encuentran organizados hasta en 4

bancos de 128 registros (bytes) cada uno

•Dos tipos de registro: Registros especiales (SFR) y de

propósito general (GPR)

•La selección del banco se hace dependiendo del tipo de

direccionamiento directo o inmediato, con RP1,RP0 del

STATUS, o con IRP del STATUS y el MSB del FSR

•Hay registros SFR (INDF,PCL,STATUS,FSR,PCLATH...)

mapeados en todos los bancos

•En algunos dispositivos los últimos 16 GPRs de cada

banco están mapeados en el Banco 0 (Common RAM)

8

FSR<7:0>

FSR<6:0>

FSR<7>

7

STATUS<7>= IRP

2

2

STATUS<6:5>=RP1,RP0

STATUS<7:5>

0

1

D/I

2

11

01

10

00

DEC

3

00h

01h

02h

03h

04h

05h

06h

80h INDF

INDF1

TMR0

OPTION

PCL

PCL

STATUS

STATUS

FSR

FSR

PORTA

TRISA

PORTB

TRISB

100h

INDF

180h

INDF

TMR0

PCL

STATUS

FSR

OPTION

PCL

STATUS

FSR

PORTB

TRISB

0

9Fh

A0h

11Fh

120h

19Fh

1A0h

F0h

170h

1F0h

FFh

17Fh

1FFh

Registros de propósito general(GPR)

6Fh

70h

7

IR

7

Otros SFR y GPR

1Fh

20h

1

D/I

Mapeados en el Banco 02

7Fh

Banco 0

00

Banco 1

01

Banco 0,1

0

Banco 2

10

Banco 3

11

Banco 2,3

1

RP1,RP0 (direcc. directo)

IRP (direcc. indirecto)

Nota 1: Registro no real

Nota 2: Algunos dispositivos mapean todos estos registros en el Banco 0 (common RAM)

•Tipos de direccionamiento: Inmediato, Directo, Indirecto

•Direccionamiento Inmediato: Los 8 LSBs de la

palabra de instrucción contiene el dato, que es

cargado a W

movlw 0x5F

;W=0x5F

1

1

0

0

X

X

0

1

0

1

1

8

1

1

1

IR

W

•Direccionamiento Directo: Los 7 LSBs de la

palabra de instrucción seleccionan el registro y

RP1,RP0 del STATUS seleccionan el banco

bsf STATUS,RP0

;RP0=1

bcf STATUS,RP1

;RP1=0

movwf 0x3F

;Registro 0xBF=W

movwf PORTB

;Registro TRISB=W

•Direccionamiento Indirecto: Se usa un acceso al

registro no real INDF (0x00), accediéndose al registro

apuntado por FSR<6:0>, y seleccionando el banco

con IRP del STATUS y FSR<7>

bsf STATUS,IRP

;IRP=1

movlw 0xA0

movwf FSR

;FSR=0xA0, FSR’=0x1A0

b0 clrf INDF

;(FSR’)=0; Dir indirecto

incf FSR,F

;FSR’++

btfss FSR,6 ;Si FSR’<0x1C0

goto b0

; Nueva iteración bucle

INSTRUCCIONES

PIC16C5X/16CXXX

PIC16C5X:

Aritméticas

33 Instrucciones (2 especif.

), 12-bit Program Word

PIC16CXXX: 35 Instrucciones (4 especif.

), 14-bit Program Word

31 Instrucciones Comunes

Manipulación bits individuales:

Ciclos

STATUS

bcf f,b

BIT ‘b’ CLEAR of ‘f’

1

-

bsf f,b

BIT ‘b’ SET of ‘f’

1

-

CLEAR W

1

CLEAR ‘f’

1

Z

movlw k

MOVE LITERAL ‘k’ TO W

1

-

movf

f,d1

f,d1

MOVE W TO ‘f’

MOVE ‘f’ TO ‘d’

1

Z

decf f,d1

DECREMENT ‘f’ PUTTING TO ‘d’

1

Z

comf f,d1

COMPLEMENT ‘f’ PUTTING TO ‘d’

1

Z

addlw k

ADD LITERAL ‘k’ TO W

1

C,DC,Z

addwf f,d1

ADD W AND ‘f’ PUTTING TO ‘d’

1

C,DC,Z

sublw k

SUBSTRACT W FROM LITERAL ‘k’

1

C,DC,Z

subwf f,d1

SUBSTRACT W FROM ‘f’ PUT TO ‘d’

1

C,DC,Z

andlw k

AND LITERAL ‘k’ TO W

1

Z

andwf f,d1

AND W WITH ‘f’ PUTTING TO ‘d’

1

Z

iorlw k

INCL-OR LITERAL ‘k’ TO W

1

Z

iorwf f,d1

INCL-OR W WITH ‘f’ PUTTING TO ‘d’

1

Z

xorlw k

EXCL-OR LITERAL ‘k’ TO W

1

Z

xorwf f,d1

EXCL-OR W WITH ‘f’ PUTTING TO ‘d’

1

Z

Z

clrf f

movwf f

INCREMENT ‘f’ PUTTING TO ‘d’

Lógicas:

Transferencia de datos:

clrw

incf f,d1

1

1

Z

SWAP NIBBLES OF ‘f’ PUTTING TO ‘d’

1

-

tris f2

MOVE W TO TRIS’f’

1

-

Rotaciones:

option

MOVE W TO OPTION

1

-

rlf f,d1

ROTATE LEFT ‘f’ PUTTING TO ‘d’

1

C

rrf f,d1

ROTATE RIGHT ‘f’ PUTTING TO ‘d’

1

C

swapf

Nota1: d={0,1}; W=0⇒W, F=1⇒‘f’

Nota2: f={5,6,7}; PORTA=5⇒TRISA, PORTB=6⇒TRISB,

PORTC=7⇒TRISC

Saltos:

goto label

GOTO INSTRUCCTION @’label’

2

-

PIC16C5X:

STATUS

(03h,23h,43h,83h)

call label

CALL SUBRUTINE @’label’

2

-

return

RETURN FROM SUBRUTINE

2

-

retlw k

RETURN SUBR., MOVE LITERAL ‘k’ TO W

2

-

retfie

RETURN FROM INTERRUPT, RE-ENABLE

2

-

btfsc f,b3

BIT ‘b’ TEST OF ‘f’, SKIP IF CLEAR

1/24

-

btfss f,b3

BIT ‘b’ TEST OF ‘f’, SKIP IF SET

1/24

-

decfsz f,d1

DECREMENT ‘f’ PUTTING TO ‘d’,

SKIP IF ZERO

1/24

-

INCREMENT ‘f’ PUTTING TO ‘d’,

SKIP IF ZERO

1/24

-

incfsz

Nota3: b=[0,7]

Nota4: 1 SI NO SALTA, 2 SI SALTA

Otras:

clrwdt

CLEAR WATCHDOG TIMER

1

sleep

SLEEP MODE

1

nop

NO OPERATION

1

TO=1

PD=1

TO=1

PD=0

-

R/W

R/W

R

PA21 PA1 PA0 TO

R

R/W

R/W

R/W

PD

Z

DC

C

R

R/W

R/W

R/W

PD

Z

DC

C

usado. No se recomienda usarlo para futura compatibilidad

PIC16CXXX:

STATUS

(03h, 83h,103h,183h)

2 Algunos

Saltos condicionales:

f,d1

1 No

R/W

R/W

R/W

R/W

R

IRP2 RP11 RP0 TO

dispositivos no usan estos bits: deben mantenerse a 0

Z: Flag de Zero

C: Flag de Carry/Borrow

DC: Flag de Digit Carry/Borrow (4-bit LSBs)

A

equ 0x20

...

movlw 0x25

xorwf A,W

btfsc STATUS,Z

goto ZERO

movlw 0x10

subwf A,W

btfss STATUS,C

goto MENOR0x10

movlw 0xCF

addwf A,F

btfsc STATUS,C

goto DESBORDE

...

;GPR 0x20 contiene A

;W=0x25

;W=A xor W

;Si A=0x25 => Z=1

;

salta a ZERO

;W=0x10

;W=A-W

;Si A-0x10<0 => C=0

; salta a MENOR0x10

;W=0xCF

;A=A+0xCF

;Si A+0xCF>0xFF => C=1

; salta a DESBORDE

CONVERSIÓN DE CÓDIGO

PIC16C5X/16CXXX

•Los dispositivos de gama baja sólo poseen TIMER0,

WDT, y puertos PORTA,PORTB,PORTC

•El PORTB de la gama media permite pull-up interno

•Los registros OPTION,TRISA,TRISB,TRISC están

direccionados en los bancos de registros en la gama

media, pero no en la baja

•2 Niveles de pila en gama baja, 8 en gama media

•La gama media incorpora nuevas instrucciones

•Vector de RESET en 0x0 en gama media, y en la última

palabra de instrucción en la gama baja

•No permiten interrupciones en gama baja

•Reubicar adecuadamente las variables almacenadas

en los GPR

•Revisar el uso del registro OPTION

•Revisar el uso de los registros de selección de bancos

de registros y paginación de memoria de programa:

STATUS,FSR,PCL,PCLATH,INDF

•Es recomendable el uso de las directivas del PASM

pagesel en instrucciones de salto call o goto, y

banksel en instrucciones con direccionamiento directo

•Gama baja (PIC16C5X):

•pagesel: bsf y bcf de STATUS<6:5>=PA1,PA0

•banksel: bsf y bcf de FSR<6:5>=RA1,RA0

DATO1

DATO2

INIT

SUBR1

INST2

equ 0x10

equ 0x50

org 0

banksel DATO1

clrf DATO1

banksel DATO2

clrf DATO2

pagesel SUBR1

call SUBR1

pagesel INST2

goto INST2

org 0x0FF

retlw 0

org 0x300

;GPR en Banco0

;GPR en Banco2

Direcc. Directo/Indirecto

;Ensambla bcf 0x4,0x5 y bcf 0x4,0x6

;Ensambla bcf 0x4,0x5 y bsf 0x4,0x6

;Ensambla bcf 0x3,0x5 y bcf 0x3,0x6

;Ensambla bsf 0x3,0x5 y bcf 0x3,0x6

;Subrutina en Página0

;Intrucciones en Página1

Optimizable!

•Gama media (PIC16CXXX):

•pagesel: bsf y bcf de PCLATH<4:3>

•banksel: bsf y bcf de STATUS<6:5>=RP1,RP0

DATO1

DATO2

INIT

SUBR1

INST2

equ 0xA0

equ 0x120

org 0

banksel DATO1

clrf DATO1

banksel DATO2

clrf DATO2

pagesel SUBR1

call SUBR1

pagesel INST2

goto INST2

org 0x1000

return

org 0x1800

;GPR en Banco1

;GPR en Banco2

Sólo direcc. Directo

;Ensambla bsf 0x3,0x5 y bcf 0x3,0x6

;Ensambla bcf 0x3,0x5 y bsf 0x3,0x6

;Ensambla bcf 0xA,0x3 y bsf 0xA,0x4

;Ensambla bsf 0xA,0x3 y bsf 0xA,0x4

;Subrutina en Página2

;Intrucciones en Página3

Optimizable!